当带电的人用手指触摸组件时,就会产生人体模型 (HBM)。这是古老的 ESD 测试,初是为采矿业开发的,它模拟电荷从手指到

集成电路引脚的传输,而其他引脚接地。

近的数据表明 HBM 很少模拟实际的 ESD 事件。一代的封装样式通常太小,人们无法用手指操作,而且大多数大型元件的制造过程都采用自动化设备,因此人们几乎无法接触元件。

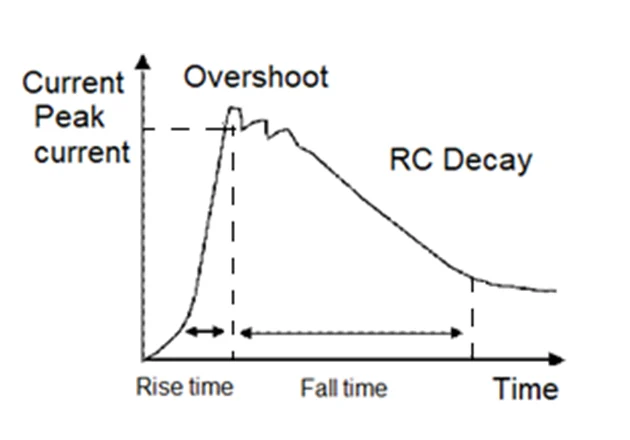

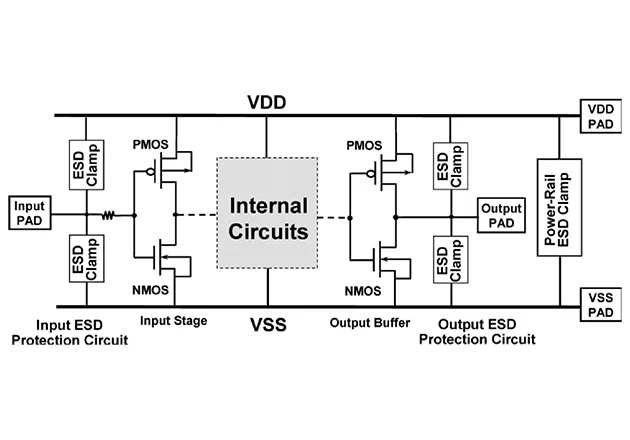

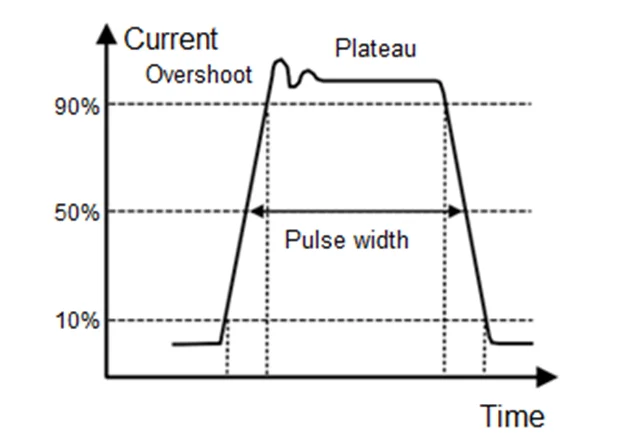

图 1 显示了 HBM 脉冲波形。

HBM 脉冲波形示例

机器模型脉冲

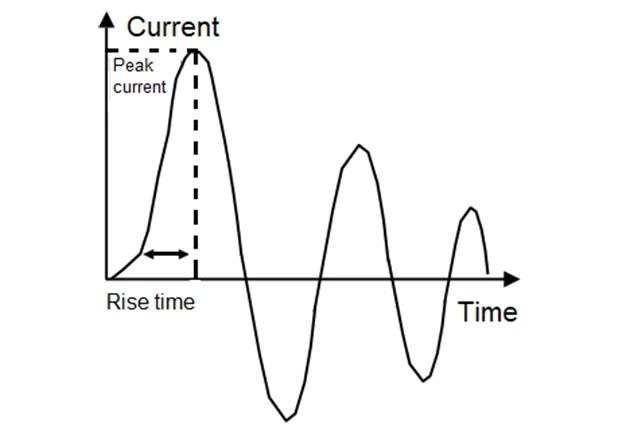

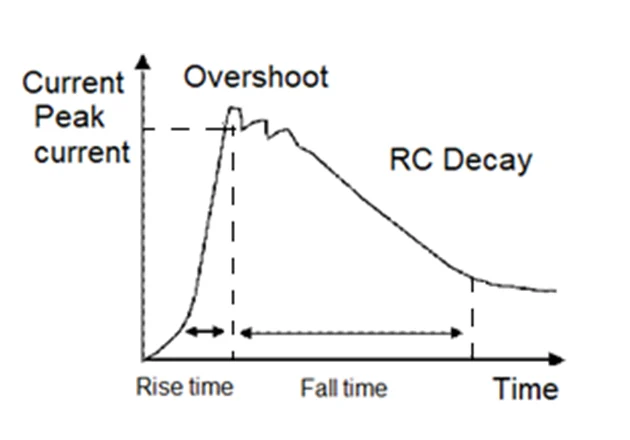

机器模型 (MM) 脉冲旨在模拟带电金属物体接触 IC 引脚时的 ESD 事件。图 2 显示了 MM 脉冲波形。

MM脉冲波形示例

图 2. MM 脉冲波形示例。图片基于 SH Voldman,2012 年。

在 HBM 和 MM 模型中,电荷转移到元件。

带电设备模型

当带电设备接触接地物体时,就会出现带电设备模型 (CDM)。在这种测试方法中,元件是电荷源,它通过接地体放电。

CDM 模型在组件级别复制内部和客户 IC 故障。它决定了 IC 在 ESD 事件中的脆弱性,即带电封装通过接地金属物体放电。目前,此类放电事件是现代电路中 ESD 故障的主要原因。

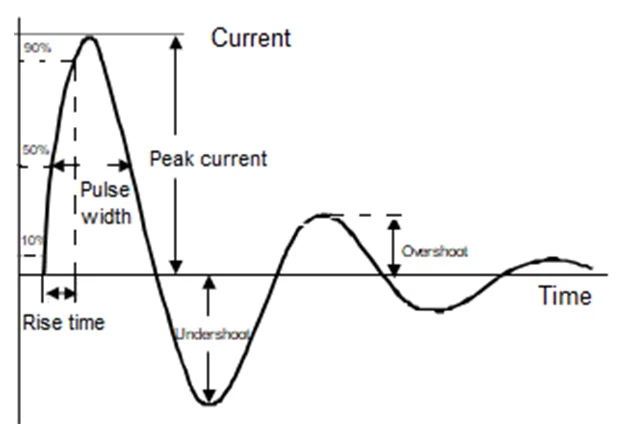

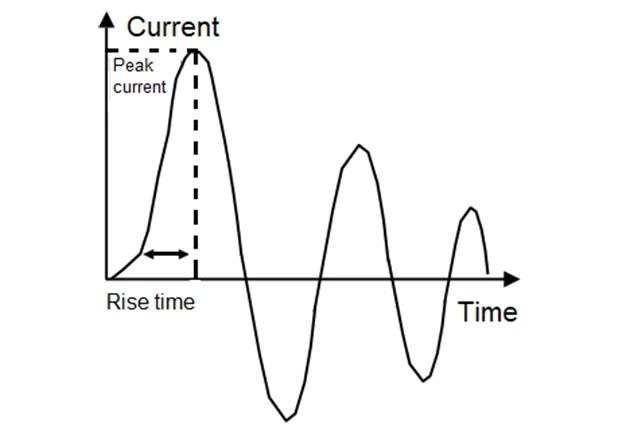

图 3 显示了 CDM 电流波形。

CDM 电流波形示例

图 3. CDM 电流波形示例。

传输线脉冲

在传输线脉冲测试 (TLP) 中,电压源对传输线

电缆充电,然后系统向被测设备释放一系列类似 ESD 的脉冲。它评估在 ESD 应力下运行的器件性能。

该测试方法是 HBM 方法的等效或替代方法,并且还可以测量或表征 ESD 性能。

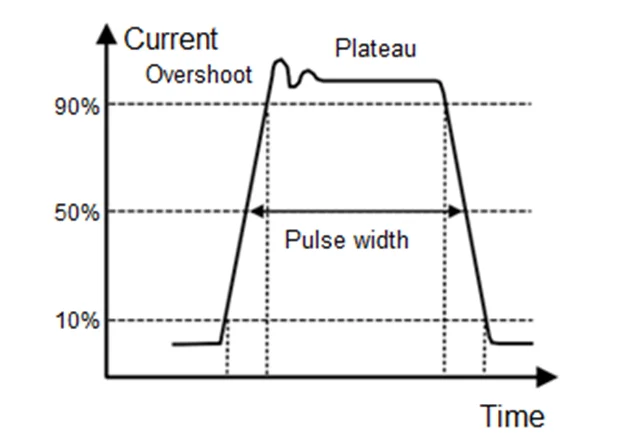

图 4 显示了 TLP 脉冲波形。

TLP 脉冲波形示例

图 4. TLP 脉冲波形示例.

常见的 ESD 故障

ESD 故障是灾难性的,可能导致 IC 芯片立即发生故障。

结点和氧化物很容易受到损坏。 ESD 引起故障的基本机制是:

硅中的结烧坏:这是常见的 HBM 故障机制 - ESD 瞬态能量的注入可以驱动结击穿。

氧化物击穿:当氧化层上施加高电压(高压过应力)导致电介质击穿时,就会出现另一类主要的 ESD 损坏。当电介质击穿时,它开始传导电流。电流产生的热量会产生热点并熔化电介质、硅和其他材料。

金属化烧毁:这会在互连路径中产生开口。当温度(I?R 热量)达到材料的熔点时,就会发生这种情况。它通常是继发效应,发生在结或氧化物失效之后。

片上 ESD 保护器件

片上 ESD 保护结构通过提供到接地总线/电源轨的安全 ESD 放电路径来保护电路的输入、输出和电源引脚。这些保护结构在正常系统运行期间关闭,但在出现 ESD 事件时迅速开启,将浪涌电流释放到地面。

在此事件期间,保护电路将引脚钳位至低电压。放电后它们返回截止状态。 ESD 事件不得损坏器件。

当由于技术限制而无法实现片上保护时,位于电缆、连接器、陶瓷载体或电路板中的片外保护解决方案非常有用。在某些情况下,采用优化方法设计的定制解决方案可能会降低成本。

ESD保护器件应符合四个特性:

鲁棒性

效力

速度

透明度

除了稳健和有效之外,ESD 保护电路还应该足够快,以便在受保护的主电路之前开启。此外,保护电路必须是透明的,并且不能改变主电路的性能

ESD 电路的构建模块

构建保护夹有不同的技术。他们的选择取决于技术和设计限制。常用作 ESD 保护器件的三种器件是:

二极管 栅极接地 N 沟道 MOSFET

可控硅 二极管

二极管结构简单,正向偏置时可满足低压 ESD 应用的要求。在这种条件下工作,它们是的 ESD 保护元件之一——具有低导通电压、低导通电阻,并可处理高 ESD 电流。

在反向偏压下,二极管表现出高导通电压、高导通电阻和低电流处理能力,使其成为不能令人满意的ESD保护器件。缺点是漏电流增加。

栅极接地 N 沟道 MOSFET

接地栅极 n 沟道 MOSFET (GGNMOS) 通常用于保护基于 CMOS 的设计免受 ESD 事件的影响。这些器件的结构和工作原理与普通MOS相似;然而,它们采用不同的布局技术来优化 ESD 保护器件的性能。

GGNMOS 器件可以在主动或快速恢复模式下运行。在主动操作模式下,它充当标准 NMOS 器件。骤回效应允许在低电压下通过大电流——高压 ESD 事件会触发电流;然而,当 ESD 保护器件上的电压较低时,该电流会继续流动。 Snapback 是常见的操作模式。缺点是鲁棒性低。

可控硅

可控硅整流器 (SCR) 因其双极传导机制而具有高鲁棒性,是有效的 ESD 保护器件。

其缺点是容易闩锁,即 ESD 事件结束后电流传导。通过正确的设计,它们可以在可容忍的闩锁风险下提供出色的 ESD 性能。

请注意,虽然二极管是非快速恢复型器件,但 SCR 和 GGNMOS 具有快速恢复特性。

片上 ESD 保护策略

ESD 保护策略包括钳位过应力电压并使用片上保护结构为 ESD 电流提供放电路径。

片上 ESD 保护电路可保护输入、输出和电源焊盘免受 ESD 事件的影响。

这些保护元件在受保护设备的正常运行期间保持无源状态,并且仅在存在 ESD 脉冲时通过检测上升时间和过压来激活。当检测到 ESD 脉冲时,保护电路将为 ESD 电流提供安全的放电路径。

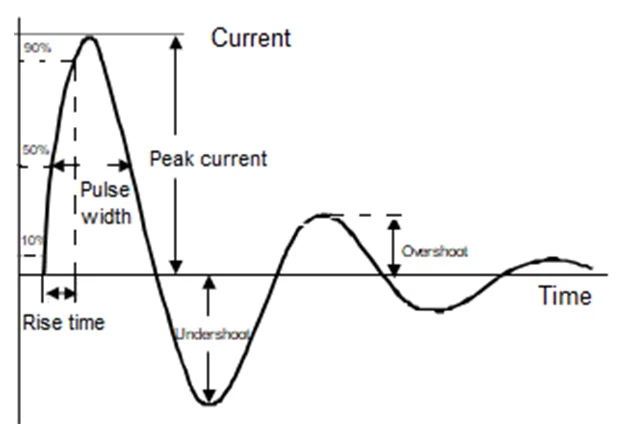

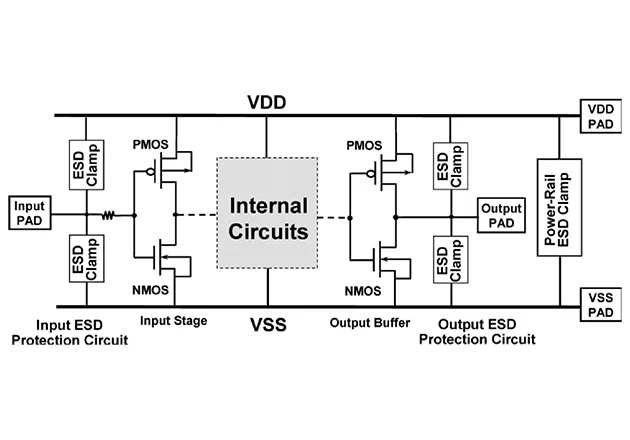

图 5 显示了一种典型设计,其中 ESD 保护电路添加到输入、输出和电源

端子 片上ESD保护电路。

图 5. 片上 ESD 保护电路。图片来自 MD Ker,1999。

该网络由以下保护组件组成:

输入焊盘接地 (Vss)

输入焊盘至电源轨 (Vdd)

输出焊盘接地 (Vss)

输出焊盘至电源轨 (Vdd)

电源轨 (Vdd) 到接地 (Vss)

ESD 保护技术适用于所有重要工艺,包括 CMOS、BiCMOS 和 III-V 化合物。