带有 GaN 和 SiC 元件的转换器的高开关频率对用于控制系统硬件在环测试的实时模拟器提出了挑战。

当功率半导体的开关频率超过 100 kHz 时,仅将模拟步骤减少到略低于 1 微秒是不够的。此外,必须对栅极信号进行过采样,并在一个模拟步骤中取平均值。这种方法在基于 CPU 和 FPGA 的连续导通模式下硬开关逆变器模拟器上效果很好。然而,对于谐振转换器或双有源桥,这种方法就不准确了,因为电流经常改变方向或进入不连续导通模式。需要几纳秒的非常小的模拟步骤才能准确模拟此类转换器拓扑,这只能通过 FPGA 上的特殊算法来实现。

电路仿真可帮助设计工程师在构建原型之前预测和分析电气设备或系统的行为。仿真允许工程师为设备创建模型或虚拟原型,并在正常和故障操作条件下执行测试。由于可以快速修改模型,因此仿真可以加速开发过程并缩短新产品的上市时间。仿真在早期设计阶段以及测试将成为更大系统一部分的现有设备的正确操作方面很有用。在电力电子领域,越来越多地使用数字实时模拟器来测试和验证没有实际电源电路的控制设备。代表受控系统的实际电源电路被模拟器上计算的适当动态模型所取代。由于控制设备体现为电子硬件,因此这种用例称为控制器硬件在环 (HIL) 测试。

HIL 仿真允许在安全的环境中测试控制硬件和软件。在实时仿真电力电子时,电路的微小时间常数和快速动态会带来挑战。为了使被测控制设备像连接到真实电力电路时一样运行,实时模拟器必须具有高保真度和低环回延迟。这意味着仿真结果必须准确地表示电路中的实际电压和电流,并且需要在模拟器输入端的信号发生变化后几微秒内计算和输出它们。

随着 GaN 和 SiC MOSFET 等宽带隙器件的出现,电源转换器的开关频率已提升至 MHz 范围。这对实时模拟器来说是一个挑战,因为它们的模拟时间步长通常介于 100 ns 和几微秒之间。然而,为了以足够的精度捕获 PWM 信号,必须以至少 100 倍于开关频率的速率对其进行采样。如果开关频率为 1 MHz,则这意味着采样间隔为 10 ns 或更短。

两种有助于实现如此小采样间隔的实时仿真的技术是子周期平均法和 Nanostep。虽然子周期平均法可以应用于主要以连续导通模式 (CCM) 运行的多种逆变器,但 Nanostep 求解器非常适合模拟高频和谐振 DC/DC 转换器拓扑,例如双有源桥 (DAB) 和 LLC。

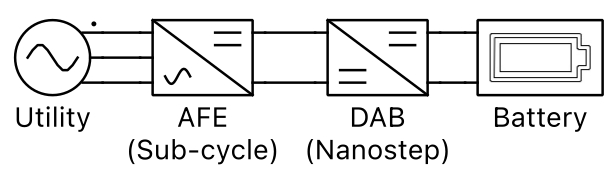

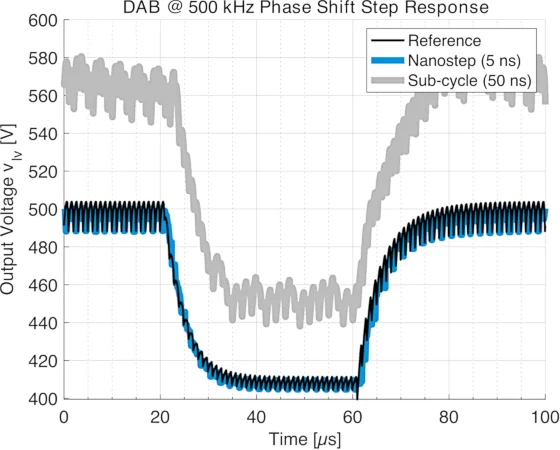

常见的电源架构结合了 AC/DC 转换器和高频 DC/DC 转换器。一个典型的例子是电动汽车充电器,它由三相有源前端 (AFE) 和 DAB 组成,如图 1 所示。在这个基于宽带隙技术的 10 kW 充电器中,AFE 在 140 kHz 的 CCM 中运行,而 DAB 则在 500 kHz 下切换。

随着 RT Box 2 和 3 即将推出固件升级,此类充电器电路可在 RT Box 内的 FPGA 结构上进行仿真。AFE 将使用子周期平均法进行仿真,而 DAB 则需要专用的 Nanostep 求解器。这种求解器技术组合可实现具有高开关频率的电源转换器的高精度实时仿真。

图 1. 带有有源前端 (AFE) 和双有源桥 (DAB) 的电动汽车充电器系统原理图。图片由Bodo's Power Systems提供 [PDF]

子周期平均

在电力电子应用中,许多逆变器-转换器系统(例如降压转换器、升压转换器、二极管整流器和电压源逆变器 (VSI))都可以通过一个或多个半桥实现。这些半桥由串联功率半导体组成,每个功率半导体可以是自然换向器件(例如二极管)、强制换向器件(例如 IGBT)或两者的组合。

在大多数应用中,半桥连接到直流侧的电容器或电压源。在正常运行下,可以假设直流电压 v dc为正偏置,否则二极管会使直流链路短路。在运行期间,相位端子切换到正或负直流链路电压或保持未连接状态。

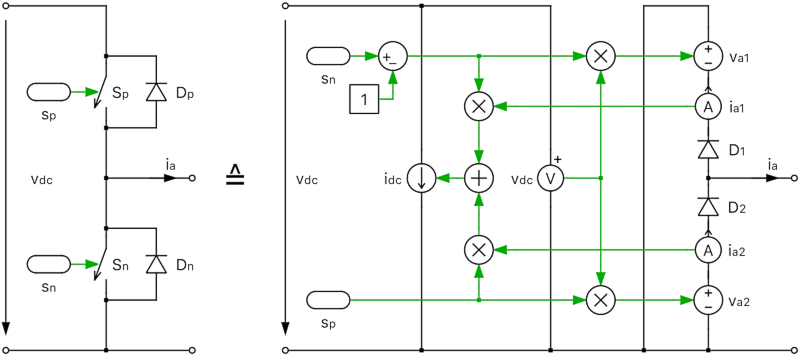

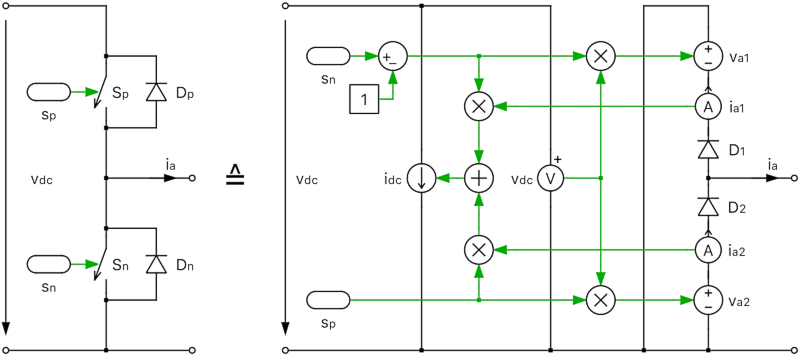

对于子周期平均,这种半桥采用两个串联二极管和多个受控电压和电流源的组合建模,以提高实时模拟的保真度。图 2 针对 VSI 半桥说明了这种建模方法。电压源 v a1和 v a2由开关信号 s p和 s n控制。它们将直流电压 v dc施加到相侧。同样,电流源 i dc由相同的开关信号控制,将相电流 i a1或 i a2施加到直流侧。

需要两个二极管来模拟自然换向和不连续导通模式 (DCM)。根据相电流的方向,下部或上部二极管将导通,从而施加相应的相电压和直流电。如果没有一个二极管导通,则半桥已进入 DCM,这意味着它为零。

图 2. VSI 半桥的子周期平均模型。图片由Bodo's Power Systems提供 [PDF]

子周期平均的关键优势在于开关信号不仅可以是代表器件导通状态(s = 1)和关断状态(s = 0)的二进制信号,还可以是代表器件在仿真步骤期间的相对导通时间或占空比的短期平均值(0 ≤ s ≤ 1)。这些平均值可以通过在每个 FPGA 时钟周期(通常短于 10 纳秒)对 PWM 信号进行采样来获得。即使开关频率很高且仿真步长比 FPGA 时钟周期大两个数量级,得到的相电流也基本上是准确的,因为平均信号的施加伏秒对应于原始 PWM 信号的伏秒。但是,并非所有开关谐波都能通过较大的仿真步长保留。如果步长太大,计算出的电压和电流可能会有严重误差。

子周期平均法的主要缺点是相电流过零导致的不准确性。由于相电流的方向在每个模拟步骤中仅确定,因此在电流过零或进入 DCM 的步骤中可能会应用稍微不正确的伏秒。虽然这种不准确性对于在 CCM 中运行且电流方向没有频繁变化的逆变器(例如并网 VSI)来说是可以接受的,但对于在高开关频率下运行的其他转换器(尤其是自然换向转换器)来说可能并非如此。

图 3 描绘了 EV 充电器示例中的三相 AFE 电路。具有 SiC MOSFET 的 AFE 以 140 kHz 切换,是用于验证子周期平均技术的基准模型。在此电路模型中,DAB 级的负载由等效电阻 R out表示。

图 3.带有 SiC MOSFET 的 AFE 电路。图片由Bodo's Power Systems 提供

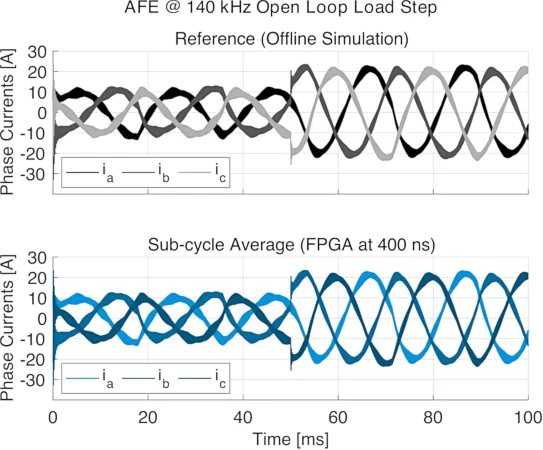

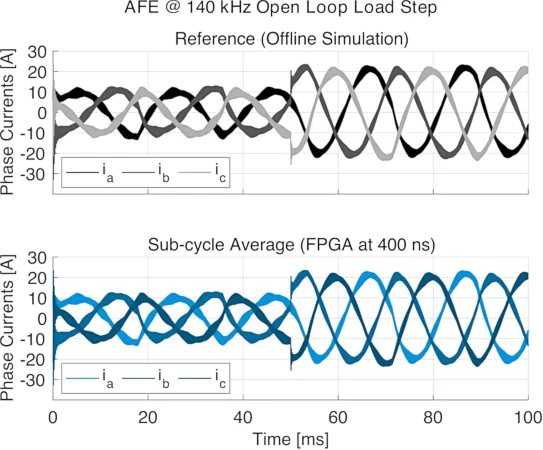

图 4 显示了从半载到满载的阶跃变化过程中 AFE 的输入电流。离线仿真使用可变步长求解器和理想开关在 PLECS 中生成参考结果。它们与使用 RT Box 进行实时仿真获得的波形进行了比较。400 ns 的模型步长对应于使用新的基于 FPGA 的子周期平均电路求解器在 RT Box 2 或 3 上可以实现的步长。MOSFET 的控制信号由开环控制器生成,以便直接比较两种不同的建模方法。

图 4. PLECS 离线仿真与 RT Box 实时仿真的对比。图片由Bodo's Power Systems提供

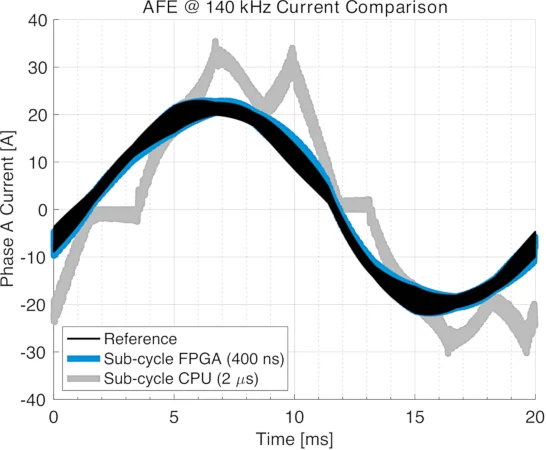

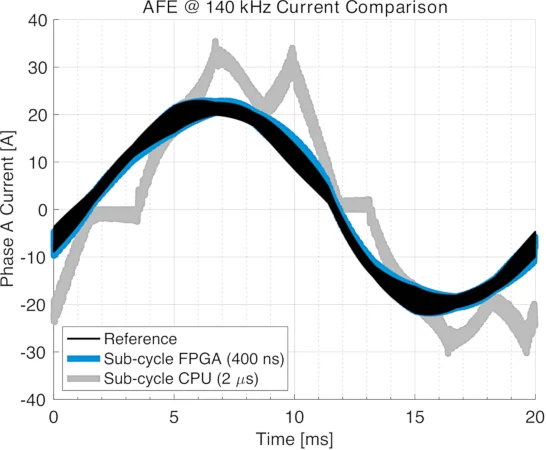

相电流的比较证明了子周期平均模型的准确性。图 5 显示了线路频率单个周期的 A 相交流电。基于 FPGA 的 400 ns 仿真与参考波形非常接近。但是,子周期平均方法需要较小的模型步长才能获得准确的解决方案。在步长为 2 μs 时,这代表在 RT Box 的 CPU 上计算子周期平均模型,电流波形表现出较大的误差。

该误差是由于对电流方向变化的检测延迟造成的,当 PWM 脉冲短于模拟的步长时,可能会出现这种情况。在图 2 中的模型中,平均电压 v a1和 v a2的峰值可能不足以使相电流直接从一个二极管(D 1和 D 2)换向到另一个二极管。相反,两个二极管可能会打开并将电流钳位为零。这种影响可以在图 5 中观察到,其中在步长为 2 μs 时,A 相电流在零交叉附近发生失真。B 相和 C 相中的相同行为通过中性电压的偏移表现为 A 相波形峰值附近的失真。

图 5.一个线路周期内的 A 相电流波形。图片由Bodo's Power Systems 提供

图 6 详细说明了相电流的方向如何从负变为正。尽管反复出现过零,但基于 FPGA 的仿真与参考值略有偏差。在 400 ns 步长下,求解器在一个开关周期内执行近 18 次,因此平均电压值通常接近瞬时电压。由开路二极管引起的电流偶尔被钳位到零,这是过渡性的,对结果的影响很小。相反,如果电压在 2 μs 的 CPU 模型步长上取平均值,则无法换向电流。

图 6. A 相电流波形的详细视图。图片由Bodo's Power Systems [PDF]提供

纳米级

对于相电流方向频繁变化的电力电子转换器,子周期平均法变得不准确。对于具有电感性交流链路的 DC/DC 转换器尤其如此,因为功率传输对电流和 PWM 信号之间的相移非常敏感。交流电的延迟过零检测会导致相当大的误差。这是因为正、负和零电流对应于由另一组微分方程控制的不同电路拓扑。

为了尽快检测零交叉,Plexim 开发了 Nanostep 求解器,该求解器将于今年晚些时候用于 RT Box。在 Nanostep 模拟中,电感电流和谐振电容器电压的值会随着每个 FPGA 时钟周期更新。由于计算新值需要一系列算术运算并需要多个时钟周期,因此所有可能拓扑的值都是并行计算的。拓扑的有效性取决于的门信号和电感电流的方向。改变方向或被钳位为零的电感电流代表限制某些拓扑有效性范围的边界条件。只有在计算完所有值后,才会根据边界条件决定必须应用哪种拓扑。

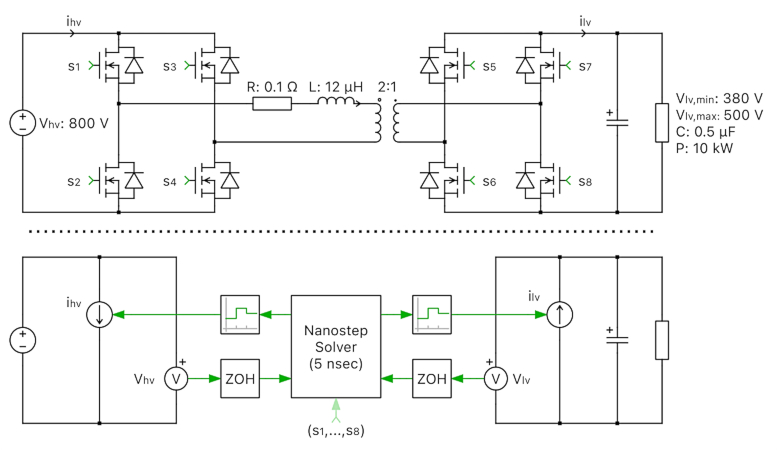

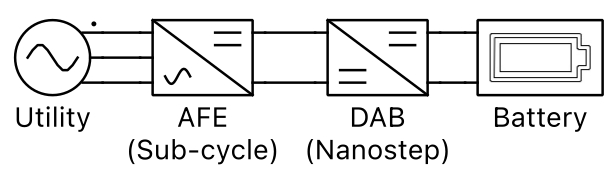

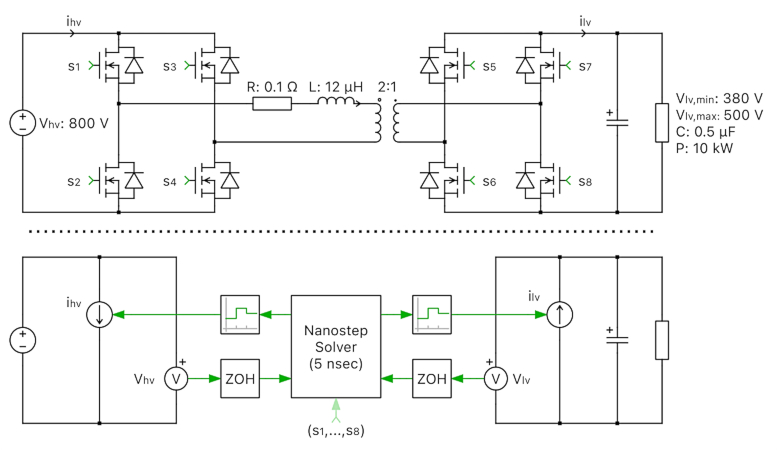

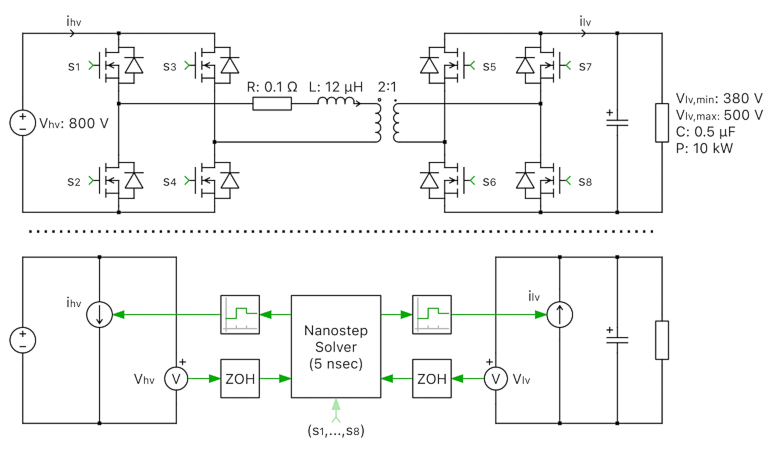

图 7 显示了 EV 充电器 DAB 级的纳米级模型。转换器开关频率为 500 kHz,死区时间为 120 ns。初级和次级开关调制之间的相移控制功率传输。

Nanostep 求解器集成了转换器的开关网络和储能元件。栅极信号采样、电感电流积分和电流过零检测发生在 5 纳秒或更短的 FPGA 时钟周期内。Nanostep 求解器的采样率为 5 纳秒,可以检测到 500 kHz 开关频率下低至 0.5% 的相移。

图 7.双有源桥与外部电路接口的纳米级模型。图片由Bodo's Power Systems 提供 [PDF]

感兴趣的外部电路动态,即输入和输出电容器电压 v HV和 v LV,通常比内部开关网络的动态慢得多。使用在 FPGA 或 CPU 上实现的具有大得多的模型步长的通用求解器来模拟外部电路。典型的步长范围从几百纳秒到几微秒。在此应用中,AFE 的 400 纳秒模型步长用作与 Nanostep 求解器的通信间隔。Nanostep 求解器的输入是转换器的端电压,在模型步长处采样。Nanostep 求解器在一个模型步长??上对转换器的输入和输出电流求平均值,以正确计算注入外部网络的电流 i HV和 i LV 。

Nanostep 求解器的局限性在于与外部电路的接口,该接口在较大的模型步骤中求解。转换器端子处的电压在模型步骤中假定为恒定的。模型步骤还决定了模拟硬件输出的更新率,从而影响环回延迟。,内部故障条件未模拟,但当 5 ns 采样间隔内的任何门信号导致转换器的直流端子短路时,可以检测到内部故障条件。

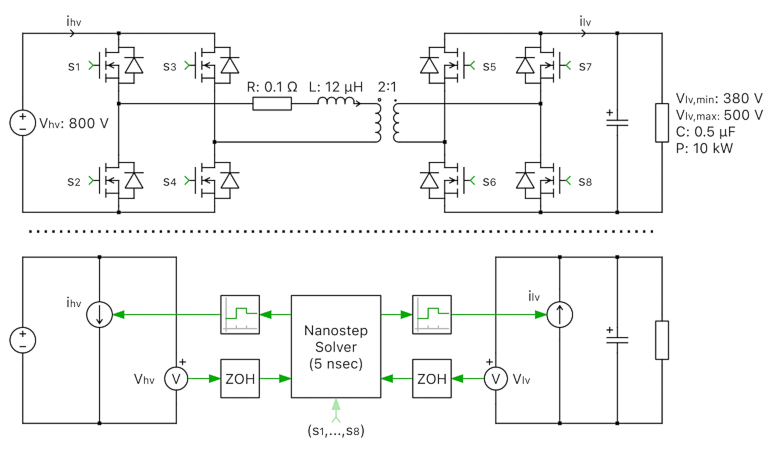

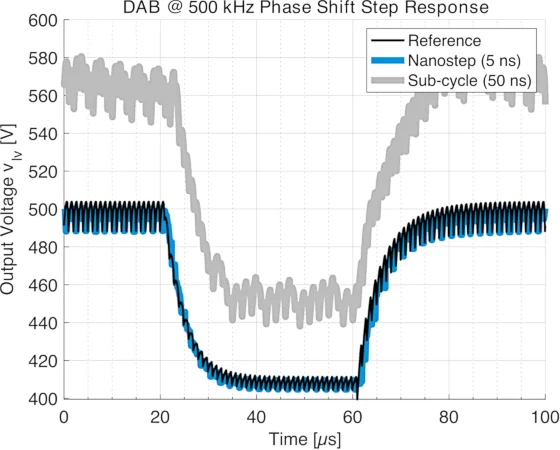

图 8 将 Nanostep 求解器的精度与具有理想开关和假设的子周期平均模型(步长为 50 ns)的离线 PLECS 模拟进行了基准测试。50 ns 模型无法在 RT Box 上实现。转换器以 0.1T sw或 200 ns 的恒定相移运行。对于较大的步长,在 50 ns 间隔内对栅极信号进行平均会导致输出电流出现误差。死区时间间隔内电流的零交叉也会被遗漏。比较模型步骤内的平均电流,Nanostep 求解器和参考解决方案的精度在 1% 以内,而步长为 50 ns 的模型的误差为 40%。

图 8. 使用 5 ns 和 50 ns 步长模拟 DAB 的输出电流。图片由Bodo's Power Systems提供

使用 5 ns Nanostep 求解器计算的平均值作为外部电路的接口可保留转换器输入和输出端口的大信号动态。图 9 显示了具有恒定电阻负载的调制器相位阶跃变化的模型响应。转换器在额定功率下以 500 V 输出开始,由于相移减小而步进到较低的功率水平,然后返回到初始相位。Nanostep 求解器的电压动态与 400 ns 模型步骤相结合,与参考解决方案非常接近。额外的相位滞后是由于 Nanostep 求解器的电流平均和模型步骤持续时间造成的。子周期平均模型不可用,因为它会提供过多的功率,因此输出电压永远不会达到预期的稳态输出电压。

图 9. 500 kHz DAB 对调制器相移阶跃变化的响应。图片由Bodo's Power Systems 提供