对于I2C系统,速度和功耗都取决于上拉电阻的值:上拉电阻的值应该足够低,以确保

总线电容的快速充电。

但低值会增加功耗,低值还会给发射机带来过重的负载。

总线的可变拓扑可能使情况变得更加复杂。

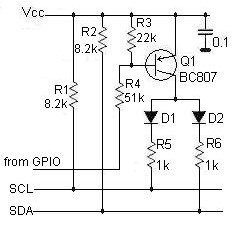

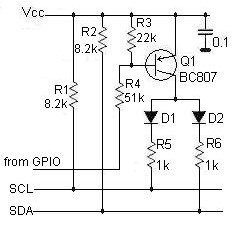

因此,当您的系统功率受限并且需要在不同的 I2C 模式下使用多个 I2C 芯片时,您必须在这些芯片之间进行折衷。或者您可以使用自适应上拉电阻,如图 1所示。

图 1:自适应上拉,其中闭合

晶体管将附加

电阻器 R5 和 R6 与主上拉电阻器 R1 和 R2 并联连接

该电路相当简单:闭合晶体管将附加电阻器 R5 和 R6 与主上拉电阻器 R1 和 R2 并联。

例如,连接可以通过 GPIO 控制,如图 1 所示,并且应该在快速数据交换发生之前完成。

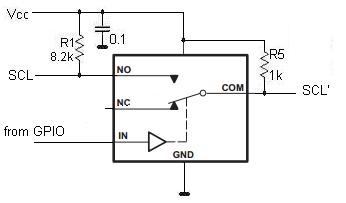

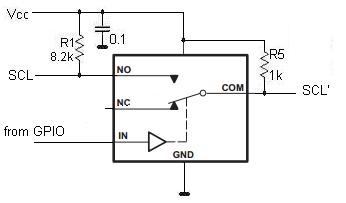

另一种解决方案如图2所示,它代表整个电路的一半(为简洁起见,省略了SDA的后半部分)。该电路使用模拟

开关(例如TI的TS5A3159)来断开总线的“快速”部分。当其断开时,电阻器 R5 在总线上提供高(空闲)电压电平。请注意,应考虑足够大的开关电容(20 至 100pF)。

图 2:替代的自适应上拉解决方案,使用

模拟开关断开总线的“快速”部分。