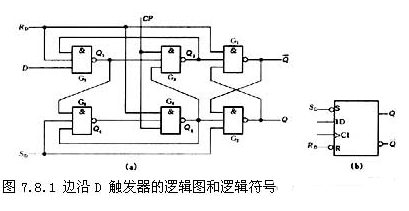

D

触发器(D flip-flop)是

数字电路中常用的触发器类型之一,用于存储一个位的状态。下面是D触发器的基本原理:

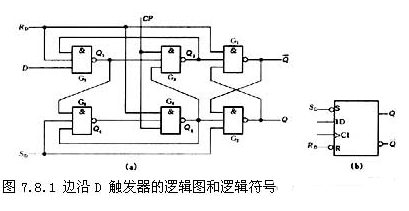

结构:

D触发器由两个输入端(D和时钟CLK)、一个输出端(Q)和一个反馈端(Q')组成。

当时钟信号到达时,D端的输入数据会被传输到输出端Q。

工作原理:

当时钟信号为高电平时,在上升沿或下降沿(取决于触发器类型)时,D端的输入数据被传输到输出端Q。

当时钟信号为低电平时,无论D端的输入如何变化,输出端Q的状态都不会改变。

时序图:

时钟上升沿时,D端的输入数据被传输到Q端。

时钟下降沿时,Q端的输出保持不变。

应用:

D触发器常用于时序电路设计、

寄存器、

计数器等数字电路中。

可以通过级联多个D触发器实现数据的移位操作。

总的来说,D触发器是一种常见的数字电路元件,用于在时钟信号的控制下存储和传输数据。通过合理设计和连接,可以构建各种数字

逻辑电路以满足不同的应用需求。