足够的故障检测响应时间约为 2 s [2],该时间决定了电源开关所需的短路承受时间 (SCWT) 额定值(即设备可以承受短路事件的短时间) ,在源极端子和漏极端子之间施加高电压和高电流。)

图 1. 三相电机驱动方案中采用的功率器件,显示了两种短路情况:(a) 高侧和低侧之间的直通,以及 (b) 感性负载上的短路。图片由 Bodo's Power Systems提供

为了支持高压 GaN FET 的持续采用,确保高 SCWT 非常重要。不过,考虑到它们的固有属性,这可能很困难。与传统硅器件相比,GaN FET 以及其他宽带隙器件可以在更小的面积内提供更高的功率密度。因此,当遇到短路条件(同时出现高电压和高电流浪涌以及极端瞬时功耗)时,GaN 器件可能会经历更急剧的温度上升,从而导致 SCWT 比硅基器件更短。

保护足够,性能降低……性能足够,保护降低

研究已证明使用 600 V GaN 器件在 400 V 电压下实现 SCWT ≥ 3 s 的能力 [3]。然而,由于的器件归一化 R on大于 20 Ω·mm (> 9 mΩ·cm 2 ),因此性能受到影响,对于市场采用而言,该值相当高。

商用 600 V GaN 器件的表现也好不到哪里去。在 400 V 下进行测试时,具有竞争性特定 R on的商业器件的 SCWT被限制为 < 0.5 s [4] [5]。因此,增加 GaN 器件的 SCWT,同时保持具有竞争力的低比导通电阻,对于在不影响性能的情况下实现短路能力至关重要。

解决方案:短路限流器

使用称为短路电流限制器 (SCCL) 的技术 [6] [7](图 2),可以通过减少短路电流来控制短路事件期间的功耗(保持在较低水平)从漏极到源极,导通电阻的降低。在两芯片常关 GaN 平台中,可以通过控制 Si-FET 的饱和电流 (I d,sat ) 或 GaN-HEMT 的饱和电流来实现更低的短路电流和更高的 SCWT 。

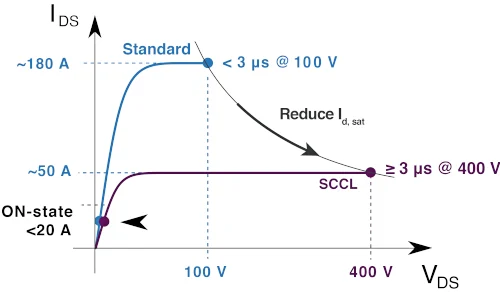

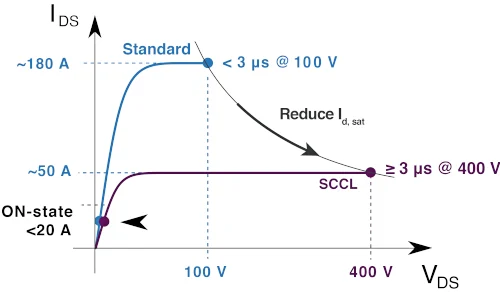

图 2. 获得的短路电流限制器 (SCCL) 可降低漏源饱和电流 (I ),从而增加器件的 SCWT,同时保持较低的通态电阻。图片由 Bodo's Power Systems提供

出于分析目的,进行了后者:通过降低GaN-HEMT 的I d,sat 来增加 SCWT。

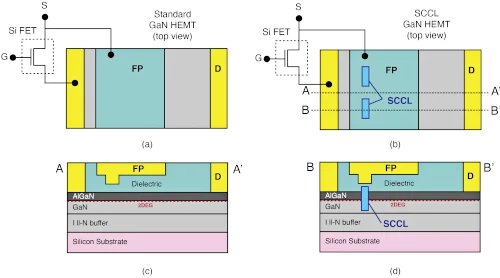

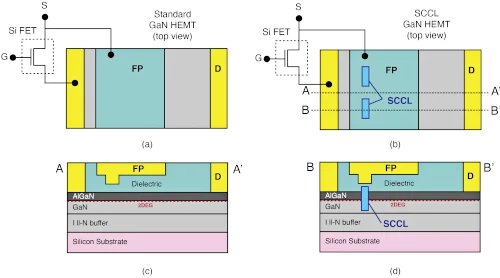

SCCL 是在 Transphorm 的技术上实现的,通过使用专有工艺去除沿 GaN-HEMT 宽度的 2DEG 通道片段。标准 GaN-HEMT 和带有 SCCL 的 GaN-HEMT 的顶视图分别如图 3a 和图 3b 所示。SCCL 装置的纵向横截面如图 3c 和图 3d 所示。AA' 截面是沿着电流孔径路径截取的,其中 2DEG 从源极到漏极不间断,

电子可以在导通状态下流动。在孔径中,场板结构的 2DEG 特性(电荷密度和迁移率)和夹断电压与标准器件相同。

截面 BB' 是沿着电流阻挡路径截取的,显示在场板结构的有限部分下缺乏 2DEG。电流阻挡分段(电流阻挡区域的长度、宽度和周期性)的正确设计确保了对饱和电流的良好控制,同时保持具有竞争力的低导通电阻。R on的增加是可能的,因为 R on主要由 GaN-HEMT 漏极接入区(相当于传统功率器件中的“漂移区”)决定,而不受 SCCL 阻挡区的影响。事实上,为了控制I d,sat,仅沿着整个源极-漏极间距以小长度部署电流块就足够了。

图 3. 两芯片常关 GaN 开关的俯视图(a)不带短路电流限制器(SCCL),(b)带短路电流限制器 (SCCL)。SCCL 是通过沿着 GaN HEMT 的宽度去除 2DEG 沟道的片段来实现的。沿具有 (c) 当前孔径和 (d) 当前块的路径截取的纵向横截面。附图并非按比例绘制。

实验结果

将标准 GaN 器件 [8] 与具有 SCCL 的 GaN 器件进行了比较。两款器件具有相同的芯片面积、相同的 650 V 额定电压,并采用 8x8 mm PQFN 封装。

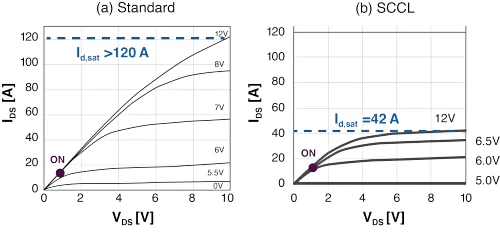

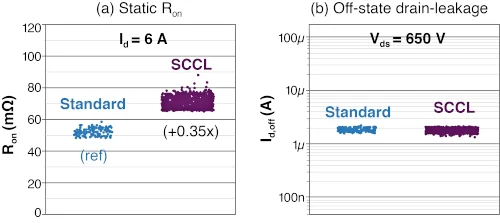

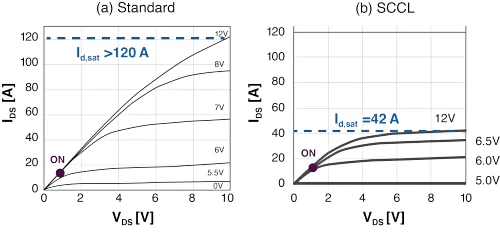

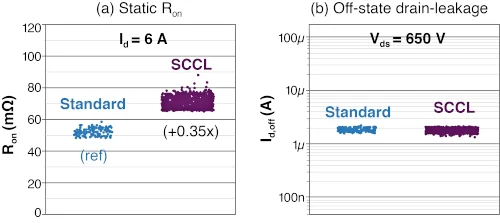

图 4 显示了室温输出特性:当栅极完全导通 (Vgs = +12 V) 时,标准器件的平均静态 R on为 53 mΩ,饱和电流 (I d,sat ) 超过 120 A ,而采用 SCCL 的器件的平均静态导通电阻为71 mΩ,并且 I d,sat显着降低为 42 A。借助 SCCL 技术,我们能够将 I d,sat 降低 3 倍,而电流消耗仅为 0.35 x 静态导通电阻增加(图 5a)。

图 4. (a) 标准 650-V GaN 器件和 (b) 采用 SCCL 的 650-V GaN 器件的室温输出曲线。当栅极完全导通 (Vgs = +12 V) 时,标准器件的饱和电流 (I d,sat ) 超过 120 A,而具有 SCCL 的器件的 I d,sat明显较低,为 42 A。 I d,sat降低了 3 倍。导通电阻仅增加 0.35 倍。图片由 Bodo's Power Systems提供

值得注意的是,尽管 SCCL 器件的 I d,sat明显低于标准器件,但 SCCL I d,sat仍比额定直流电流(室温下 20 A)高 2 倍以上。这不仅对于确保良好的导通状态操作非常重要,而且对于导通瞬态期间输出电容 (C oss ) 的快速开关和快速放电也很重要。,SCCL 技术不会降低场板电介质隔离的质量,因为相对于标准器件,未观察到 650 V 断态漏电流增加(图 5b)。

图 5. (a) 在室温下获取的原始静态 R on,导通状态 Id = 6 A。SCCL 器件的 R on惩罚相对较小,为 +0.35x,因为当前模块仅部署在较短的部分中整个漏源长度。(b)室温下V ds = 650 V时获得的断态漏极漏电流。断态泄漏没有增加表明 SCCL 技术不会降低场板电介质隔离的质量。

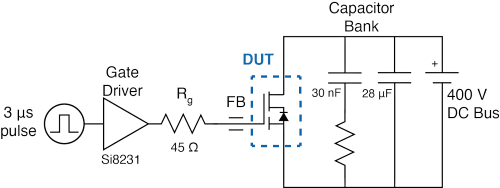

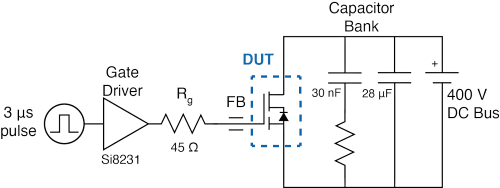

图 6. 短路测试板示意图。该板模拟硬开关故障,其中 DUT 直接在出现故障时开启,并在其端子上承受整个直流总线电压 (400V)。

为了评估 SCWT 的改进,在称为“硬开关故障”的坏情况下,在短路事件期间对器件进行了测试,并比较了使用 SCCL 和不使用 SCCL 的情况,其中 DUT 直接在出现故障时开启,并且必须承受短路脉冲的整个持续时间内的全总线电压。短路测试板如图 6 所示。在测试期间,通过完全打开栅极 3 s 来模拟短路事件。直流总线从 50 V 逐步增加到 400 V,增量为 50 V。在每一步中,施加一个短路脉冲并记录相关的短路波形。这项工作中的测试是在室温下进行的。

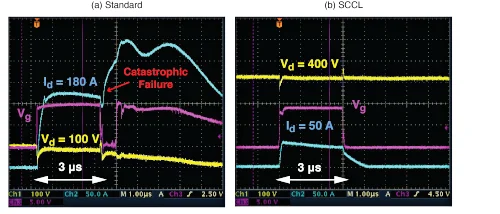

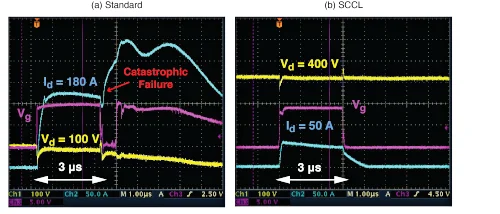

结果如图 7 所示。标准器件的短路电流为 180 A,在直流总线电压仅为 100 V 时 3 s 后失效,而 SCCL 器件的短路电流要低得多 (50 A),并且能够承受 400 V 电压下的 3 s 脉冲。短路鲁棒性的显着提高(超过 4 倍)证明了 SCCL 设计的概念验证和成功实施。

图 7. 在室温下在 (a) 标准 GaN 器件和 (b) 采用 SCCL 的 GaN 器件上采集的 3 s 短路脉冲。标准器件的短路电流为 180 A,在 100 V 的直流母线电压下出现故障,而 SCCL 的短路电流低得多 (50 A),并能承受 400 V 下的 3 s 脉冲。图片由 Bodo's Power Systems提供

为了确保 SCCL 器件能够在实际开关应用中以高性能和高可靠性运行,我们进行了直流和短路测试以及动态导通电阻测试、电感开关测试和高温反向偏置 (HTRB) 压力测试。执行。

使用 480 V 直流母线和 2 s 导通脉冲宽度进行的动态 R on测试表明,动态和静态 R on之间的相对增量约为 +18%。这与标准器件中动态和静态 R on之间的相对增加类似,表明 SCCL 阻挡区域不会加剧电荷捕获。

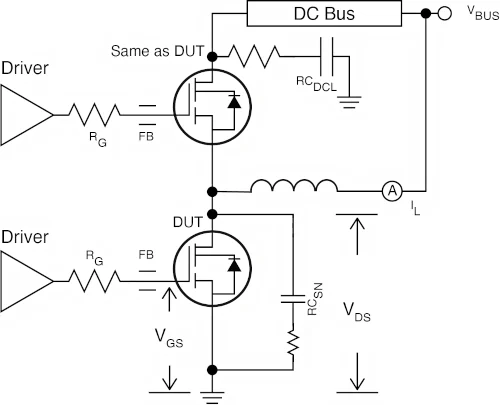

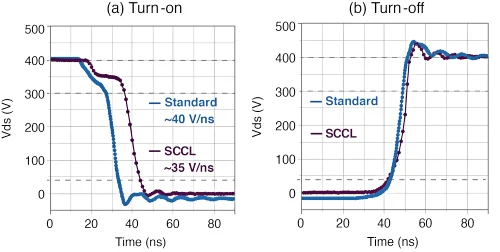

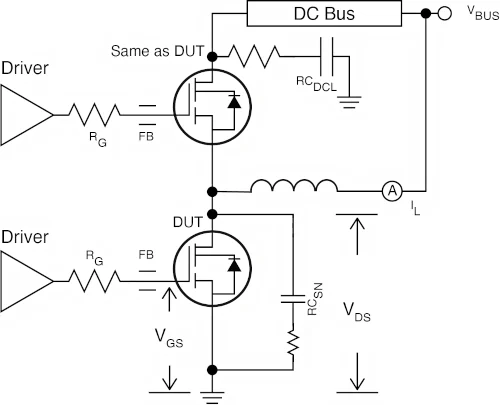

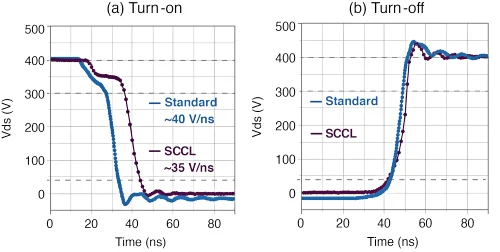

使用 400 V 直流母线和 15 A 负载电流进行的感应开关测试(图 8)表明,在导通和关断期间,这对 SCCL 器件的 dv/dt 与标准器件(≥35 V/ns,Rg = 50 Ω,图 9),表明 SCCL 的低 I d,sat不会妨碍输出电容 (C oss ) 的充电和放电。

图 8. 感应开关测试板原理图。图片由 Bodo's Power Systems提供

在 HTRB 测试期间,80 个部件在 150°C 和 520 V 的条件下承受反向偏压 1000 小时。250 小时和 1,000 小时后,没有观察到熔断器故障、泄漏没有增加,并且退化参数 R 相对较小(约 5%)。请参见图 10。退化时的小参数 R与标准器件中观察到的类似,因此表明 SCCL 阻塞区域不会引入任何额外的退化和/或故障机制。对于 SCCL 技术的未来 JEDEC 和汽车资格来说,这是一个充满希望的结果。

结论

事实证明,SCCL 是一种高性能、高可靠性的解决方案,可将 GaN 功率器件的 SCWT 在 400 V 下提高至 3 s,同时导通电阻的增加有限。SCCL 将短路电流降低了 3 倍以上,并将短路稳健性提高了 4 倍以上。截至目前,导通电阻的损失仅限于 0.35 倍。通过不断优化 SCCL 设计可以进一步减少 Ron 惩罚。从包括动态 Ron 测试、电感开关测试和 100 小时 HTRB 在内的初始表征活动来看,SCCL 技术已证明具有与标准 Transphorm 技术类似的开关性能和可靠性

图 9. 标准器件和 SCCL 器件在约 15 A 的感性负载电流下采集的 (a) 开通瞬态和 (b) 关断瞬态。SCCL 器件具有与标准器件相似的 dv/dt,表明 SCCL 的低 I d,sat不会妨碍输出电容 (C oss ) 的充电和放电。图片由 Bodo's Power Systems提供

图 10. 在150°C 和 520 V 的 SCCL GaN 器件(80 个部件)上进行 1000 小时 HTRB 测试之前和之后测量的导通电阻和漏极泄漏。250 小时和 1000 小时后,我们观察到没有

保险丝故障,没有泄漏增加,并且退化参数 R 相对较小(约 5%)。退化时的小参数 R与标准器件中观察到的类似,因此表明 SCCL 阻塞区域不会引入任何额外的退化和/或故障机制。