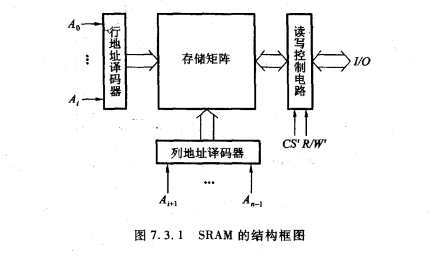

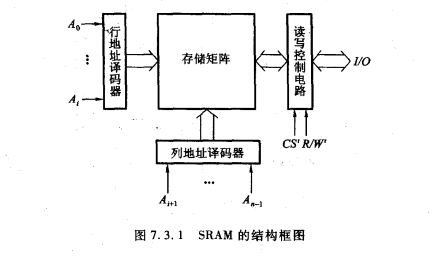

SRAM电路通常由存储矩阵、地址译码器和读/写控制电路(也称输入/输出电路)三部分组成,如图7.3.1所示。

在读/写控制电路上都设有片选输入端(csc当CS′=0时 RAM 为正常工作状态;当CS′=1时所有的输入/输出端均为高阻态,不能对RAM进行读/写操作。

图7.3.2是一个1024×4位 RAM的实例——2114的结构框图,其中4096个存储单元排列成64行×64列的矩阵。10位输入地址代码分成两组译码。AA6位地址码加到行地址译码器上,用它的输出信号从64 行存储单元中选出指定的一行。另外4位地址码加到列地址译码器上,利用它的输出信号再从已选中的一行里挑出要进行读/写的4个存储单元。

‖O‖O既是数据输入端又是数据输出端。读/写操作在R/W′和csc信号的控制下进行。当CS′=0,且R/W′=1时,读/写控制电路工作在读出状态。这时由地址译码器选中的4个存储单元中的数据被送到。‖O‖O。

当CS′=0,且R/W′=0时,执行写入操作。这时读/写控制电路工作在写入工作状态,加到∪OI/O端的输入数据便被写入指定的4个存储单元中去。

2114采用高速NMOS工艺制作,使用单一的+5V电源,全部输入、输出逻辑电平均与 TTL 电路兼容,完成读或写操作的时间为 100~200 ns。

若令CS′=1,则所有的‖O端均处于禁止态,将存储器内部电路与外部连线隔离。因此,可以直接将‖OWO与系统总线相连,或将多片 2114 的输入/输出端并联运用。免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。