什么是 DRAM?

内存是计算机运行的基础。当与 CPU 结合使用时,可以运行指令集(程序)并存储工作数据。随机存取

存储器(RAM)是一种众所周知的存储器类型,之所以如此称呼是因为它能够以大致相同的时间延迟访问存储器中的任何位置。

动态随机存取存储器(DRAM)是一种特定类型的随机存取存储器,可以以更低的成本实现更高的密度。笔记本电脑和台式机中的内存模块使用 DRAM。

DRAM 与 SRAM

其他类型的存储器(例如 SRAM、MRAM 和闪存)可能会在以后的文章中讨论。简而言之,DRAM 代表 动态 随机存取存储器,而 SRAM 代表 静态 随机存取存储器。的区别是 DRAM 使用

电容器(我们将在本文后面讨论),而 SRAM 则不使用电容器,不过还需要考虑不同的处理、不同的速度以及开发人员的不同成本等因素。

DRAM 是如何工作的?

DRAM 由 IBM 的 Robert Dennard 于 1966 年发明,其工作原理与其他类型的内存有很大不同。DRAM 中的基本存储单元由两个元件组成:

晶体管和电容器。

当需要将一个位放入存储器时,晶体管用于对电容器充电或放电。充电的电容器代表逻辑高电平或“1”,而放电的电容器代表逻辑低电平或“0”。充电/放电是通过字线和位线完成的,如图 1 所示。

图 1. 在 DRAM 中,一位被存储为电容器上是否存在电荷

在读取或写入期间,字线变高并且晶体管将电容器连接到位线。无论位线上有什么值(“1”或“0”),都会从电容器中存储或检索。

每个电容器上存储的电荷太小而无法直接读取,而是通过称为读出

放大器的电路来测量。感测放大器检测电荷的微小差异并输出相应的逻辑电平。从位线读取的行为迫使电荷流出电容器。因此,在 DRAM 中,读取具有破坏性。为了解决这个问题,需要执行一种称为预充电的操作,将从位线读取的值放回到电容器中。

同样的问题是电容器随着时间的推移会泄漏电荷。因此,为了维持存储在存储器中的数据,必须定期刷新电容器。刷新就像读取一样,确保数据永远不会丢失。这就是 DRAM 获得“动态”绰号的由来——DRAM 单元上的电荷每隔一段时间就会动态刷新。将此与 SRAM(静态 RAM)进行对比,SRAM 无需刷新即可保留其状态。

DRAM 是如何组织的?

根据应用的不同,DRAM 可以有不同的形式。图 2 显示了包含多个板载 DRAM 芯片的 DIMM(双列直插式内存模块)。

图 2. 包含多个 DRAM 芯片的 1 GB DIMM

此 DIMM 包含 1 GB 内存,但请注意贴纸上印有“2Rx8”。2R 表示该模块的等级为 2,而 x8(发音为“by 8”)表示来自每个 DRAM 芯片的数据的输出宽度。列是一组可单独寻址的 DRAM。在这种情况下,一个列是一组四个 DRAM 芯片。由于总共有 8 个(前/后),所以我们有 2 个等级。

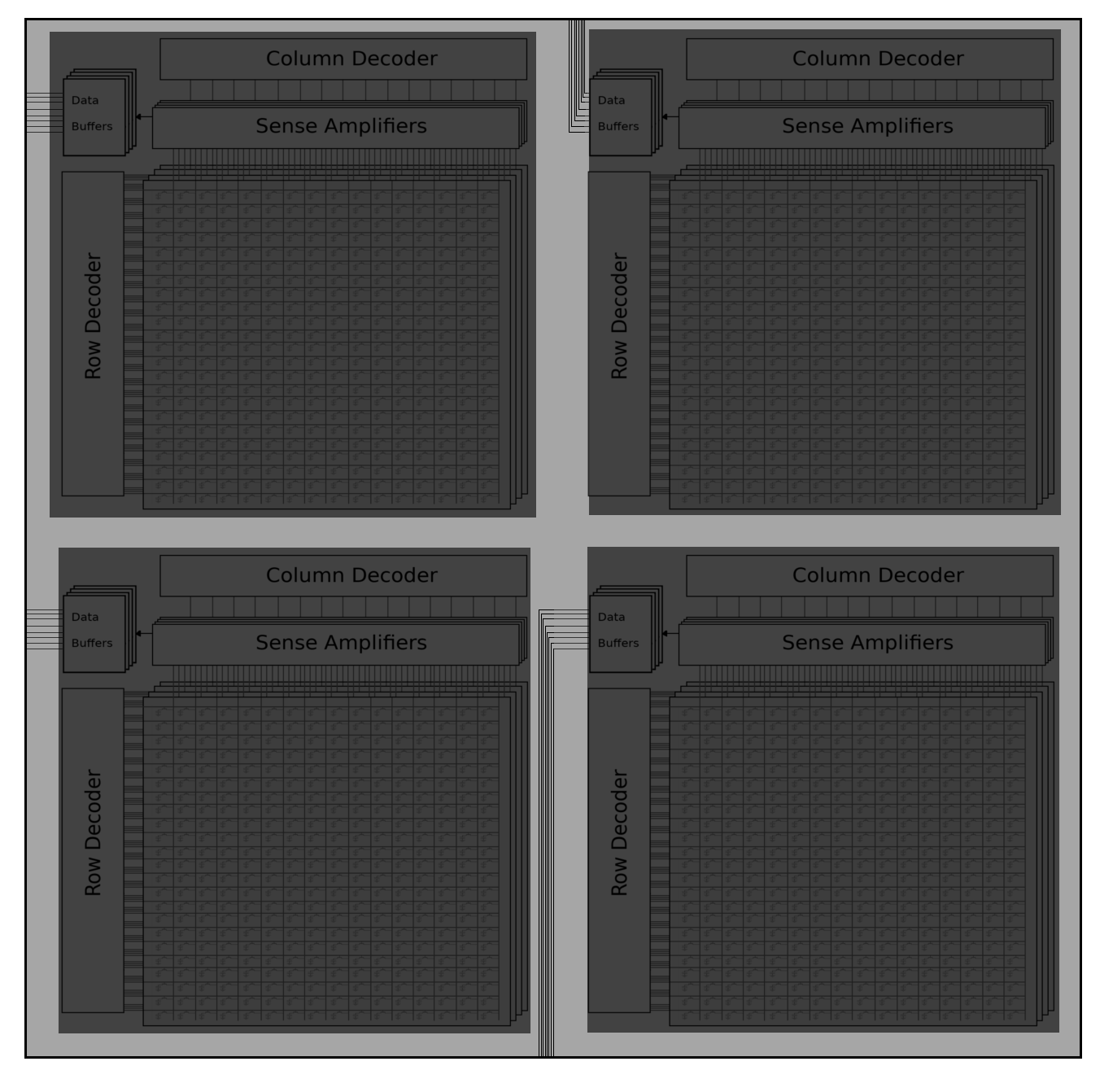

DRAM 模块的等级是 DIMM 内的组织级别。下面,每个芯片被组织成许多包含行和列的存储体和存储器阵列。图 3 显示了具有四个存储体的 DRAM 芯片。

图 3. 具有四个存储体的 DRAM 芯片

每家银行都独立于其他银行运营。这意味着读取、写入和预充电都可以在一个存储体上完成,而不会影响另一存储体。

、银行、行和列

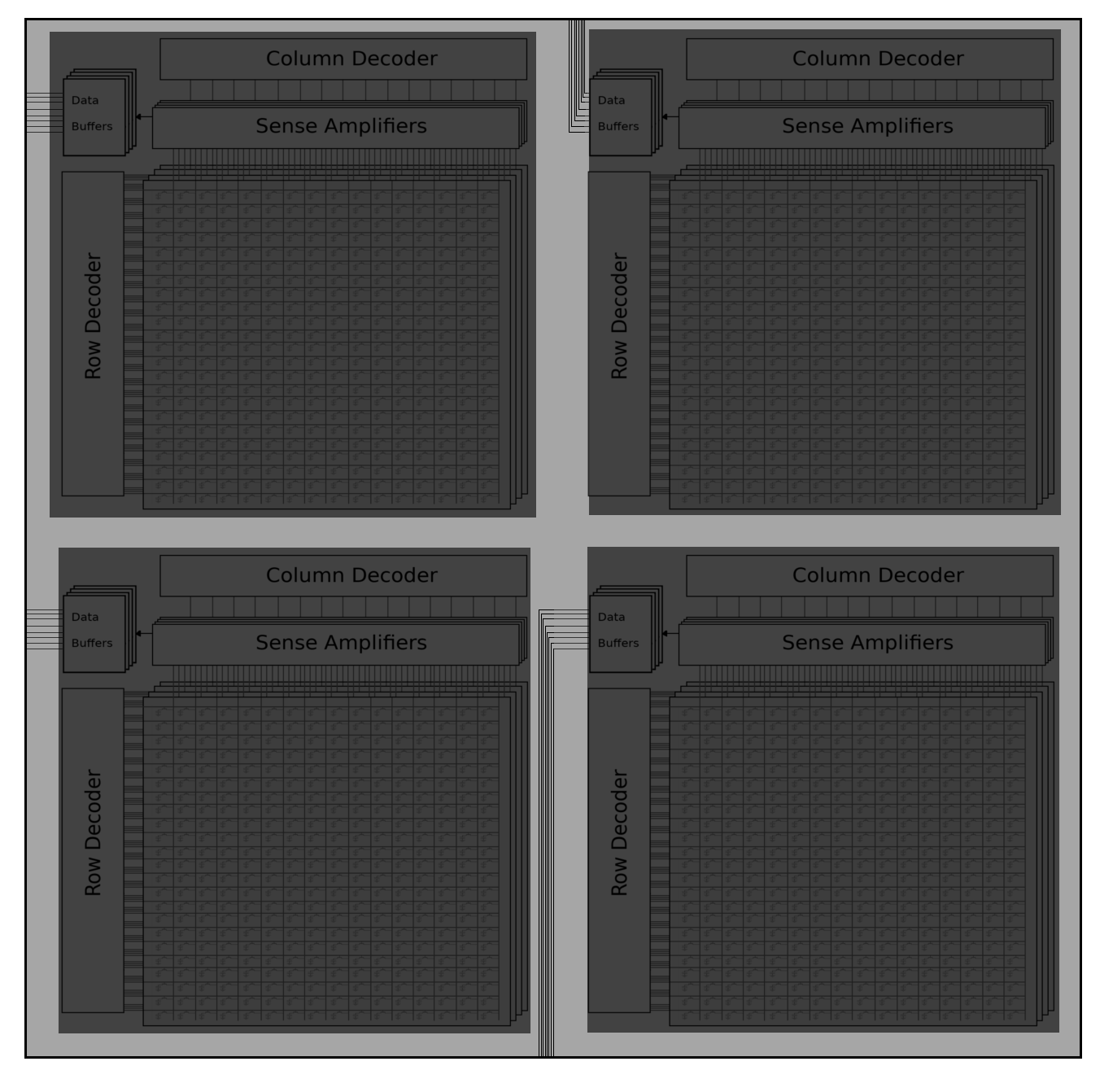

如前所述,DRAM 的列是一组可单独寻址的 DRAM 芯片。每个 DRAM 芯片进一步组织成多个包含一组存储器阵列的存储体。每个存储体的存储器阵列数量等于输出宽度的大小。因此,在 x4 DRAM 芯片中,每个内部存储体都有四个存储器阵列。图 4 显示了单个 x4 组的示例。

图 4. 由解码器、读出放大器和存储器阵列组成的 x4 组

灰色部分是设计为行和列网格的存储器阵列。一组解码器用于访问行和列,选择存储器阵列内的单个交叉点。正是在这个交叉点,一个小电容器存储了代表正在访问的数据的电荷。

读出放大器对电容器执行预充电操作,并为多个数据缓冲区生成逻辑电平输出,这些数据缓冲区存储数据,直到内存控制器或 CPU 检索数据为止。

结论

在本文中,我们研究了动态随机存取存储器 (DRAM) 背后的基本操作原理。DRAM 在个人计算机中极为常见,是任何计算机正常工作所需的基本组件。DRAM 的工作原理是利用电容器上是否存在电荷来存储数据。

由于单个 DRAM 单元仅由两个组件(晶体管和电容器)组成,因此 DRAM 可以高密度制造,并且与其他类型的存储器相比价格便宜。我们还研究了包含多个 DRAM 芯片的 DIMM 以及这些 DRAM 芯片如何组织成存储单元阵列。