CCD 电压非常“非标准”。高电平时钟电压通常大于我们用于 CMOS 逻辑的电压,而低电平电压通常延伸到地电位以下。

我随机选择了一些 CCD 数据表,为您提供一些预期的示例。如果您不明白我所说的“帧传输”和“行间传输”的含义,请务必阅读上一篇文章。

安森美半导体的 KAI-1020:这是一款行间传输器件,分辨率为 1000 × 1000 活动像素。控制电压范围为 –9V 至 +15V。但是,应用于芯片的控制信号使用 5V 逻辑;内部驱动器将逻辑信号转换为电荷传输门所需的电压电平。

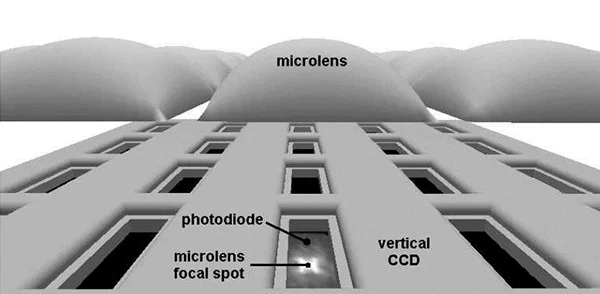

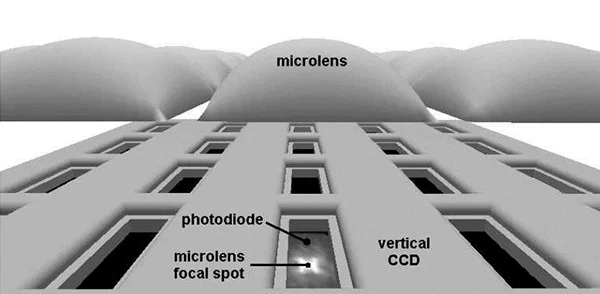

我想您可能会喜欢这个来自 KAI-1020 数据表的行间传输 CCD 的流畅 3D 表示。

Sony 的 ICX059CL:这是一款 752 × 582 像素、行间传输 CCD,适用于单色摄像机。如果我正确理解数据表,它使用 15 V 将电荷包从光电

二极管传输到垂直移位寄存器,使用 –8.5 V 到 0 V 进行垂直传输时钟,使用 0 V 到 5 V 进行水平传输。下图传达了该设备的整体架构。

图表取自 ICX059CL数据表。

Texas Instruments 的 TC281:这款 1000 × 1000 像素图像传感器采用帧传输架构。大多数时钟的低电平为 –10 V,高电平为 +2 V。

带×符号的部分是感光像素阵列,下半部分是存储阵列。该图取自 TC281数据表。

读出时钟配置

让我们回到半导体层面,讨论如何准确地说服电荷包从像素移动到输出

端子。我们知道,这是通过施加电压序列来实现的,电压序列依次创建势阱和势垒序列,但事实证明,有几种不同的方法可以创建必要的电势变化。

四相时钟

直接的方法使用四个时钟相位。我们将详细考虑四阶段方法,然后我将简要提及其他方案。

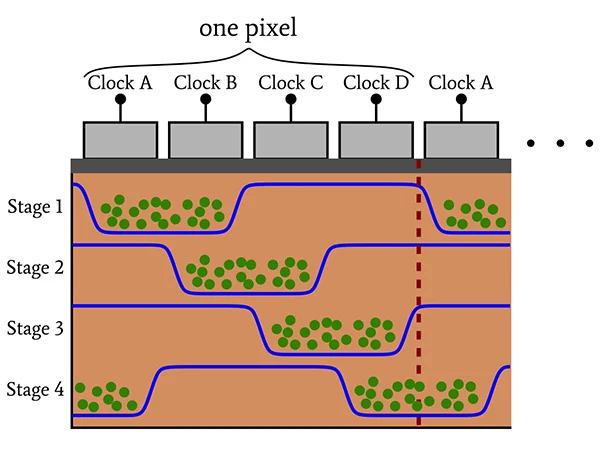

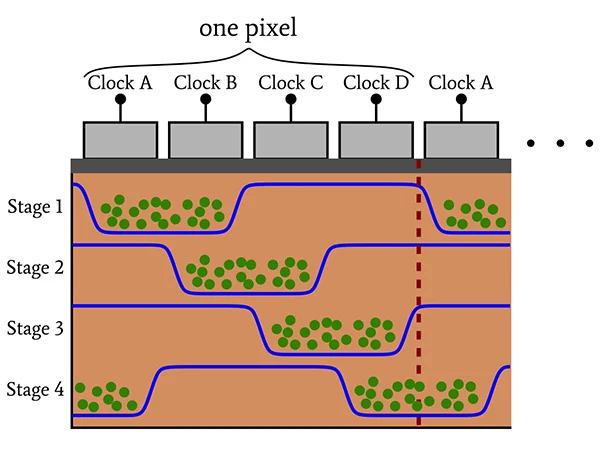

如下图所示,四相 CCD 每个像素有四个门。因此,需要施加到像素的四个不同部分的四个单独的时钟信号来将电荷包移动到相邻像素中。

(请注意,如果这是行间传输 CCD,我们可能会说“移位寄存器部分”而不是“像素”,因为电荷包不会穿过行间传输架构中的光敏区域。)

该过程从我们所说的阶段 1 开始。时钟 A 和时钟 B 为高电平,时钟 C 和时钟 D 为低电平。(请记住,“高”意味着更高的电压,会产生吸引

电子的势阱,而“低”会产生阻挡电子的势垒。)

在继续之前,请先看一下下图,并在我们完成接下来的三个阶段时参考它。

在阶段,电荷在A门和B门下方的势阱中积累,并且由于被C门和D门下方的势垒阻挡而无法移动。

在阶段 2中,时钟 A 变低,时钟 C 变高。时钟 B 和 D 不变。这会将所有电子向右移动一步,因为现在在门 B 和 C 下有一个阱,在门 A 和 D 下有一个势垒。

在阶段 3中,时钟 B 变低,时钟 D 变高。我们再次将电子向右推了一步,因为现在势阱位于门 C 和 D 下方。

在第 4 阶段,时钟 A 变高,时钟 C 变低。现在我们有一个势阱,从一个像素的栅极 D 延伸到下一个像素的栅极 A。

阶段5与阶段1相同。电荷完全转移到相邻像素,并且循环继续。

三相、两相和单相时钟

四相方案的问题是传感器分辨率受到每个像素需要四个门的限制。我们可以通过减少电荷传输所需的时钟数量来减小像素尺寸,从而提高像素密度,但为了减少时钟数量,所施加的电压必须变得更加复杂。

四相控制的替代方案是三相、伪两相、真两相和虚拟相(即单时钟)控制。以上述 CCD 传感器为例,KAI-1020 使用两相时钟,ICX059CL 使用四相时钟,TC281 使用 TI 描述的“专有虚拟相位”时钟方案。