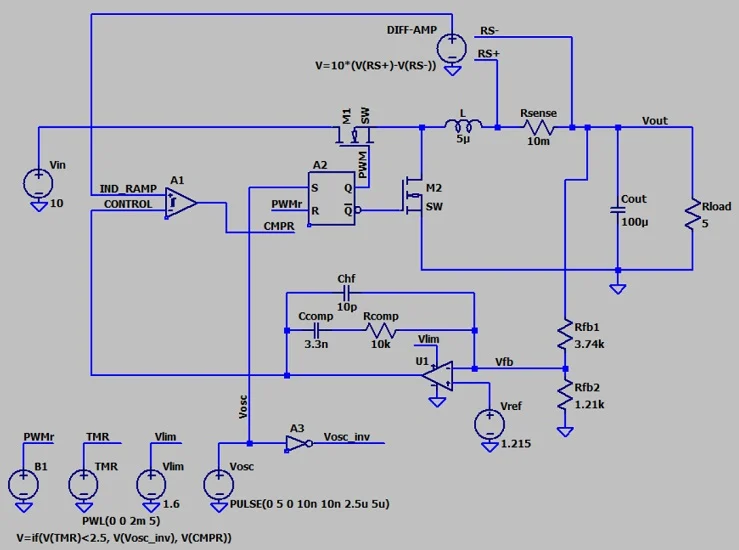

我们探讨了图 1 中所示的电流模式控制 (CMC) 降压转换器的设计原理和基本操作。在本文中,我们将使用仿真对电路的电气性能进行相当精细的分析。行为。

峰值 CMC 降压转换器的 LTspice 原理图。

图 1. 在 LTspice 中实现的 CMC 降压转换器。

启动行为

我的 LTspice 实现和我所基于的电路之间有两个主要区别:

缺乏坡度补偿,我们在上一篇文章末尾讨论过。

我添加了额外的电路,可以帮助快速启动调节器,我们现在将讨论这一点。

如果您检查图 1,您会发现比较器的输出并未直接连接到 SR 锁存器的复位线。相反,由任意行为电压源 B1 控制的PWM R信号驱动复位线。在标记为TMR (“定时器”)的电压源的帮助下,B1 初将PWM R连接到设置锁存器的方波的反相版本。TMR电压从0V逐渐上升到5V;在仿真开始后t = 1 ms 时,电压超过 2.5 V。

这种情况导致 B1 将PWM R与反相

振荡器信号断开并将其连接到比较器的输出。这听起来可能很复杂,但这只是让反馈环路完成其工作的一种方式——它迫使调节器开始切换并产生一些电流和电压动作。

如果您完全复制我的电路,您将不需要启动辅助电路,但即使是微小的调整也可能会干扰启动,并且如果稳压器不切换,您将无法有效地诊断和解决问题。

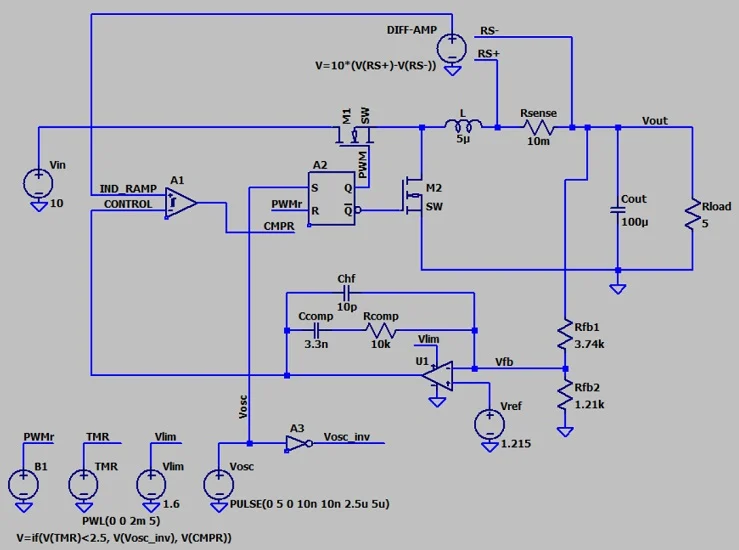

图 2 显示了我的原理图,没有启动辅助电路。我们将使用此版本的原理图进行本文讨论的模拟。请注意,比较器的输出直接连接到锁存器的复位引脚。

没有启动辅助电路的峰值 CMC 降压转换器的 LTspice 原理图。

图 2.不带启动辅助电路的 CMC 降压转换器。

输出收敛

图 3 显示了启动后稳压器的瞬态行为。

CMC 降压转换器启动后的电压行为。 输出电压短暂地出现峰值,然后稳定在所需的水平。

图 3. CMC 降压转换器启动后的瞬态行为。

该稳压器仅需约 100 μs 即可高精度地收敛到所需的输出电压。如图 4 所示,纹波幅度相当低。

模拟 CMC 降压转换器的输出纹波。

图 4. CMC 降压转换器输出纹波。

误差

放大器 正如我在上一篇文章中所解释的,误差放大器没有直流反馈路径,因此如果输出缓慢高于或低于所需电压,误差放大器将充当比较器。然而,在正常情况下,调节器环路被锁定到输出电压。V FB和V REF之间的差异是由频繁发生的微小幅度变化引起的。这意味着误差放大器的作用类似于放大器,而不是比较器,如图 5 所示。

模拟 CMC 降压转换器中误差放大器的电压波形。

图 5. CMC 降压转换器中的正常误差放大器行为。

比较器和 SR 锁存器

CONTROL信号成为允许

电感器电流控制PWM动作的阈值。让我们看看它是如何工作的。

该循环的设计使得CONTROL信号处于相对于IND_RAMP信号的适当范围内。系统的振荡器连接到锁存器的设置引脚。在每个

开关周期开始时,振荡器转换为逻辑高电平,导致锁存器的Q输出依次转换为逻辑高电平。这称为“设置”锁存器。

如果Q为高电平,则主电源开关 (M1) 开启。当 M1 导通时,电流流过电感器,并且IND_RAMP逐渐上升。当代表电感器电流的电压超过CONTROL建立的阈值电平时,比较器输出变高。这会导致锁存器的Q输出转换为逻辑低电平,从而“重置”锁存器。现在 M1 关闭,电感器电流开始下降。振荡器终再次设置锁存器,然后重复该循环。

简而言之,在单个开关周期的过程中,以下事件依次发生:

振荡器变为逻辑高电平。

锁存器的Q输出变为逻辑高电平。M1现已开启。

电感电流逐渐上升。

代表电感器电流的电压超过控制阈值。

比较器输出变高。

锁存器的Q输出变为逻辑低电平。M1 现在已关闭。

电感电流逐渐下降。

图 6 中的多窗格图很好地讲述了这个故事,但您可能需要思考一会儿。

CMC 降压转换器中比较器和 SR 锁存器的电压波形。

图 6.比较器和 SR 锁存器在 0.040 ms 周期内的电压行为。

图 7 中的版本更清楚地显示了时序关系: PWM信号的逻辑高电平部分从振荡器信号的上升沿开始,在IND_RAMP达到CONTROL时结束,导致比较器重置锁存器。

比较器和 SR 锁存器的电压波形如图 6 所示,但时间周期较短。

图 7.比较器和 SR 锁存器在约 0.015 ms 内的电压行为。

占空比决定输出电压,但控制环路不必完全依赖输出电压来正确调整占空比。相反,输出电压通过误差放大器提供阈值。电感电流提供了控制功率开关的基本模式(因此是电流模式控制)。

比较器输出和开关状态之间以及开关状态和电感器电流之间的联系有时会导致IND_RAMP信号在CONTROL信号上方和下方呈锯齿形。反过来,这会导致PWM信号出现杂散转换。

这些转变不会严重损害稳压器的功能,但值得注意的是(至少出于模拟目的)您可以通过降低比较器的迟滞电压来缓解这些转变。前面的图是用 10 mV 的滞后电压生成的。在图 8 中,它已降低至 1 mV。

比较器和 SR 锁存器的电压波形如图 6 和 7 所示,但迟滞减少了 9 mV。

图 8.比较器和 SR 锁存器的电压行为,迟滞从 10 mV 降至 1 mV。

这些结果看起来好多了。尽管如此,我认为这种迟滞调整仅在我的无噪声仿真环境中才是解决方案。