串行数据传输比并行数据传输具有重要的优势,并且在许多系统中,这些优势足以证明添加对并行数据进行串行化和反串行化的电路是合理的,以便可以将其作为串行数据进行传输。然而,计算机

存储器是并行数据传输仍然盛行的应用领域之一。由于并行接口可以同时读取和写入许多数字信号,因此速度很快,设计人员一直在寻找使它们更快的方法。

一种古老但仍然相关的用于实现数据传输速率大幅提高的技术称为双泵浦,该功能将内存系统转变为双倍数据速率(DDR)内存系统。“单泵浦”内存系统采用历史悠久的策略,将数据从一个 IC 同步移动到另一个 IC。基本上,逻辑信号每个时钟周期改变,并由接收器在时钟的上升沿或下降沿进行采样。在此方案中,字传输速率不能超过时钟频率。

例如,如果您的时钟运行频率为 133 MHz,则(理想情况下)每秒可以传输 1.33 亿个字。请注意,位传输速率取决于系统架构,因为不同的计算系统使用不同的字长(8 位、16 位等)。双泵浦系统可以在 133 MHz 的频率下实现 266 MT/s(每秒数百万次传输)。钟。

在本文中,我们将了解单数据速率接口和双数据速率接口之间的差异、为什么使用 DDR 及其应用。

SDR 与 DDR:单数据速率和双数据速率接口

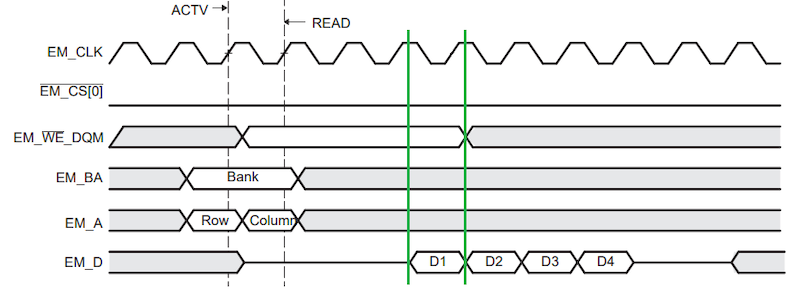

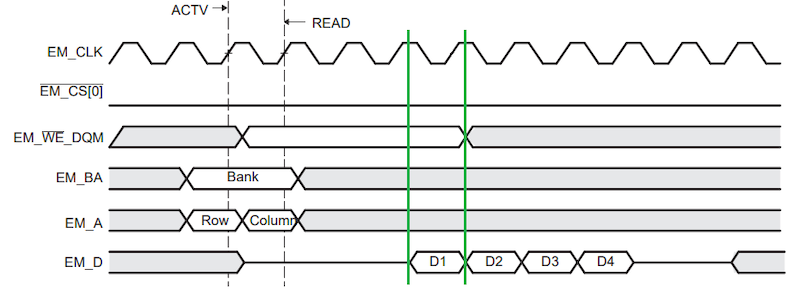

下面图 1 中所示的时序图是单数据速率存储器接口的示例。

单数据速率存储器接口的示例。

图 1.单数据速率存储器接口示例。图片[已修改]由德州仪器 (TI)提供

首先,使用 EM_BA 信号选择存储体,并通过 EM_A 信号建立行和列地址。数据字 D1、D2、D3 和 D4 在 EM_D 引脚上输出。请注意一个数据字如何占据 EM_CLK 信号的整个周期。

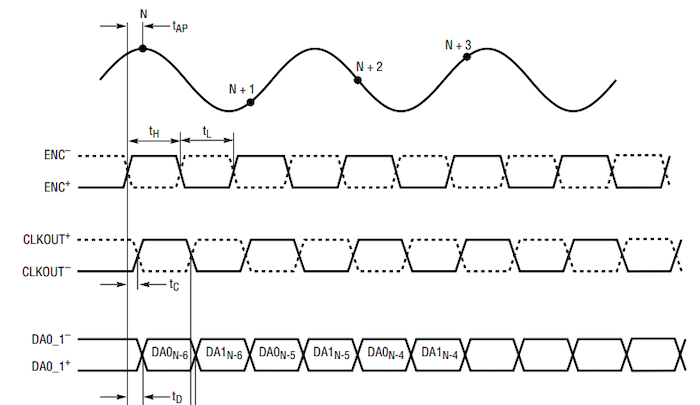

我们将看到的下一个时序图(图 2)描述了双倍数据速率接口。

双数据速率接口的示例。

图 2.双倍数据速率接口示例。图片由美光公司提供

“DQ”线表示数据信号,阴影区域之间的无阴影 X 形区域表示从一个字到下一个字的转换。您可以看到每个字只需要半个完整时钟周期。请记住,该芯片使用差分时钟,这就是时序图具有 CK 信号和互补 CK# 信号的原因。

动机:为什么要加倍数据速率?

您可能想知道为什么工程师要费尽心思为 DDR 信号创建新的逻辑,而他们本来可以将时钟频率提高两倍。对这一决定的主要解释包含在代表无数小时高速研发的两个词中:信号完整性。

高频信号(“高频”是相对于给定技术时代或应用场景的限制来理解的)是令电路板设计人员感到震惊的根源。这些信号:

因信道带宽有限而遭受更多色散

需要更多的电力消耗

更容易受到电容耦合和反射的影响,

任何 PCB 上存在的各种无意

天线可以更有效地进行辐射

使用测试设备来表征和排除故障也更加困难。例如,

示波器的模拟和数字带宽有限,并且随着频率的增加,它会在波形中引入更多的失真。

因此,在尝试实现更高的时钟速率之前,从现有时钟速率中提取尽可能多的吞吐量是有意义的。通过从单一数据速率接口转向 DDR 接口,设计人员可以显着提高数据传输速率,而无需更改系统的信号频率。即使数据信号的频率增加了两倍(这个新数据频率不高于先前的时钟频率),所有这些都可以实现。

DDR内存应用

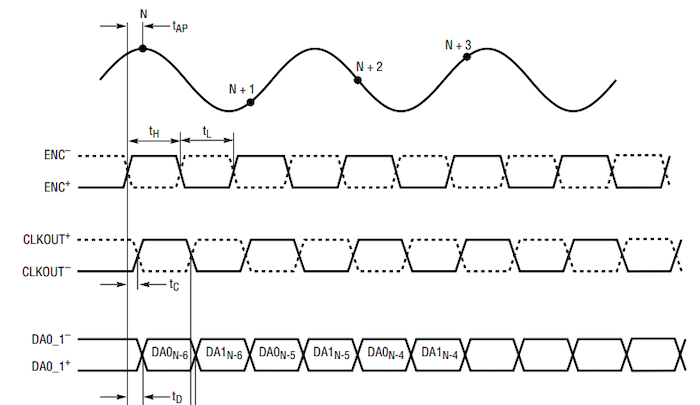

双泵浦是一种通用功能,已用于各种并行数据传输接口。甚至高速数据

转换器也采用了这种技术。例如,在图 3 所示的

模数转换器 (ADC) 时序图中,一个样本在一个完整时钟周期所需的时间内被数字化,但数字输出使用 DDR 时序,因为两个数据位被复用到每个样本上。输出。

示例 ADC 时序图,其中显示的所有信号都是差分信号。

图 3. ADC 时序图示例,其中显示的所有信号都是差分信号。图片由Analog/Linear Technology提供

然而,DDR并行传输仍然与计算系统中使用的SDRAM(同步动态随机存取存储器)密切相关。几十年来,工程师们一直在努力提高计算机移动和处理数字数据的速度,DDR 信号使他们能够将吞吐量加倍,同时保持当时可行的时钟频率。

1998年发布的代DDR SDRAM支持高达200 MHz的时钟频率以及高达400 MT/s的传输速率。然后是 DDR2、DDR3、DDR4,是我们目前使用的 DDR5。DDR5 的传输速率超过 7 GT/s。