磁阻RAM(MRAM)器件的工作结构是磁隧道结(MTJ)。

位状态被存储为与隧道势垒直接接触的两个磁性层的相对磁化方向,其中反平行方向(高状态)具有比平行方向(低状态)更高的结电阻。通过使电流流过结并将结电压与已知参考电压进行比较来读出位状态。

飞思卡尔的 MR2A16ATS35C 4Mbit MRAM 采用 0.18 微米六金属工艺制造,具有 256K x 16 位配置,采用 3.3V 电源运行,采用 44 引脚 TSOP II 型封装。

这种不寻常的部件总是引起我们的注意,因此我们忍不住要深入了解飞思卡尔如何将它们组合在一起。

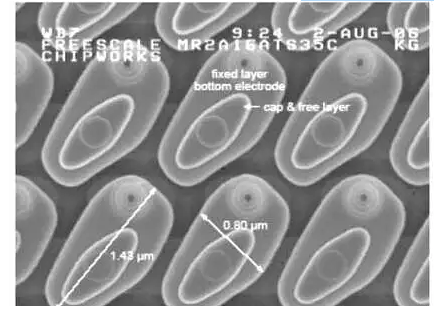

图1。在上板中心看到的

触点通向公共顶部电极,而在每个下板顶部边缘的触点通向衬底中的隔离(选择)

晶体管。

工作原理

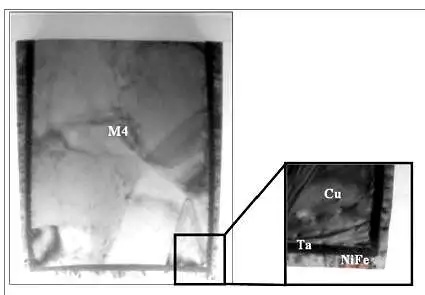

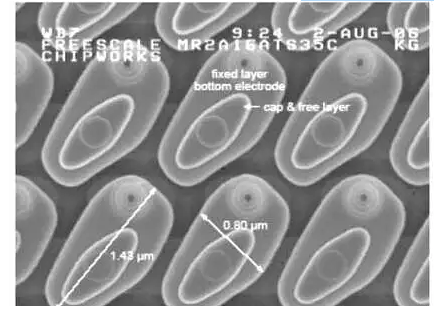

飞思卡尔 MRAM 单元具有对角放置在两个高电流写入线导体之间的多层 MTJ,这些导体由金属 4 和金属 5 形成,并且彼此成直角排列。该芯片已被延迟,以暴露一系列 MTJ 结构,显示较小的顶板覆盖在较大的底板上(上图 1)。

我们只能看到接线板阵列下方的下部写入线。在上板中心看到的触点通向公共顶部电极,而在每个下板通向顶部边缘的触点则通向衬底中的隔离(选择)晶体管。

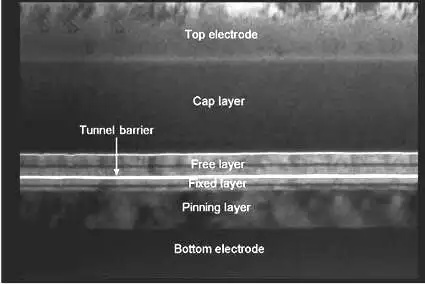

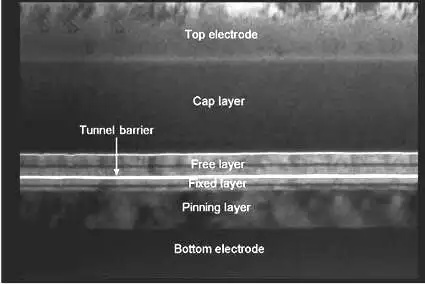

图2. 该器件使用磁阻隧道穿过夹在两个 SAF 层之间的绝缘隧道势垒,其中顶部 SAF 层为“自由”层,底部 SAF 为“固定”参考层。

上图 2 说明了 MRAM 单元的工作原理。该器件利用磁阻隧道效应穿过夹在两个合成反铁磁 (SAF) 层之间的绝缘隧道势垒。顶部SAF层是“自由”的(即其磁矩可以编程),底部SAF是“固定”(不可编程)参考层。

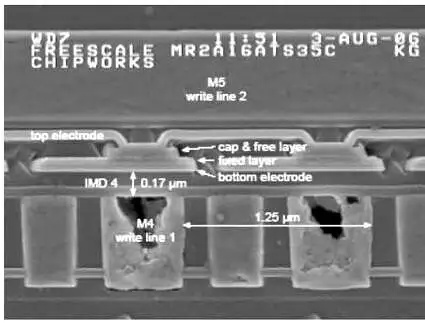

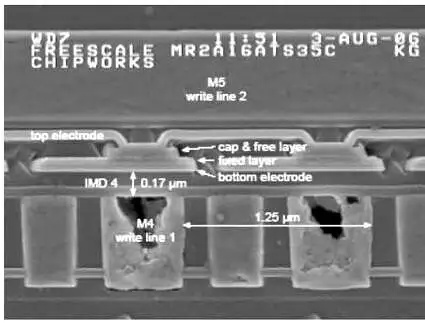

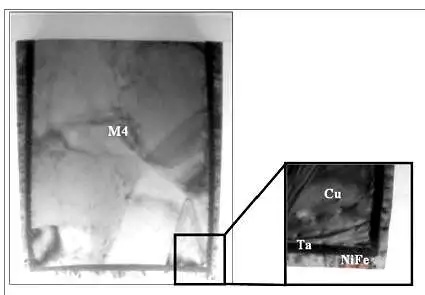

下面的图 3 显示了下部 M4 写入线的横截面和上部 M5 写入线的线性部分,中间有 MTJ 结构(此图中存在一些来自样品制备的空隙。)。

图3. 所示的是下部M4写入线的横截面和上部M5写入线的线性剖面,磁隧道结结构位于其间。

多层结构

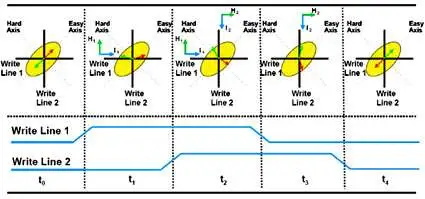

顶部和底部 SAF 层实际上都是三个子层,两个铁磁层由非磁性垫片隔开;自由铁磁子层使用具有几乎平衡磁矩的磁性可编程材料。

当施加磁场时,这使得磁矩像一对相连的“时钟指针”一样旋转。隧道屏障是氧化铝。下面图 4中的透射电子显微镜图像显示了多层结构。

图4. 顶部和底部 SAF 层实际上都是三个子层,两个铁磁层由非磁性垫片隔开;自由铁磁子层使用具有几乎平衡磁矩的磁性可编程材料。

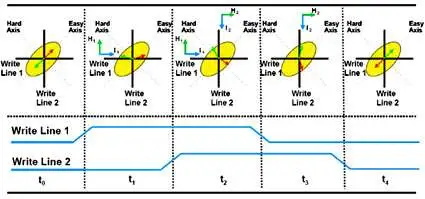

使用这种类型的结构(在其对角线方向)允许使用相同的双相脉冲序列(无论状态如何)使用两条写入线将磁矩切换 180°。这需要预读取以查看是否需要写入序列,但可以保护数据状态免受任一写入线上的单个脉冲的影响(下图 5 )。

写入线本身有一些有趣的结构怪癖,以优化与 MTJ 的磁耦合。有趣的是它们是由铜制成的。

图5. 写入线本身有一些有趣的结构怪癖,以优化与 MTJ 的磁耦合。

同时,焊盘和下金属层均采用符合0.18μm工艺的常规铝。据推测,这可以允许更高的电流密度,提供更高的磁场并保持单元间距较小。

镶嵌镶嵌结构还有助于使用导磁包层,该包层可以集中磁场——飞思卡尔声称添加这些层后磁通量增加了一倍。

底部写入线中的包层将磁场向上聚焦到隧道结中。这是通过在镶嵌线的势垒层结构中添加镍铁 (NiFe) 层来完美实现的(下图 6)。

图6. NiFe 被放置为外部阻挡层,然后是通常的 Ta 基阻挡层,然后用铜填充沟槽。

NiFe 被放置为外部阻挡层,然后是通常的钽 (Ta) 基阻挡层,然后用铜填充沟槽。

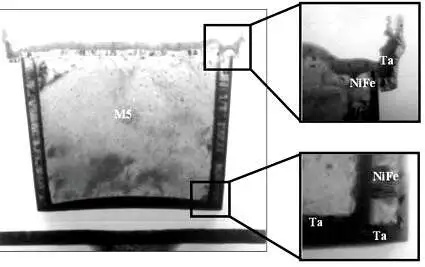

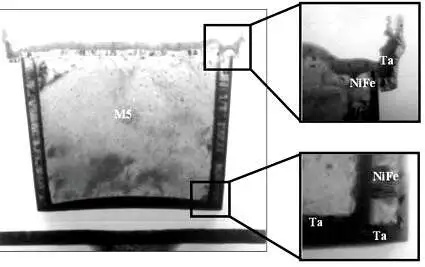

上面的写线更难制作。这是因为要将场聚焦到 MTJ,我们需要在线的顶部和侧面放置包层(图 2)。

下面的图 7 说明了飞思卡尔如何实现这一目标:他们在沟槽的底部和侧壁上放置了 Ta 阻挡层,然后是 NiFe 层。然后,将NiFe溅射远离沟槽底部并沉积另一个Ta阻挡层。

沟槽用铜填充并像往常一样平坦化,并沉积氮化物和氧化物金属盖层。这些被掩蔽和蚀刻以暴露存储器阵列中 M5 铜的顶部。沉积第二组 NiFe 和 Ta 层,然后抛光以去除多余的部分并隔离线条,在每个线条边缘留下“翅膀”。

图7. 飞思卡尔在沟槽的底部和侧壁上放置了 Ta 阻挡层,然后放置了 NiFe 层。然后,从沟槽底部溅射掉NiFe,并沉积另一个Ta阻挡层。

这是一个相对复杂的过程,但它达到了预期的目的。这涵盖了 MTJ 的基础知识。由于较低的金属层是铝以及 M4 和 M5 铜,因此该器件是少数具有真正混合金属化结构的部件之一,与大多数 130 nm 及更小部件中带有 Al 键合焊盘的铜金属不同。

这是了解该部件的制造历史的线索。当我们观察前端结构(即晶体管+M1”M3)时,它看起来非常像我们在其他器件中看到的台积电0.18微米工艺。仔细询问发现,前端确实外包给台积电,然后晶圆被运回钱德勒添加MRAM结构。

嵌入式应用

根据飞思卡尔的说法,这种 MRAM 技术的主要优点是它是传统 CMOS 的后端补充,因此适合嵌入式应用。这个精彩的序列似乎清楚地证明了这一点。

作为一种制造策略,我认为这也很有意义。它将晶圆成本降低到代工水平,并且还可以对投机性产品发布进行更严格的库存控制——保留前端晶圆的库存,仅根据订单量需要添加后端。

1.3 平方微米的 MRAM 单元尺寸与该代 SRAM 单元尺寸相当。目标市场之一是用于数据记录等应用的电池供电 SRAM 存储,并且该器件采用与 SRAM 兼容的引脚排列进行封装。

通过这一部分,飞思卡尔提出了一种在价格和性能方面可能存在一些缺点的技术。然而,作为一种需要零功耗存储数据的解决方案,它将在汽车、航空航天和类似市场中找到一些应用。