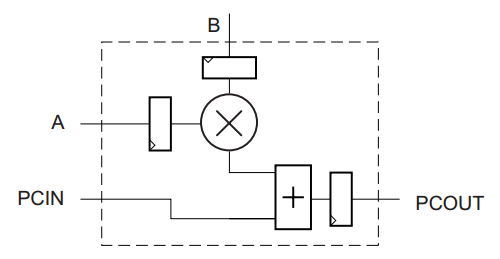

下面的图 6 显示了图 5 的 DSP Slice 的简化框图。

图6

这个简化的框图强调一个切片的输出可以作为输入路由到下一个切片的加法器/减法器。如果我们忽略图 6 中所示的输入

寄存器,图 6 的原理图与图 4 虚线框内的电路相同。因此,通过级联这些 DSP 切片,我们可以有效地实现图 4 的 F

IR 滤波器。在这种情况下,我们可以使用 FPGA 的通用结构切片来实现红色加法器(参见图 4)。

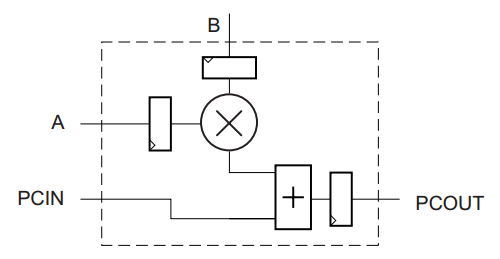

图 7. 基于 DSP48 的八抽头对称 FIR 滤波器实现。图片由

Xilinx提供。点击放大。

这里,阴影加法器实现了图 4 中的红色加法器,并且可以使用片内的寄存器来实现延迟线。