米勒频率补偿使得使用相当小的补偿电容C ?值成为可能。这是非常可取的,不仅因为C ?可以在芯片上制造,还因为它比分流电容补偿产生更快的动态。之所以如此,是因为转换速率、开环带宽和全功率带宽与C ?大致 成反比。

现在,就C ?的大小而言,一直到单位增益的闭环增益补偿是保守的。有许多应用涉及大于值的闭环增益,例如大于A min = 10 V/V,这将使用更小的 C ?并因此享受更快的动态。

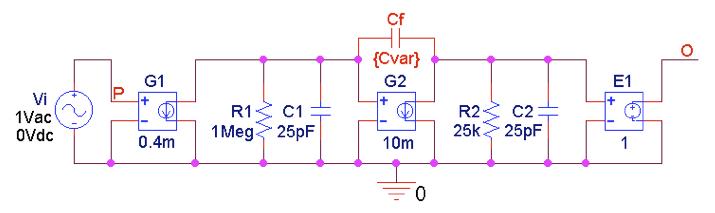

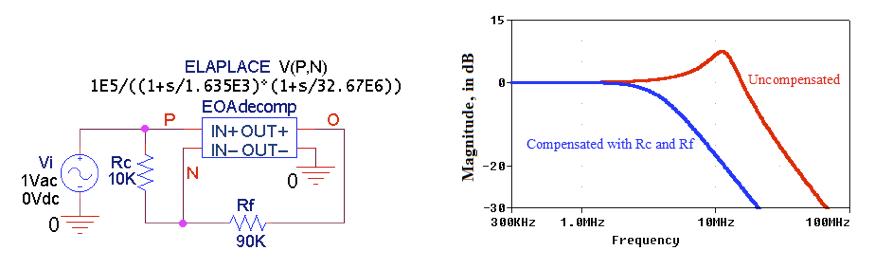

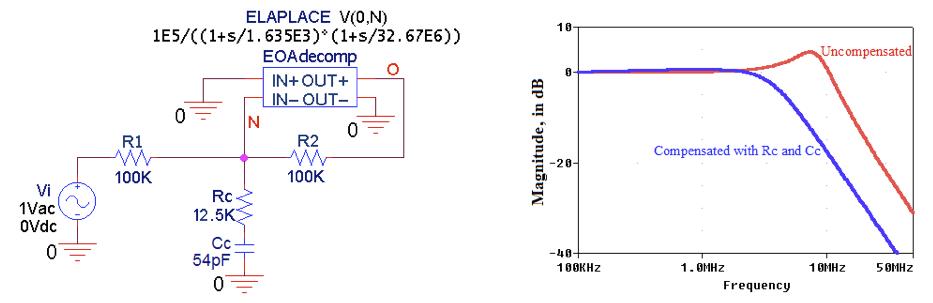

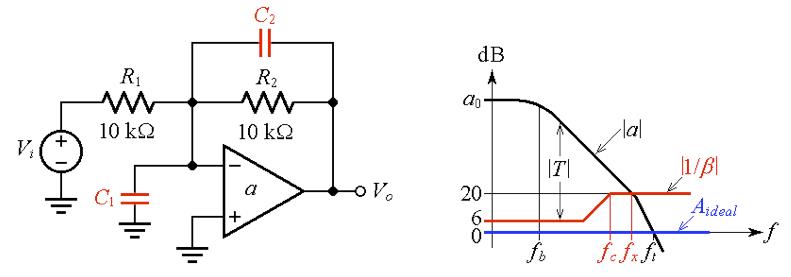

让我们使用运行的 PSpice 电路示例(在我关于运算放大器频率补偿的文章中首次介绍)来比较去补偿与完全补偿:

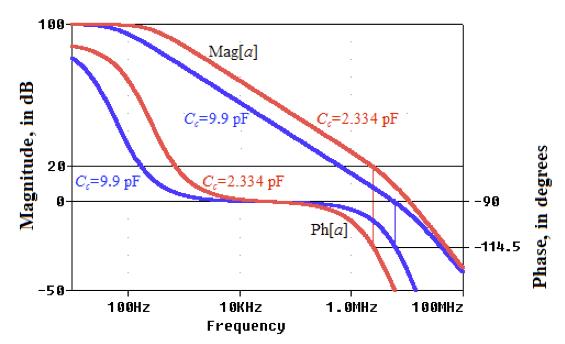

PSpice 的结果如下图所示:

结果得出以下观察结果:

现在让我们继续考虑如何使用外部因素在我们的电路中实现补偿;例如,电阻器。

尽管去补偿运算放大器旨在实现高于 A min(上例中 A min = 20 dB)的闭环增益,但它们出色的动态特性也使它们对于增益低于A min的应用也很有吸引力。

但这会降低相位裕度? m,因此用户有责任从外部补偿电路以将? m保持在所需水平。

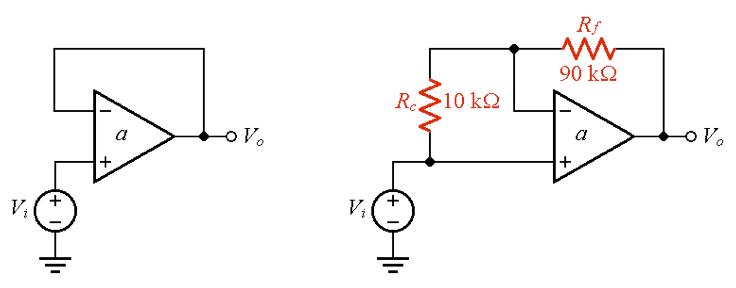

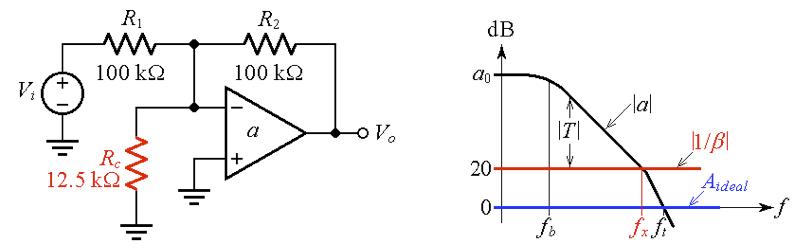

为了说明这一点,让我们以C ? = 2.334 pF的去补偿形式获取图 1 中的运算放大器,并将其配置为如图 3(a) 所示的电压跟随器操作。

如前所述,该电路的相位裕度仅为? m ≈ 24°。我们如何将它提高到? m = 65.5°?一个简单的解决方案是将其1/β曲线提高到 20 dB,同时仍然确保单位增益。我们通过以 1 比 9 的比例 连接电阻对Rc -R?来实现这一点,如图3(b)所示。理想化极限a → ∞中的闭环增益仍然是

(这种情况是因为对于a → ∞,运算放大器输入端子两端的电压趋于零。这意味着通过R c的电流为零,因此通过R ? 的电流也为零。因此, R ?两端的电压为零, 所以我们有V o = V i。)

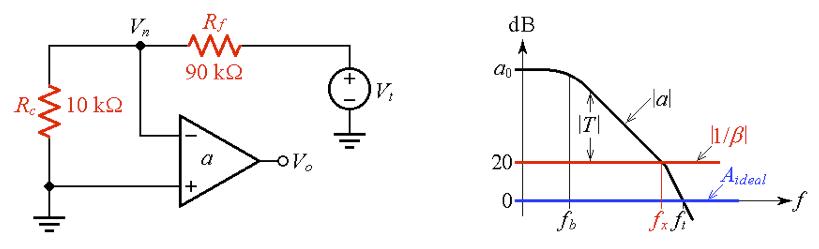

然而,我们通过图4(a)的测试电路找到的 反馈因子β 是

或1/β = 10 = 20 dB(注意1/β ≠本例中的 理想值) 。

响应如图 5 所示。

类似的推理适用于图6(a)的单位增益反相放大器 。

在这种情况下,在极限a → ∞中,我们有

通过检查,反馈因子现在是

在这种情况下,已选择R c以使 ( R 1 || R c ) = R 2 /9。

上述专门针对单位增益同相和反相放大器的讨论可以很容易地推广到闭环增益而非单位增益的情况,但仍然满足 1 < (1 + R 2 / R 1 ) < A min。

该电路是用作同相放大器(A ideal = 1 + R 2 /R 1)还是用作反相放大器(A ideal = – R 2 /R 1),只要满足条件(1 + R 2 /R 1 ) < A min成立,我们在运算放大器的输入端子上放置一个电阻R c ,例如 1 + R 2 /( R 1 || R c ) = 1 + R 2 /R 1 + R 2/R c = A分钟。

电阻补偿虽然简单,但有两个缺点:

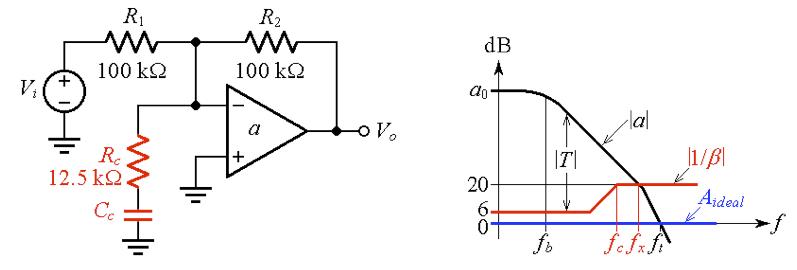

我们可以通过将合适的电容Cc与Rc串联来减轻电阻补偿的局限性,如图 7(a) 所示的 反相放大器。

请注意,为确保所需的相位裕度,我们需要仅在交叉频率? x附近将放大器引入所需的关闭率(ROC) ,而不一定一直到直流。

从物理上讲,1/β曲线在电容阻抗的大小等于R c或 |1/( j2πC c | = R c的频率? c处中断,给出

为了防止相位裕度? m的明显侵蚀,通常将? c放置在? x下方大约10 倍,或者

对于图7(a)的电路 ,这意味着C c ≈ 54 pF。图 8 的仿真产生? x = 2.38 MHz 和? m = 61° 的测量值。

输入滞后补偿因在闭环响应中产生零极点双峰而臭名昭著,除其他外,这会导致无法忍受的长稳定时间特性。Michael Steffes提出的替代补偿方法避免了这些缺点, 如图 9 所示。

我们已经在之前关于杂散输入电容补偿的文章中遇到过这种类型的电路,因此那里所做的许多考虑也适用于本电路,的区别是现在C 1是有意的。

我们有兴趣开发两个条件来指定C 1和C 2的值。在高频下, C 1和C 2的阻抗在幅度上远小于R 1和R 2,我们可以忽略R 1和R 2并声明在高频下我们有1/β → 1 + C 1 / C 2。

Imposing 1 + C 1 /C 2 = 20 dB = 10 为我们的电路示例提供了个条件

第二个条件源于这样一个事实

所以C 2的值取决于我们决定放置? c的位置。

Steffes的详细分析超出了本文的范围,我们在这里采用启发式方法,而不是应用它。

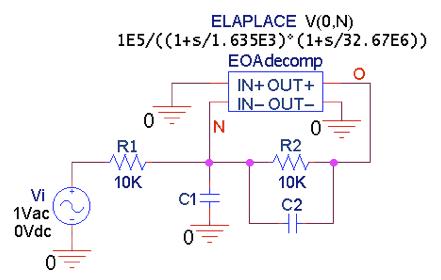

我们从等式 (6) 和 (8) 开始,并使用图 10 的 PSpice 电路观察交流响应,因为我们通过降低C 2逐渐增加? c,同时保持等式 (7) 的条件。

我们在 AC 响应刚开始出现峰值时停止。这种方法给出C 2 = 12 pF 和C 1 = 9 C 2 = 108 pF,从而产生图 11 中表现良好的响应。AC 响应具有 2.36 MHz 的 –3 dB 频率。

值得指出的是,通过将C 1的值更改为9C 2 – C n,可以将反相输入端存在的任何杂散电容C n纳入此补偿方案。因此,如果C n = 20 pF,那么我们使用C 1 = 88 pF。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。