在我们关于 VLSI 中的晶体管大小调整系列的续篇中,我们将介绍我们系列中的第三个也是一个模型,即线性延迟模型。如果您想了解线性 RC 延迟模型 和流行的Elmore 延迟模型,请务必查看之前的文章。

线性延迟模型提供了一种更简单的方法来模拟大型 RC 分布式电路的延迟,正如我们在上一篇文章末尾观察到的那样,Elmore 延迟变得复杂或不准确。

在本文中,我们将学习如何找到较大电路中晶体管/逻辑门的尺寸以提供所需的性能。

回想一下上一篇文章,我们使用 Elmore 延迟将等效 RC 电路模型线性化为:

tpd=(p+gh)3RC

其中 p = 寄生延迟。

通过这个表达式,我们可以计算出多级 MOS 电路的尺寸。

逻辑功是栅极的有效输入电容与反相器的输入电容之比。从这个意义上说,有效电容意味着输入端出现的电容。

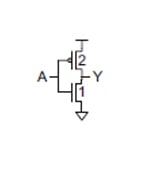

查看下图所示的反相器,其中 PMOS 的单位尺寸是 NMOS 的两倍,以提供相等的上升/下降时间。

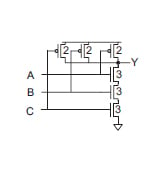

对于下图所示的 3 输入与非门,输入 B 处的电容为 (3C + 2C = 5C)。

因此合乎逻辑的努力是

这与上一篇文章中推导出的线性化延迟是一致的

对于逆变器

对于 NAND

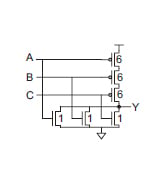

如果您应用相同的技术,下图中所示的 3 输入或非门将给出 的逻辑结果。

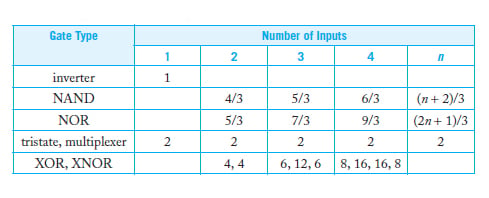

这种方法可用于计算其他常见逻辑门的逻辑努力,如下表所示。

表 1. 普通门的逻辑努力

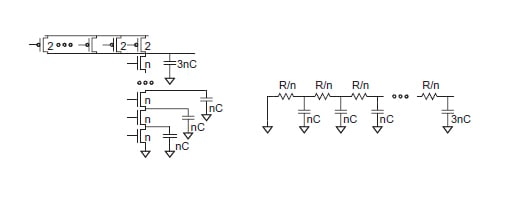

可以使用上一篇文章[链接]中描述的 Elmore 延迟或通过仿真来计算寄生延迟。为了简要总结寄生延迟的影响,考虑一个 N 输入 NAND 门,它的 Elmore 延迟等效值在下图中给出;

埃尔莫尔延迟是,

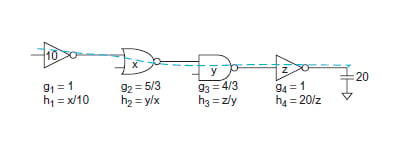

从表达式中可以看出,寄生延迟部分随串联晶体管的数量(n)呈二次方增加,这就是为什么建议级联两个较小的门以形成较大的门以减少门的输入寄生延迟。在多级逻辑网络中可以进一步观察到这一点的含义,它是路径中每延迟的总和,如下图所示的多级逻辑网络所示。

\[D=\sum{d_i} \; \;\textit{在哪里} \; \; d_i= g_ih_i+p_i\]

\[D=\sum{g_ih_i} + P \;\; \textit{哪里} \; g_ih_i = \textit{舞台效果}\]

路径电功 H 是路径的输出电容与路径的输入电容之比。

路径努力 F 是每个阶段的阶段努力的乘积。由于目标是达到延迟值,因此每个阶段将为 n 阶段关键路径贡献等量的阶段努力。要求每个阶段必须具有相等的阶段努力。因此,对于 N 级网络,级工作量很简单;

-----阶段努力

所以,

因此延迟表达式可以写成

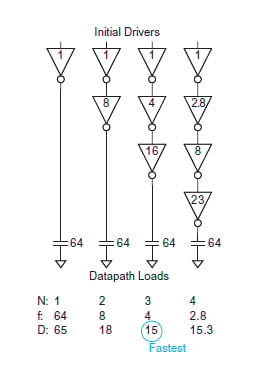

为了更好地理解这个概念如何应用于实际系统,我们将考虑通过逆变器驱动 64 个电容单位所需的功能单元。了解逻辑工作量后,我们可以确定阶段数以提供延迟。

请注意,反相器的寄生延迟为1,因此对于N级反相器链网络,路径的总寄生延迟P将是每个反相器的寄生延迟之和,即N。

| N = 1 | N = 2 | N = 3 | N = 4 |

|---|---|---|---|

由于三级反相器设计是延迟的设计,因此我们要确定每反相器的大小以给出延迟。

由于每个阶段的努力 ,因此靠近负载电容的个反相器的大小为,

中间反相器导出为

虽然输入端个反相器的大小推导为,

每个阶段的总结如上图 6 所示。可以观察到,单级逆变器网络提供了的延迟,即使电路的整体尺寸,设计也会运行得非常慢。虽然 3 级设计的面积更大,但它为设计提供了延迟量,从而使系统按照规范工作。

至此,我们已经能够研究MOS电路中的各种延迟模型。虽然这些方法简单且相当准确,但在准确性至关重要的情况下,它们不能完全替代 CAD 工具。然而,这些方法适合提供一种快速而粗略的方法来深入了解各种电路拓扑和关键路径设计。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。