也就是说,Delft University of Technology 与 Goodix Technology 合作,似乎凭借 0.18μm BCD 原型 IC 达到了 120.9dB 动态范围和 -111.2dB 峰值 THD+N 的高保真数字。

在全功率 (10% THD) 时,它可以以 90% 的效率向 8Ω 提供 13W,或者以 86% 的效率向 4Ω 提供 23W。

具有讽刺意味的是,尽管有数字输入,但它在内心深处求助于模拟信号。

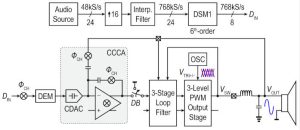

在前端,电容性 DAC 用于避免电流控制或电阻性 DAC 出现的热噪声和 1/f 噪声。

这会驱动基于电容耦合斩波

放大器拓扑结构的闭环 D 类放大器。

由于 DAC 输出包含采样频率倍数附近的 DAC 图像以及整形量化噪声,因此需要注意频率规划,以防止 DAC 输出与各种斩波和 PWM 音调之间的互调。

24 位输入被上采样到 768kHz(16×48kHz),通过数字 ΔΣ 调制器降低到 8 位,然后 DAC 将其转换为模拟信号,供斩波放大器和 D 类放大器的其余部分使用,D 类放大器具有 4.992MHz从 14.4V 轨运行的三级 PWM 输出。该频率是斩波频率的第 13 次谐波(因此是奇数),避免了边带的互调。

“然而,这也意味着 PWM 频率不位于采样频率的倍数 [它是 6.5x],因此会发生一些量化噪声折叠,”Delft 说。“幸运的是,PWM 频率附近的量化噪声被 DAC 频谱的 sinc 滚降和低通特性衰减,因此折叠噪声可以忽略不计。”

原型为 7.5mm 2,在单独的 FPGA 中带有插值

滤波器和数字 ΔΣ 调制器。

高动态范围

运算放大器使用斩波放大器的问题

同样由代尔夫特理工大学撰写的 ISSCC 会议的下一篇论文深入研究了在高动态范围运算放大器中使用斩波放大器的问题,这是由于输入和输出

开关同时转换而信号需要有限的时间通过放大器。

这会导致输出的斩波时间略微错误,从而导致类似尖峰的输出错误。

使用两个并联斩波放大器,正交斩波,并交替选择它们的输出,远离斩波时刻,可以消除这些尖峰。

代尔夫特使用了一个原始质量的斩波放大器,然后只在主放大器的斩波点周围短暂使用了并行放大器,允许并行放大器的 1/f 噪声和偏移规格在不降低整体质量的情况下放宽,并且大多数时候可以关闭次级放大器以节省电量。

该团队采用0.18μm BCD 工艺在 0.57mm 2上构建放大器,5V 时消耗 620μA,选择次级放大器后降至 530μA。

将运算放大器作为缓冲器连接后,单个 1Vrms 79kHz(~4x Fchop)输入会在 1kHz(4xFchop – Fin)时引起 -125.7dB IMD 音调,如果主放大器使用 100%,则在 -102dB 时会更糟的时间。

39kHz Fin(~2x Fchop)处的数字为 -128.5dB,恶化至 112.8dB。

在 Fin <5kHz 时,IMD 音调低于 -140dB 本底噪声。

输入电流为 22.6pA。

ISSCC 2023 论文 3.1 A 120.9dB DR,-111.2dB THD+N 数字输入电容耦合斩波 D 类

音频放大器 ISSCC 2023 论文 3.2 具有松弛填充技术和 22.6pA 输入电流的斩波稳定放大器

每年在旧金山举行的 IEEE 国际固态电路会议是基于 IC 的模拟、数字和射频电路的世界展示。它为 IC 和电路设计工程师提供了一个保持技术流行并与建立联系的机会。