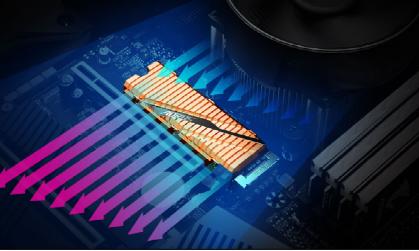

ADAS高功耗、低效率所带来的能源危机

新能源车发热和能耗问题

根据中国国家应急管理部门统计,2022年季度,智能汽车发生自燃的事故一共发生了640起,平均1天有7辆电动车发生自燃。电动车起火的原因主要是以下几点:电池过热、电池老化、电池遭受碰撞、高负荷运行等等。其中,电池的高负荷运行是严重的原因之一。

视觉算法算力的高功耗和低效率

随着特斯拉通过视觉算法来实现自动驾驶。各大Tier 1大厂纷纷进入算力的军备竞赛,算力不断加大,较大的算力需要消耗较高的功耗。

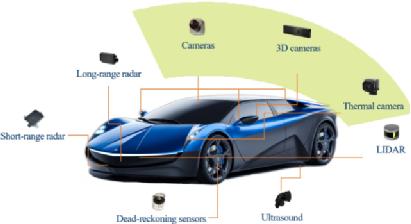

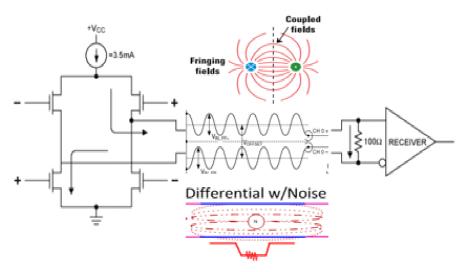

图1 视觉算法引发功率消耗问题

ADAS的多

传感器融合策略

实际上自动驾驶领域,变化的区域占整个图像的很小一部分,大部分视觉数据是无用数据。传统的视觉处理花费了大量精力来处理这些无用的背景,这浪费了大量的算力和时间。采用事件处理系统,通过时间系统触发判断方式,可以提高100-1000倍的处理速度,减少运算量。

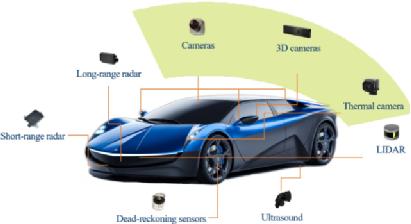

图2 多传感器融合技术策略

事件相机无法提供深度信息,目前依靠相机的计算方式还属于简单的蛮力计算。采用事件相机结合激光雷达、毫米波雷达、超声波雷达等方式就可以实现完美的3D感知。同时,也可以避免依靠海量数据和海量算力造成的资源浪费。

ADAS域架构多传感器融合技术

多传感器同步问题

图像事件系统能解决视觉识别的大部分算法,但是,它也存在一些局限性。除了传统的图像算法,激光雷达、毫米波雷达、超声波雷达也越来越多地被用于ADAS。随着ADAS的智能化要求的不断提高,自动驾驶系统需要采用多个不同类型的传感器协同处理的方式实现。

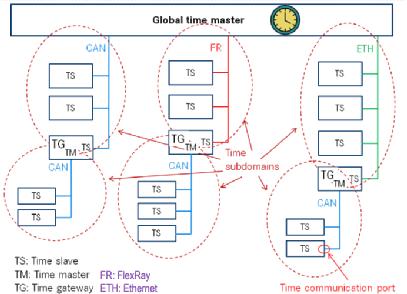

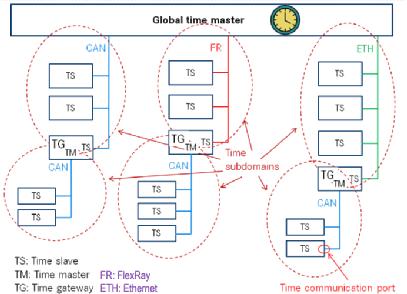

图3 多传感器融合面临时间延迟的挑战

各传感器采集数据,然后通过总线发送给域控制器,存在一定程度的延时,并且,各传感器延时的时长不固定。为了提高自动驾驶的传感器之间的深度融合、决策规划和融合定位等性能,自动驾驶域控制器与其关联的传感器均需要做时间同步。

常用的时间同步主要包括:GPS同步、SyncE、NTP和PTP(IEEE 1588)时间同步。对于ADAS来说,主要采用的是时间敏感网络TSN(Time Sensitive Network)技术。

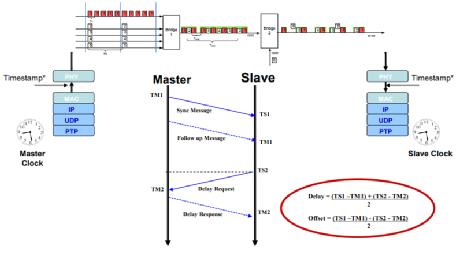

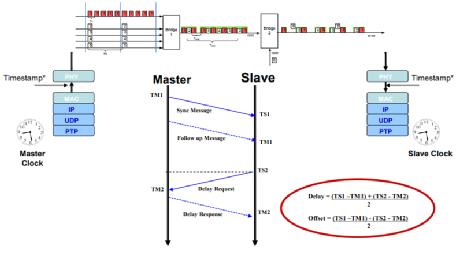

图4 时间敏网络技术TSN原理

TSN初来源于音视频领域Ethernet AVB的应用需求,用于解决音视频网络的高带宽、高实时性、和高传输质量的需求。TSN的原理是基于时间流量调度和管理,通过TSN网络中的时间感知整形器TAS(Time Aware Shaper)的调度来实现的。

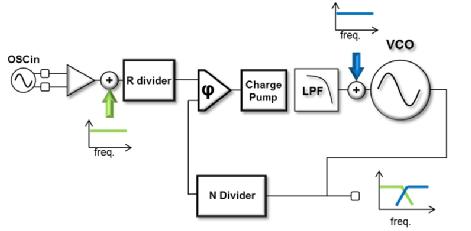

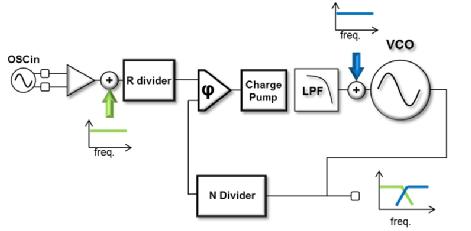

图5 采用锁相环技术实现时钟频率相位锁定

TSN可以比较的计算出传输线的时延问题。但是,如果主从设备采用自己独立的时钟,还会存在频偏问题,这就需要采用精度非常高的

晶振来实现传输功能。基于成本等综合考虑,通常采用OCXO/VCXO+PLL的方式实现从设备时钟的频率锁定,与主时钟实现频率同步。

在ADAS应用中,采用TSN结合OCXO+锁相环的方式,就可以实现各传感单元和GPU/FPGA的时间同步,消除累计误差,实现时钟源的统一和多传感器完全融合。

传感器高速数据交换问题

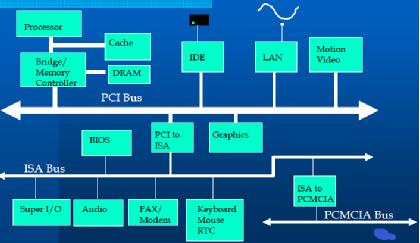

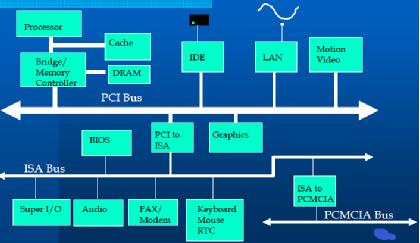

图像事件系统含有海量数据,要满足多传感器深度融合,这些数据就必须要在极短时间完成信息交换。受流线型处理器启发,人们一直采用独立于处理器的32位或64位局部总线。该总线工作频率为33MHz/66MHz,峰值速度达533MB/s。这种总线被称为外设互联标准总线(PCI总线)。

图6 PCI总线架构框图

后来,在PCI总线的基础上,又衍生出PCI-X总线协议,其工作频率提高到133MHz,峰值带宽达到1064MB/s。再后来,又发展到PCI-X 2.0。

PCI总线在发展到PCI-X 2.0之后,传输速率很难做进一步的提升。这是因为,时钟和数据信号之间的传输线寄生电感形成串扰,严重影响数据信号的波形,很容易对采样信号形成误判,影响通信效率。

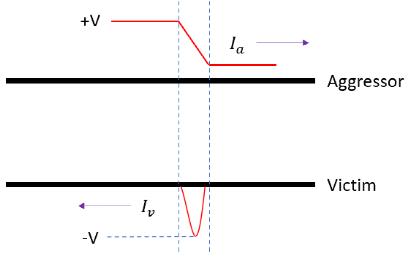

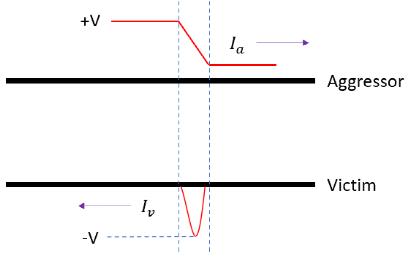

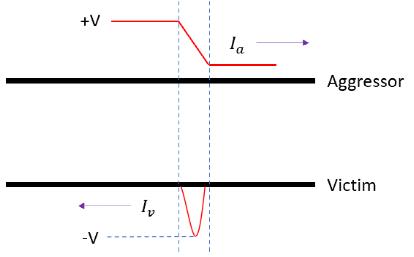

图7 高速数字信号引发的码间干扰

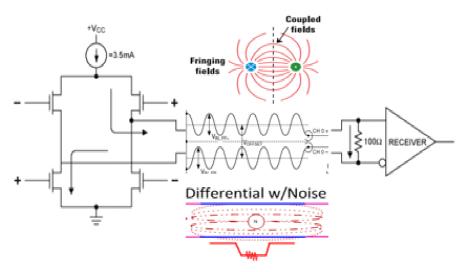

数字信号在高速传输的时候,很容易产生天线效应,向周围辐射,产生电磁感应,形成码间干扰。码间干扰,包括感染源信号和被干扰信号。这导致传输信号判决门槛的不断提高。为了提高抗码间干扰问题,有人提出采用差分传输模型。

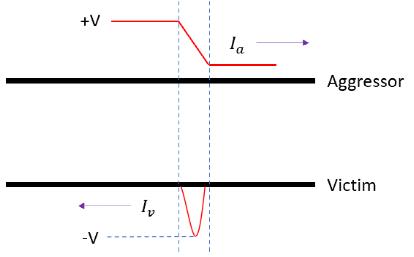

图8 差分信号消除码间干扰

这种差分信号传输方法,后来经过一系列演变和改进,发展成后来的USB和PCIe传输总线,PCIe总线经过迭代,现在已经演进到现在都PCIe5.0,根据消息,PCIe刚刚已经发布PCIe6.0和PCIe7.0规范。

图9 PCIe总线技术提升传输速率

不同技术算力的功耗对比

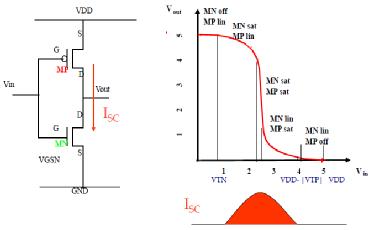

基于SRAM工艺的动态功耗

目前,市面上大部分视觉算法处理系统都是基于GPU和FPGA实现的,这些处理器大部分都是基于静态随机存储器工艺为单元。

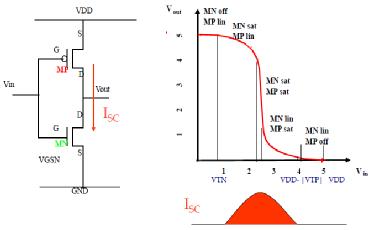

图10 SRAM单元内部架构

SRAM单元用六只N沟道CMOS管组成,其中四个CMOS管组成基本RS触发器,用于记忆二进制代码,另外两个做门控开关,控制触发器和位线。

图11 SRAM架构动态功耗

由于SRAM的上管和下管都是工作在深度饱和状态。所以,CMOS反相器从一种稳定工作状态转变到另一种稳定工作状态时,会出现上下管同时导通的情况。此时,CMOS的内阻非常小,此时对应的电流会非常大,所以,产生的动态功耗非常大。

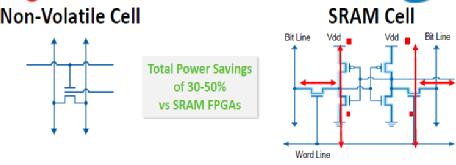

基于Flash工艺的动态功耗

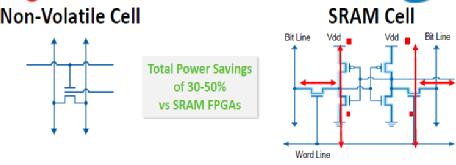

除了基于CMOS的SRAM处理器之外,Excelpoint世健的工程师Wolfe Yu介绍了Microchip推出的一种基于叠栅MOS的Flash架构FPGA处理器。

图12 Flash架构FPGA与SRAM架构FPGA的差别

Flash架构的FPGA的一个特点,工作点是静态的,动态切换也不会出现大的电流波动,可以节约高达50%的功率损耗。Wolfe表示MicrochipPolarFire与同类器件28nm产品相比,其算力能做到其他器件2.6 倍GOPS/W。

Microchip基于ADAS技术一揽子解决方案

在政策、互联网跨界竞争、消费者内在需求等因素驱动下,ADAS渗透率将快速提升。也有一些低端车型,也开始搭载部分ADAS功能,提升卖点。

Microchip基于时间敏感网络解决方案

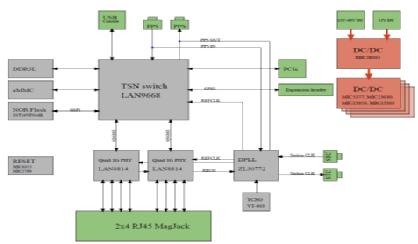

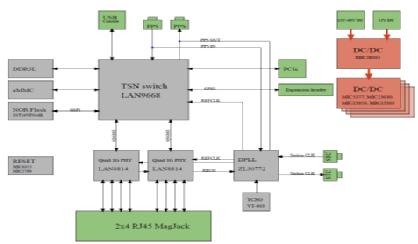

Microchip推出LAN937X系列TSN交换器件。作为业界符合IEEE 802.1AS标准的功能的交换解决方案,可实现更低延迟的数据流量和更高的时钟精度。下一步,Microchip还会推出集成1000 BASE TI PHY的LAN969X系列产品。

TSN可以实现网络传输延迟,但是,由于时钟晶体存在频偏差异,可能引发不同节点之间的频率误差,为了解决频偏问题,人们通常会在节点中,采用PLL锁相环和VCXO来锁定时钟频率。同时,为了更进一步同步GPS的1PPS时钟,还需要同步1PPS时钟。Microchip的ZL307XX系列集成5个PLL ,支持1PPS,SYNCE。满足大部分以太网时间同步要求。目前,Microchip已经和部分车企展开合作,开始评估Microchip的时钟解决方案。

图13 Microchip TSN解决方案

LAN93XX搭配1000BASE-T1 PHY LAN887X,配合同步数字锁相环 ZL307XX的计时的IEEE 1588v2和IEEE 802.1AS-2020、用于多传感器时间同步,符合IEEE P802.1Qci、IEEE P802.1Qav等,可以满足ADAS实时联网的需求。针对低端市场,Microchip的LAN937X配合100BASE-T1 LAN8770,也可以满足客户需求。

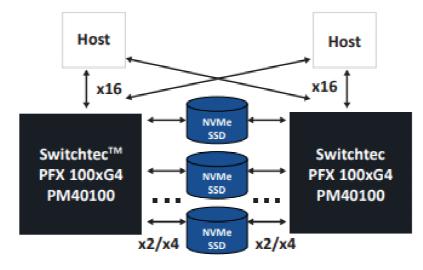

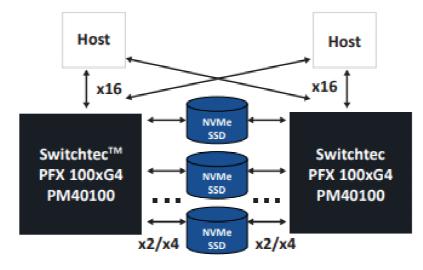

Microchip首款车用PCIe交换机介绍

2022年2月,Microchip宣布推出市场上首款汽车级的PCIe交换机PM430XX/PM440XX。新发布的PFX、PSX和PAX交换机解决方案为ADAS提供了的计算互连能力,第4代PCIe交换机提供高速互连,支持ADAS架构中的分布式实时安全关键数据处理。

图14 Microchip PCIe SWITCH解决方案

Microchip基于FLASH工艺的低功耗FPGA介绍

因为Microchip所采用Flash工艺这一独特的工艺制程,其功耗多只有相同制式的FPGA的50%。

在ADAS机器视觉算法应用中,采用Microchip的FPGA做摄像头前端采样、预处理,图像拼接等应用中,有着很好的表现。

Microchip带功能安全的PolarFire FPGA系列内置安全加密、可以保护设计、数据、网络不受攻击,Flash自带SEU免疫性能的FPGA,是数据中心、工业、汽车和航空航天应用的理想之选。

图15 Microchip基于Flash工艺FPGA与友商的功耗比较

除此之外,Microchip集成功能安全的MCU、DCDC、USB HUB、AES加密芯片,以及诸如CAN、LIN总线等,也是ADAS和汽车行业应用的主流方案。针对Microchip基于ADAS技术一揽子解决方案,Excelpoint世健都提供相应的技术支持和指导,降低视觉算法算力的功耗,提高效率,助力自动驾驶技术发展。