本应用笔记将介绍带有异步抽取滤波器的音频模数转换。它提出了转换过程对高频系统时钟的要求,并提出了这种音频转换的解决方案。

介绍

现代高性能 delta-sigma 模数 (A/D) 和数模 (D/A) 音频转换系统需要高频系统时钟(主时钟)用于其转换过程,通常超过 12 MHz .该时钟上的抖动是这些系统性能下降的一个重要来源。在包含转换器和基于晶体的时钟的产品中,这通常不是问题。然而,这在网络音频系统中可能是一个特别难以解决的问题,录音系统是转换节点和网络以采样率或在同一时钟域内运行。在这些系统中恢复低抖动主时钟的 常见方法是使用锁相环 (PLL)。PLL 电路有多种形式,各有优势。然而,

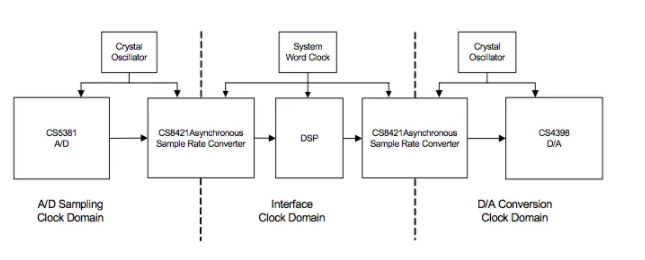

另一种方法是创建一个系统架构,其中 A/D 和 D/A 转换节点在独立于网络或系统时钟域的本地时钟域内运行。使用采样率转换器 (SRC) 可以轻松实现具有独立时钟域的系统,如图 1 所示。该架构还允许转换过程以固定采样率运行,该采样率始终高于网络或接口采样率。这种方法的基本优点是转换过程不受接口时钟抖动的影响,并由本地无抖动晶体振荡器控制。

具有独立时钟域的音频系统架构

CRD5381概述

CRD5381 是一种 4 通道参考设计,它结合了 CS5381 模数转换器和 CS8421 异步采样率转换器,以创建本应用笔记中所述的模数转换系统。CRD5381 本质上是一种 2 通道设计,其中已复制 2 通道模块以创建第 3 和第 4 通道。每个 2 通道部分包括所需的模拟输入缓冲器、CS5381 A/D 转换器和 CS8421 异步采样率转换器。该参考设计还包括时钟生成、状态 和所需的系统复位功能。此外,双 CS8421 器件可以配置为 4 通道时分复用 (TDM) 接口。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。