某些应用(例如ADC测试和校准)要求DAC具有极好的分辨率,单调性, 和分辨率。在这些性能类别中,图1中的电路很难被击败。其典型规格如下:

分辨率= 32位= 3×10–10= 1.2 nV = 192 dB。

DNL(微分非线性)= 27位= 400 nV = 162 dB。

INL(积分非线性)= 22位= 1.6 ?V = 130 dB。

满量程 (未加边框)= 11位=±2.5 mV = 66 dB。

零 = 23位=±500 nV±10 nV /°C = 140 dB。

纹波和噪声= 21位= 2 ?V pp = 128 dB。

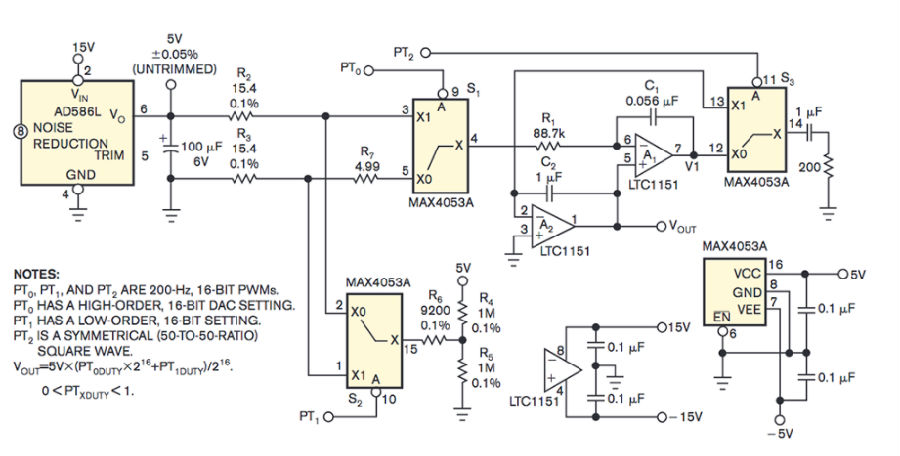

图1该DAC电路使用精密模拟开关将两个16位PWM信号求和,以实现32位分辨率。

DAC的32位分辨率的基础是模拟开关S1和S2以及精密电阻网络R2至R6对两个16位PWM信号求和。DAC的单调性和DNL在理论上是无限的,并且,在实践中, 的限制是1到216比R2:(R6+ R5+ RS2-ON)和R3:(R6+ R4+ RS2-ON)。0.1%电阻器的典型 可产生约0.1 ppm = 27位的DNL。

AD586基准电压源的输出阻抗小于0.1Ω,斩波稳定的“零漂移”放大器A1的130dB CMR(共模抑制)主要限制了INL。R7抑制了RS1-ON中的不对称性引起的潜在贡献,从而产生了大约0.3 ppm = 22位的典型INL。

由于LTC1151 A1和A2运算放大器的出色规格以及MAX4053A S2的电荷注入性能:约0.4 ppm或23位,因此零 和输出噪声规范处于低微伏级。

AD586L 5V基准电压源的未调整误差为±500 ppm,这限制了 。如果您的设计需要更高的 ,则可以使用ADI公司的简单调整电路对其进行进一步的调整。所建议的200 Hz PWM周期并不重要。您只需更改R1和C1即可适应任何方便的频率。R1C1时间常数与PWM周期时间的接近程度决定了A1-S2-A2同步“零纹波”积分保持滤波器的建立时间,并且 快可达到一个周期如果匹配正确。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。