随着对功能丰富的手机的需求日益增长,单片机开发中具有特殊应用性能的模拟开关继续受到 终设计的青睐。这不仅会降低材料成本(BOM),而且有助于提高设计性能并满足上市时间要求。本文将指导单片机开发系统设计人员完成几个实际使用 ,以减少爆音,检测充电器。

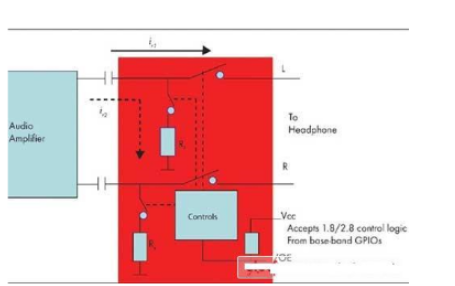

对于单片机开发设计人员而言,由涌入电流引起的冲击噪声仍然是艰巨的挑战,特别是当 终用户启动音乐和通话功能之间的切换时。只要 终用户打开音乐功能,这种烦人的声音就会给人不愉快的体验。如图1所示,当音频放大器工作时,通过交流耦合电容器的开/关浪涌电流是?冲击噪声的根源,音频共模电压将急剧上升。

当今市场上有多种解决方案可用。其中之一是添加一个额外的放大器,以使音频输出具有“0V”偏移?,从而很大程度地减小了紧接耳机之前的交流耦合电容器的尺寸。因为大多数耳机放大器都集成在基带处理器或电源管理单元(PMU)中,所以添加此放大器不仅会增加材料成本,而且会增加功耗。

此开关非常适合通过单个USB连接器(D+/D针)与耳机和USB数据线共享的手机和MP3/MP4播放器。低的总谐波失真(THD)对于音频通道非常重要。另外,由于开关放置在交流耦合电容器之后,因此必须处理低THD时较大的反向信号摆幅。该开关的超低关断电容器允许通过设备“有线”连接高速USB信号。较低的寄生电容也是Hi-Speed一致性测试的关键USB2.0标准。

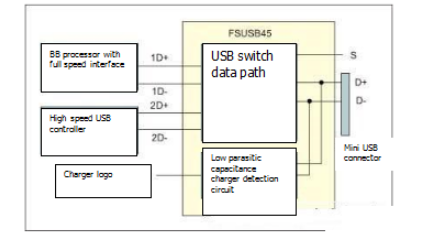

随着当前市场趋势转移到单个USB充电器/数据端口?,特殊应用的USB开关已成为具有充电器检测功能的手机设计中的常用配置。图2是此类交换机应用程序的示例。

基于两个主要原因,在此设计中需要低导通电容开关。首先,由于基带处理器和高速?当手机进入高速模式时,USB?控制器输出在连接器侧共享相同的D+/D-引脚USB2.0模式(例如音乐 或闪存功能),必须降低基带USB1.1/。2.0全速控制器的输出电容。D+/D-线上的任何附加电容都会损坏Hi-Speed的眼图USB信号。其次,在高速USB模式下,必须切断D+/D-线上的多余走线,以有效避免480MbpsUSB信号快速上升/下降沿引起的信号反射。

由于单个USB端口用于充电器和数据功能,因此充电器检测功能在当前设计中已变得非常流行。传统方法是将D+/D-线馈入内部A/D转换器,以确定D+/D-线是否短路。如前所述,该方案的主要局限性在于基带处理器的GPIO端口的高输入电容会在数据线上增加额外的电容电抗。这种新的容抗将导致在高数据速率下有效触发信号。不良影响,属于USB2.0一致性测试(例如,对于USB2.0信号为480Mbps)。当然,该方法的另一个缺点是它也占用了系统A/D转换器的资源。

在这些应用中,需要具有超低内部电容检测电路的USB开关来实现充电器隔离和全速USB控制器输出电容器的隔离。同时,用于确定将哪个USB通道用作输出的USB通道选择引脚(图2中的S引脚)必须识别1.8V和3V逻辑输入(注意:基带中的1.8V和3V处理器的GPIO输出非常普遍)。

传统的开关选择引脚接受高达2.0V的输入“高”(Vih)电平(TTL逻辑),当直接从电池中获取开关电源(VCC)时,会导致严重的泄漏电流。能够识别1.8V输入逻辑电平的能力也消除了对外部电平转换设备的需求,从而使单片机开发设计人员能够进一步降低材料成本。例如,飞兆半导体的FSUSB45和其他IC具有超低导通电容(7pF)和小尺寸(1.4×1.8mm),以及充电器检测和1.8V控制逻辑识别,可以很好地满足USB数据路径开关设计的需求。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。