随着我国电力事业的快速发展,电力系统对发、输、配、用电量的采集也有了更高的要求。电量采集作为电力系统实时控制、监测、调度自动化的前提环节,毫无疑问具有重要的作用。但在电量采集过程中,由于存在谐波等干扰因素,因此如何准确、快速地采集电力系统中的各个模拟量一直是电力系统研究中的热点。

根据采样信号的不同,采样可分为直流采样和交流采样两大类。直流采样算法简单、便于滤波,但维护复杂、延时较长、无法实现实时信号采集,因而在电力系统中的应用越来越受到限制。交流采样实时性好、相位失真小、投资少、便于维护,其缺点是算法复杂、对A/D转换速度和CPU处理速度的要求较高。随着微机技术的发展,交流采样有逐步取代直流采样的趋势。近年来,各种集成化单片DSP的性能得到很大的改善,价格大幅度下滑,越来越多的单片机用户开始选用DSP器件来提高产品性能。本文以TI公司新推出的2000系列DSP(TMS320F2812)为例探讨DSP在电力系统交流采样中的应用。

1总体设计

励磁装置的电量采集除发电机定子机端电压、电流外,励磁电压、励磁电流及母线电压也需一并考虑在一起,共九路模拟量。为了提高可靠性,还需加上第二组仪表PT时,则要采集的模拟通道数将增加为12路。因此需要从采样 、速度及经济成本等多个方面权衡,选择合适的采样方式和采样频率,并注意强弱电的隔离和电磁干扰,从而确定 终的软、硬件设计和元器件选择。参考文献[4]中详细地分析了影响软件同步采样 和硬件同步采样 的因素及改进措施。本系统采样模块利用硬件同步采样方式,并通过硬件锁相环同步环节直接控制采样保持电路来获得更高的同步 。为了使采样信号f*(t)能反映被采样的模拟信号f(t),采样频率必须满足采样定理,即采样频率fs必须大于模拟量所含 次有效谐波频率fmax的两倍。实际采样时一般使fs≥10fmax,以保证采样信号能够准确地代表被采样的模拟信号。采样频率过高时,会增加处理器的负担,影响实时性。本系统设计时初步定为40点,即采样频率为2kHz左右。

2采样系统的硬件设计

交流采样模块的硬件结构如图1所示,它包括隔离变换电路、通道选择电路、限幅电路、同步方波变换电路、模/数转换及控制电路等。

隔离变换电路中利用带有磁补偿的霍尔传感器将相关PT、CT送来的电压、电流信号转换为同波形A/D通道允许的弱电电压信号。通道选择电路利用两片2选1模拟多路选择器MC14053B,通过不同的编址选出不同的A、B两组,同时采样六通道模拟量。这两部分电路比较简单,不予详述。

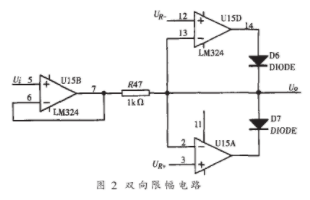

2.1限幅电路

在模/数转换中,如果A/D转换器损坏,检测和控制的功能就不能实现。出于安全考虑,在A/D转换器前采用限幅电路,以保障系统的A/D转换器安全。传统的限幅器如齐纳二极管限幅器、稳压管反向限幅器、桥式限幅器等,都是利用二极管的击穿特性限幅。在击穿区由于二极管内阻并不为零,并有漏电流存在,所以稳压值并非恒定而且不易调节。本系统所设计的限幅电路如图2所示,设定UR=±2.5V,由TL431提供高 的基准电平。

2.2同步方波变换电路及频率采样

为了保证励磁装置采样的 ,必须使采样频率具有快速的自适应能力,同步跟踪机端电量的频率变化。如图3所示,所设计的同步方波变换电路由迟滞电压比较电路、高速光耦、锁相倍频电路和脉冲整形电路组成。其中,由U1A(LM339的1/4)和Q1(9012)组成的迟滞比较电路将正弦波输入信号变为0~5V的同频率方波信号,同时利用迟滞电压特性消除输入信号在过零点可能出现的抖动现象。高速光耦6N137把模拟部分和数字部分电路隔离开,同时进一步隔离了强弱电之间的电气连接。锁相倍频电路由锁相环电路U2(CD4046)和十进制分频电路CD4017组成,按每周波采样40点计算,两片CD4017完成40分频。由于锁相环的相位负反馈作用,当锁相环锁定时(D5为锁定指示灯),U6_7的输出信号与U2_14的输入信号同步,也即与正弦输入信号同步,此时U2_4的输出信号频率为正弦信号频率的40倍,并且跟随其同步变化。

U6_7输出的同步信号经分压后,被送入TMS320F2812的捕获模块CAP1,用于频率的测量,以满足励磁控制中后续的电力系统稳定器(PSS)和V/F限制的需要。U2_4输出的同步倍频信号经CD4528脉宽整形后得到合适的脉冲信号,作为A/D采样保持的触发信号。本采样模块通过硬件锁相同步,避免了软件同步中的中断响应时间不确定性,可以获得更高的同步 。如果需要改变每周波采样的点数,仅需改变CD4017引脚复位的连线即可。

2.3模/数转换及控制电路

TMS320F2812芯片上有一个12位、转换频率为25MHz的A/D转换器,其前端为两个8选1的多路切换器和两路同时采样/保持器,在要求不很高时完全可利用其构成同步顺序采样电路,或者增加外部采样保持器后构成同步采样。考虑到发电机励磁控制装置电量检测的重要性和其对电量采集 、速度的较高要求,本系统采样模块中选用了外置的六通道16位模/数转换器ADS8364。其内部包括六个高速采样-保持放大器、六个高速ADC、一个参考电压源及三个参考电压缓冲器,可以提供250kSPS的同步采样率,还可提供具有超低功耗(69mW/每通道)的所有六个输入通道的转换,这样使得所有通道的单位成本均较低[5]。并且六个通道的数据输出接口电压介于2.7V到5.5V之间,便于与DSP直接接口,省去了中间的电平转换。六个完全独立的ADC可大大提高硬件整体的并行处理速度,在50kHz输入信号下仍可保证大于80dB的卓越共模抑制能力,特别适合于诸如发动机控制及能量转换等高干扰环境中。图4所示为模/数转换及控制电路,ADS8364的每通道的差分输入V+IN都需经比例运算放大器和电平自举电路将双极性交流信号转换为0~5V的信号。A/D转换器的 时钟频率为5MHz,由TMS320F2812的PWM1口提供,ADD和BYTE位设为低电平,IOPF0控制ADS8364的复位启动,三对(六通道)采样保持触发信号来源于同步倍频的输出信号HOLD,每对通道转换完毕后由EOC向XINT1发出外部中断请求,TMS320F2812响应中断请求后,通过地址线选通对应通道,将转换所得数据由数据线读入。

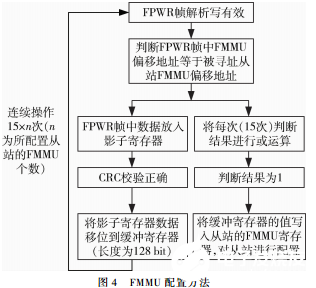

3采样系统的软件设计

本采样系统的软件结构较为复杂,涉及的算法也较多,为了便于调试和维护,软件设计遵循模块化、自顶向下、逐步细化的编程思想。软件采用C语言和汇编语言混合编程,主要软件可划分为主程序、采样中断服务子程序、频率捕获中断服务子程序三大模块。图5所示是主程序流程图,软件的工作过程是:系统上电复位后,首先按照所选定的模式(调试时为JumptoH0SRAM模式,实际应用时为JumptoFlash模式)自举加载程序,跳转到主程序入口;然后进行相关变量、数据缓冲区、控制寄存器、状态寄存器的初始化;调用事件管理器EV初始化程序,设定PWM1的周期(5MHz)、占空比,捕获单元CAP1时基T2的输入时钟分频数、周期,并启动T1、T2;初始化外设扩展中断PIE,使能所用到的外部中断XINT1和捕获中断,清中断标志位,开全局中断;而后复位并初始化外部的ADS8364,等待外部中断,在中断服务子程序中将A/D转换后所得数据读入所分配的数据缓冲区,待周波采样完毕后,根据原通道采样物理量(交流、直流)调用不同的数字滤波程序,对数据处理后,调用各计算子程序,计算所需的有效值、有功功率、无功功率、功率因数、平均值。采样中断子程序和频率捕获中断服务子程序的流程图如图6所示,其中频率捕获中断的时基 为0.43μs。TMS320F2812为定点DSP,为了提高运算的 和速度,软件设计中充分利用TI公司提供的IQmathLibrary以实现浮点运算与定点程序代码的无缝接口,简化了程序的开发,并大大提高了程序运行的实时性。

本文所设计的同步采样模块已经通过各种功能测试,达到了预期的目标。该方案的硬件设计和软件编程对提高能源、冶金等行业中多通道电量同步采集的速度和 有一定的借鉴意义。其中的子程序具有良好的可移植性,对其它DSP应用系统的设计也有一定的参考价值。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。