锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

图1.锁相环框图

图1所示为基于PLL的频率合成器框图。VCO生成输出信号。通过PLL将其保持在设定频率,并锁定到基准频率。基准频率通常由非常精准的石英振荡器提供。在锁相环电路的反馈路径部分,在鉴相器前通过分频器提供可调的VCO分频比。

VCO包含可调的调谐元件,例如电容随输入电压改变的变容二极管。因此,PLL电路可以算一种VCO反馈控制系统。VCO所需的输入或控制电压通常高于提供给PLL电路的电源电压。电源电压一般为3.3 V或5 V,而VCO根据频率需求可能需要高于20 V的电压。要生成范围更广泛的频率,可以使用具备更广泛调谐范围的VCO。图2显示了支持千兆赫范围VCO的简单电路示例。

VCO可以使用Synergy Microwave Corporation的DCYS100200-12。该产品在28 V (VTUNE)时产生2 GHz频率,如图3所示。

生成高控制电压,有几种可行方案。其一是使用有源环路滤波器,该滤波器基本是由高速放大器和低通滤波器构成,可以将来自鉴相器(CPOUT)的输出脉冲转化为干净的直流电压。或者,可以使用带集成电荷泵的PLL频率合成器,例如ADI的ADF4150HV,该器件不需要额外的有源环路滤波器。虽然这两种解决方案都需要高压电源,但是使用ADF4150HV可以减少所需的组件数量。也可以避免有源滤波放大器导致的失真和相位噪声。此外,ADF4150HV允许实现小数N或整数N锁相环频率合成器。 终VCO的频率可以进行1、2、4、8或16分频,使得输出频率 可达到31.25 MHz。

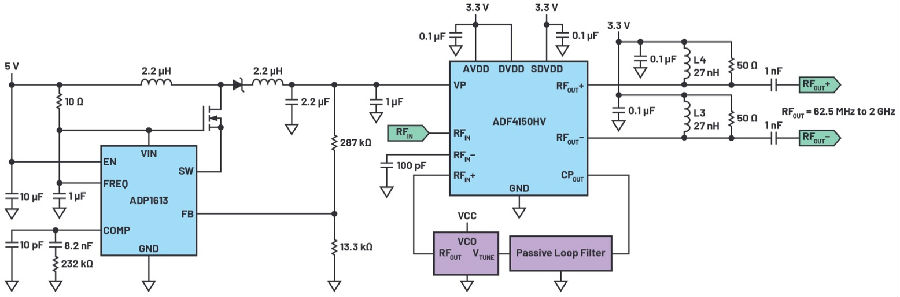

图2.用于ADF4150HV的高压电荷泵电源简化电路

图3.DCYS100200-12的控制电压与频率关系曲线1

ADF4150HV的集成电荷泵所需的高电压可以使用直流-直流升压转换器ADP1613 生成,且不降低PLL性能。 ADP1613是一款集成功率晶体管的高效开关稳压器,可以轻松实现 20 V的输出电压。也可以使用额外的外部组件实现更高的输出电压,尤其是通过外部功率晶体管实现。ADP1613的开关频率可在650 kHz至1.3 MHz范围内调节。这样可以实现更出色的瞬态响应和简单的噪声过滤。一般而言,推荐选择高于1 MHz的开关频率,以便通过PLL环路滤波器降低开关噪声。

采用ADF4150HV的锁相环频率合成器电路通过使用集成的RF分频器,提供超宽带PLL功能。工作频率范围为62.5 MHz至2 Ghz。通过采用相同的PLL硬件设计,可以为系统中的多个不同的硬件平台生成不同的频率。但是,如果要求一项设计适用于不同的VCO类型,则需要在设计中集成相应的环路滤波器。这样才能确保锁相环可靠运行。为了实现相对较宽的输出频率调节范围,以及相关的更高输出功率,ADF4150HV的每个RF输出也需要采用小型滤波器。将27 nH电感和50 Ω电阻并联,可以有效调节高达3 GHz的频率。该电阻提供定义上的输出阻抗。较低的电感将导致频段扩展到较低的范围。

如今,也可提供适用于更大频率范围(即适用于PLL、滤波器和VCO)的一体化集成解决方案,但是,由于不同组件之间的距离过近,可能导致无用耦合。分立式设计和由此实现的物理分隔可以充分降低这种风险。

PLL频率合成器模拟工具ADIsimPLL?也可以为HF功能模块开发和HF信号链器件建模提供有效帮助。通过使用该工具,设计人员更容易模拟所有会影响PLL性能的重要非线性效应;例如,频率合成过程中出现的无用杂散(杂散频率)。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。