交错运行方案已被广泛采用于DC/DC并联电源系统中,不过现有方案多采用集中式控制,通过一个独立的控制模块产生一系列频率相同而相位差为2πPN的触发脉冲来驱动相应的变换器。这种方案优点是控制简单,但其缺点也显而易见,即该方案难以适应模块数目变化的情况。此外集中控制单元的采用也使得系统的可靠性极大地取决于控制单元的可靠性,提高了系统的运行风险。为了解决集中式控制的不足,有文献提出了一种基于交错线的自动交错控制方案,该方案采用分布式控制,能够适应模块数目变化的情况,而且分布式控制的采用也降低了系统由于集中式控制单元而带来的运行风险。较之传统的集中式控制方案而言,这种控制方案的优势是很明显的,但其缺点也很明显,那就是交错线的引入一方面使得系统的模块化无法真正实现,另一方面,交错线极易受到干扰,这使得系统的可靠性受到影响。

为了解决现有交错运行控制方案的缺点,本文研究了一种无交错线自动交错控制方案,这种方案采用分布式控制,而且不需要交错线,能够提高系统运行的可靠性,并且实现真正的模块化。

无交错线自动交错原理

基于无交错线自动交错控制方案的三模块并联系统的电路结构图如图1所示,其中主电路采用普通BUCK变换器。由于模块2、3的结构与模块1完全一样,故而简化之。

图1 三模块并联系统结构图

从图1可以看出,三个参与并联的模块只有输出端通过负载相互连接,此外模块之间再无其他连接线。在每个模块中,主电路向控制电路反馈输出电压、本模块输出电流以及本模块主电路主开关管的开关信号,而控制电路向主电路提供PWM控制信号来控制主电路主开关管的导通与关断。

该方案原理如图2所示,主要由脉冲整形单元、异地时钟获取环节、锁相环电路以及PWM控制信号发生电路构成。

图2 控制电路原理框图

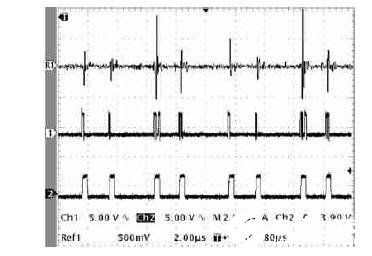

由图可知,系统时钟是通过提取输出电压中的尖峰脉冲成分并对其进行处理而得到的。由于不同模块通过的传输路径的差别,因此提取到的尖峰脉冲幅值不一,必须首先进行“整形”,这可以通过高速比较器来实现。经过高速比较器后得到的系统开关信号中,对应于每次开关时刻可能有多个窄方波。为了确保对应于每个开关时刻只有一个开关信号,还需要用单稳态触发器对高速比较器输出信号进行处理。此后,得到的一系列脉宽相等幅值相同的窄方波便为与系统每个开关动作对应的系统时钟,如图3所示。其中,波形R1是经过高通滤波后的电压尖峰脉冲,波形1是经过高速比较器“整形”后得到的一系列窄脉冲,而波形2则是单稳态触发器输出的对应于系统各次开关动作的系统时钟的。

得到系统时钟后,便可以通过系统时钟与本地时钟之间的逻辑运算来获得异地时钟。为了实现系统中各模块的交错运行,则必须实现各模块对应时钟的交错运行,在本方案中,这通过各模块控制电路中的锁相环电路来实现。

图3 系统时钟信号的提取

以两模块并联的情况为例,图4所示波形2为本地模块时钟,波形1为异地模块时钟,由图可知,此时,本地模块时钟频率小于异地模块,鉴相器检测模块时钟的上升沿得到3所示波形,低通滤波后得到本地VCO输入,是一个渐升的直流电压,从而使得本地VCO输出频率提高,将此VCO的输出脉冲作为本地模块的 SYNC同步,则可以使本地时钟频率上升。而对异地模块而言,其VCO输入是一个渐降的直流电压,则可以使其时钟频率下降。这样通过本地模块和异地模块时钟频率的反方向调整,终即可实现频率同步。

图4 两模块并联系统频率同步的实现

如果两个模块的VCO压频特性一致(这可以通过调节锁相环的外部电路参数实现),且我们事先设定他们的初始振荡频率(offset frequency)也就是VCOin=0V时的振荡频率相同,那么,终实现频率同步时,两模块的VCOin也一定相等,则两模块的相位必然交错180 度。

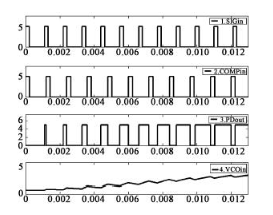

图5为三模块交错结果示意图,其中波形1为本地模块检测到的系统时钟,为一系列等宽的窄方波脉冲,每个窄方波对应系统中某个模块的开关动作(开通或者关断);波形2为从系统时钟里除去本地时钟后剩下的部分,即异地时钟,反映了系统中本地模块之外的其他模块的开关时钟信息。在本地模块控制电路中,锁相环电路根据所检测的异地模块开关时钟信息(波形2)与本地开关脉冲(波形3)进行鉴相,鉴相器输出结果为一周期变化的矩形方波,如波形4所示。在一个周期内,该方波上升沿对应本周期内异地时钟信号的个上升沿,下降沿对应本地开关信号的上升沿。除了本周期的个上升沿之外的其他异地时钟信号的所有边沿均为无效信号,在系统中不起作用。对于系统中其他两个模块,也是如此,对应的鉴相器输出结果分别如波形5、6所示。

图5 三模块并联系统交错示意图

本文所提的方案能够实现系统的自动交错运行,具体过程如图6所示。系统本来有三个模块并联运行,每个模块交错120度,分别记作模块1、模块2、模块3。其中模块1和模块2的开关脉冲如图中波形1、2中实线波形所示。

图6 自动交错的实现

在某个时刻,模块3退出运行,系统变成两模块并联运行。在变化瞬间,对模块2而言,其控制电路中鉴相器的输出发生突变,输出矩形方波占空比降低,如图中波形3中实线波形所示,这导致模块2的开关频率降低,在图中表现为它的开关脉冲“右移”。

对于模块1而言,在系统发生变化的瞬间,其鉴相器的输出不会发生突变,而随着模块2的开关频率降低,则模块1控制电路中鉴相器的输出矩形方波占空比也将逐渐降低,而这也将导致模块1的开关频率逐渐降低,在图中也表现为它的开关脉冲“右移”。

经过一段时间的调整后,模块1和模块2将达到一个新的稳定状态,两者的开关频率将再次相同,此时,两个模块必然互相交错180度。系统达到新的交错状态,如图6中的虚线波形所示。

在本方案中,PWM信号是通过SG3525芯片产生的。锁相环输出信号用作PWM信号发生电路的同步端,而所产生的PWM脉冲占空比则由电流设定与电流反馈的误差进行调节。

实验结果

为了验证本文所提无交错线自动交错控制方案是否可行,我们设计了一台基于该控制方案的实验样机。样机由三个相同的小功率BUCK电路并联而成,输入电压30~50V,开关频率95~105KHz,负载为纯电阻,8~15Ω。

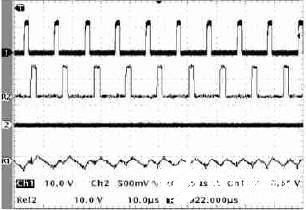

图7为三模块并联的BUCK变换器系统波形,其中信号R1、R2和R3为三个模块的PWM开关信号,由图可见,此三个信号彼此交错120度,表明系统工作在交错运行状态。

图7 三模块并联交错运行波形图

信号1为系统输出电压的交流成分,包括纹波和电压尖峰脉冲,对应的刻度为50mV/p。此时的电压纹波峰2峰值为24.7mV,是比较低的,而纹波频率则为系统开关频率的三倍,符合前文对交错运行效果的分析。

信号R4为此时的输出电压波形,刻度为5V/diV,此时输出电压为9.6V,电压平直程度较好,无明显纹波成分。

图8显示了该系统自动交错运行功能的实现。初始系统有三个模块并联并且运行在交错状态,其中信号1、2和信号R2为初始参与并联运行的三个模块的PWM主开关信号,彼此交错120度。在某个时刻,其中的一个模块(对应PWM主开关信号2)因成了一条直线。此时,系统的自动交错功能开始起作用。由图8可见剩余两模块(对应PWM主开关信号1和R2)由彼此交错120度逐渐向彼此交错180度过渡,在经过若干周期后实现彼此交错180度运行,即达成了两模块并联时的交错运行状态。信号R1显示的是这个过程中系统输出电压纹波变化情况。

自动交错实现过程

图8 自动交错实现过程

为了验证交错运行的实际效果,我们还设计了一组对照实验,通过使两模块并联系统分别运行在并联同步、并联不控以及并联交错运行状态,比较各自输出电压纹波之间的差别来验证交错运行确实能够降低输出电压的纹波幅值,并且提高输出电压的纹波频率。

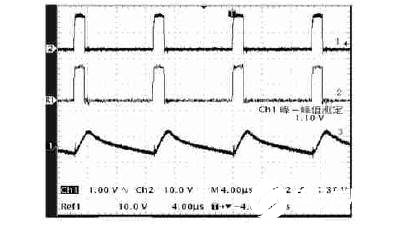

在图9中,两个模块的PWM主开关信号频率相同且彼此同相,因此处于同步运行状态,此时,两模块出电压纹波的波峰无相差,二者彼此重叠,因此,输出电压的纹波比较明显,幅值比较高,峰2峰值为1.1V,纹波的频率与系统开关频率一致。

在图10中,两个模块的PWM主开关信号相互独立,二者的频率有差别,体现为两个信号的相位差呈现周期性变化,而表现在输出电压上则是输出电压的纹波幅值时大时小,在0.5V至1.0V间呈现周期性变化,变化的周期跟两个PWM主开关信号的频率差有关。两模块并联系统同步运行

图9 两模块并联系统同步运行

两模块并联系统独立运行

图10 两模块并联系统独立运行

在图11中,两模块的PWM主开关信号频率相同,相位互相交错180度,因此处在交错运行状态,此时两模块输出电压的纹波波峰彼此错开,表现为输出电压纹波幅值较低,峰2峰值为0.56V,而纹波频率则提升为系统开关频率的两倍。

两模块并联系统交错运行

图11 两模块并联系统交错运行

通过这组对照实验可以看出,并联系统的交错运行确实能够降低系统输出电压的纹波幅值,并且提高纹波频率。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。