近些年,随之模拟信号技术性的发展趋势,必须解决的信息量愈来愈大,解决的速率也变快,因而具备髙速特性DSP 集成ic的运用获得了普遍高度重视。而根据DSP 解决的统计数据通常要传送给PC 机开展储存和再解决,那麼就务必处理DSP 与 PC 机中间的高速通信难题。本方案设计以德州仪器(TI)的C5000 系列产品DSP 集成icTMS320VC5416为微控制器,运用Cypress企业出示的USB2.0插口集成icCY7C68001 保持了USB2.0 从机接口设计,进而使PC机与DSP 根据USB2.0 插口保持髙速双重地传送数据。

2 TMS320VC5416 与CY7C68001 EZUSBSX2硬件配置接口设计

系统软件计划方案选用PC机做为上位机,承担USB系统总线上检验到机器设备连接并开展枚举、鉴别的全过程,而且能够根据在PC机上运作手机应用程序来控制参数的传送。USB集成ic做为USB机器设备端,联接DSP与上位机的数据传输。DSP用以保持USB协议书,根据DSP程序编写保持DSP统计数据根据USB插口与PC机通讯,且USB集成ic的描述符载入及各种各样指令情况的解决均根据DSP程序编写保持。

TMS320VC5416 是TI 的这款16bit 指定性能DSP,因为VC5416的功率低、特性高,其分离的指令和数据室内空间使该集成ic具备高宽比的并行操作工作能力,在单周期时间内容许指令和数据一起存储,加上高宽比提升的指令集,促使该集成ic具备很高的与运算速率,一起该集成ic自身 具备丰富多彩的片内

存储器資源及其多种多样上面外接设备,因而在建筑界获得了普遍的运用。

Cypress 企业的CY7C68001 EZ-USB SX2 是这款性能、方便使用的USB2.0 插口集成ic,考虑USB2.0 协议书,可工作中在髙速(480Mbps)或飞速(12Mbps)方式下,出示1个操纵端点用以解决USB机器设备的恳求及其4个可配备端点用以传送操纵和网络信号,这4个端点共享资源1个4KB的FIFO室内空间,具有规范的8位或16位外界服务器插口,可无缝拼接联接多种多样规范微控制器,比如说DSP、ASIC和FPGA等,并可依据要求设定为同歩或异步插口,片内集成化锁相环(PLL),该集成ic运用于DSL调制调解器、MP3、SD读卡器、数码科技照机、扫描机、复印机等机器设备。

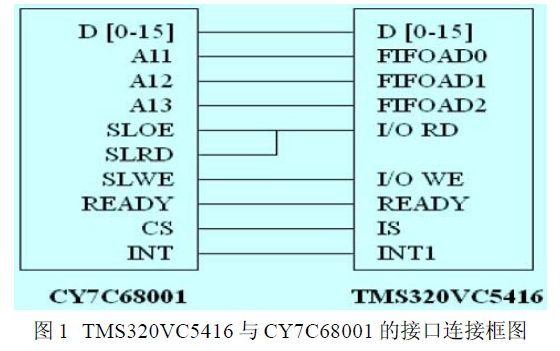

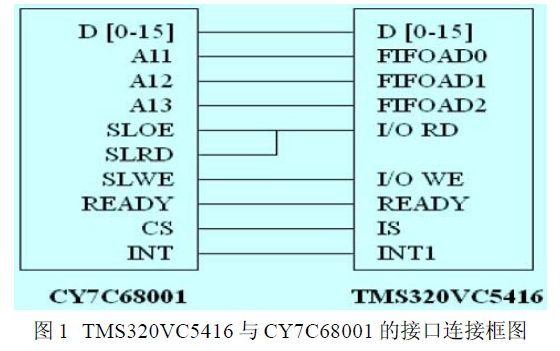

系统软件的硬件配置接口设计如图所示1、图2图示,二者根据统计数据、地址总线及其读、写

电源线等开展通讯,CY7C68001的片选数据信号联接至TMS320VC5416 的I/O室内空间片选数据信号上,CY7C68001 的FIFO拓展在VC5416 的I/O 室内空间上。

根据DSP与PC机中间的高速通信设计方案

开关电源一部分选用一整片1117 将5V 变为3.3V供求平衡CY7C68001EZ-USB SX2,仿真模拟地与大数字地中间选用

磁珠联接,校准一部分选用RC电路原理,且集成ic材料上详细介绍有典型值100KΩ和0.1μF。

3 插口实际操作基本原理

CY7C68001 有2个外界插口:

(1) 指令插口:用于浏览CY7C68001 寄存器、Endpoint 0缓冲器,及其叙述表。

(2) FIFOapi接口:用于浏览4个1K字节数的FIFO中的统计数据。

这2个外界插口均能够根据同歩或异步的方法开展浏览。

本设计方案选用异步的方法开展浏览。依据图3 的详细地址分派,运用TMS320VC5416 的四根上位详细地址线(A11、A12、A13)联接CY7C68001 的FIFOAD0/1/2,用于挑选FIFO2、FIFO4、FIFO6、FIFO8及其指令插口,其详细地址表如图所示3图示。CY7C68001的详细地址线FIFOADR[2:0]为100B 时,选定CY7C68001 的指令口(Command)。根据CY7C68001的指令口,能够浏览37个寄存器、Endpoint 0缓冲器(64个字节数FIFO)和叙述表(500个字节数FIFO)等,对这种寄存器开展读写能力方法选用再次寻址方式,即根据指令口即将寻址方式的寄存器的子详细地址和实际操作种类(读或写)载入,随后再根据指令口将统计数据读取或载入相对的寄存器。

载入指令口的內容称之为命令字,命令字包括要寻址方式的寄存器的子详细地址,或要载入寄存器的统计数据的高4位或低4位。读指令口务必要跟在给指令口写读命令字以后,读取的为相对寄存器的8位统计数据。因此,寄存器的写实际操作由3 个流程构成:

4 USB 插口的软件开发

USB插口的软件开发由两一部分构成:一要在PC机Windows中运作USB 2.0 UTIlity 专用工具,是1个Windows 图形用户界面手机软件,出示CY7C68001 与Windows 电脑操作系统的插口程序流程,促使CY7C68001的开发设计越来越简易。二要在在DSP中运作嵌入式应用编程代码,出示硬件配置的驱动器,用于管理方法CY7C68001开展不一样方法的数据处理方法,从而实现USB2.0 传送协议书。

4.1 USB 插口的软件开发步骤

USB插口的软件开发,DSP端编码大概包含DSP集成ic复位(vc5416_init 涵数)、USB集成ic复位(sx2_init 涵数)、USB集成ic配备程序流程( s x 2 _ s e t u p 涵数) 及其USB 集成ic统计数据读写能力程序流程(sx2_processdata 涵数),操作流程如图所示4 图示。

DSP集成ic复位(vc5416_init涵数)关键承担设定VC5416的输出功率,配备SWCR及其SWWSR寄存器,另一个本软件系统选用1个GPIO脚位做为68001的校准数据信号,因此还必须进行有关设定。

USB集成ic复位(sx2_init涵数)关键承担消除Buffer堆栈及其使能VC5416 的外界终断INT1,待复位完毕后传出READY终断,这时DSP将描述符载入68001,开展枚举全过程,待枚举根据后传出ENUMOK终断,枚举方法能够选用外界EEPROM根据I2C系统总线通电后从外界导进描述符,也可选用根据运作DSP程序流程从DSP导到68001,本软件系统选用第二类枚举方法。

USB集成ic配备程序流程(sx2_setup涵数)是在指令安全通道(0连接点)接到没法全自动解决的上位机恳求,68001向VC5416传出SETUP终断后实行的程序流程,这时VC5416 根据对SETUP寄存器持续实行八次读操作步骤就能获得8字节数恳求,系统软件能够响应当恳求或STALL该恳求。

USB 集成ic统计数据读写能力程序流程(sx2_processdata 涵数)即PC 机与USB从机器设备端遵循USB传送协议书开展数据通讯。

CY7C68001的详细地址FIFOAD[2:0]为100时,选定CY7C68001的指令插口。针对指令插口的读写能力要分二步开展,即在READY合理时,先根据指令插口载入要寻址方式寄存器的子详细地址和实际操作种类(读或写),以后,在READY再度合理时段2次读写能力指令插口,就能读写能力一个字节的统计数据。

4.2 终断服务项目编程设计关键点

DSP应用1个外界终断脚位(INT1)与CY7C68001的INT脚相接,USB系统总线上造成一连串的主题活动,均会开启相对的终断,如果终断造成,DSP 是从CY7C68001 的Command 嘴中载入相对的值,来分辨造成的是哪种终断。