现实世界的本质就是模拟。我们需要从周围世界采集的任何信息始终是一个模拟值。但要在微处理器内处理模拟数据需要先将这些数据转换为数字形式。因此,SoC中使用多种不同的ADC(模数转换器)。根据几个参数(即吞吐量、噪声抗扰度及设计复杂性)选择相应类型的ADC。

SoC设计人员不需要了解集成到SoC中的任何IP的复杂深层设计。因此,如果将ADC视为一个黑盒,即使从SoC设计人员的角度来看,在SoC层面仍有许多因素会决定ADC的性能质量。我们必须格外注意这些因素。

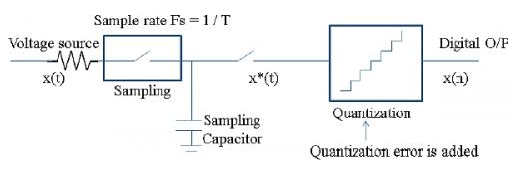

将模拟信号转换成数字数据需要在时间以及幅度上进行离散化。时间离散在采样相位上进行,而幅度离散在量化相位进行。采样通过采样保持电路完成。采样保持电路有一个开关、一个阻抗路径以及一个电容,当开关关闭时在该电容上对电压进行采样。量化简言之是指在一定范围内(由ADC的参考电压控制)将采样值缩放为数字值。采样和量化相位如图1所示。

如何将ADC模数转换器集成到SoC中去

图1:通用模数转换流程

即使在简单的ADC黑盒示意图中,我们也需要了解其在SoC中的集成知识:

● ADC有多个输入信道,只有一个数字输出。

● 信道之间存在复用,这样,在任何时候ADC都能转换来自于一个信道的数据。

● 采样通过一个时钟进行。

● 任何ADC在其量化相位都使用一个基准。

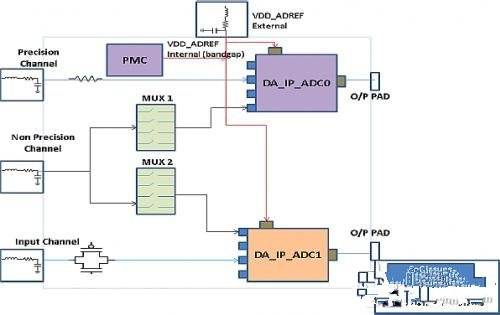

鉴于以上因素,我们便会明白,即使在同一个、甚至非常简单的ADC外部视图中也会有许多设计难点,同时还有许多常见问题。我们将在以下章节中逐一讨论。图2展示了将ADC集成到SoC的一般情况。

如何将ADC模数转换器集成到SoC中去

图2:ADC到SoC的一般集成

模拟输入信道

在转换的个相位,也就是采样相位,输入信道的模拟输入是重要的。采样电容是ADC设计的组成部分,但是采样遇到的电阻与SoC集成有较大的关联。需要核实一些常见的整合细节。

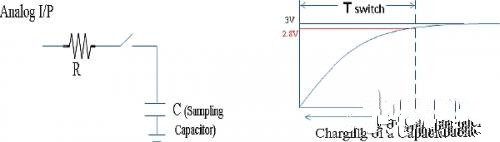

模拟输入路径的电阻决定采样所需的时间(如果C相同,采样时间将随着R的增加而增加,采样时间等于电容器的充电时间)。采样相位通过一个开关控制。在ADC IP设计的一个可编程寄存器指定的时段内,该开关保持关闭。

也就是说,任何模拟值存储到采样电容器的时间由使用可编程寄存器的ADC设计决定。我们称该时间为Tswitch。同时,模拟输入需要一定的时间给采样电容器充电,这等于电容器通过阻抗路径的采样时间(RC)。我们将这段时间称为Tsampling。对于被采样的模拟值:

Tsampling<Tswitch (等式1)

Tswitch在ADC IP内编程,而Tsampling只由集成决定。因此,作为SoC设计人员,我们需要确保实现Tsampling化。一种方法是使该路径的电阻保持。这种情况请参见图3。

图3:为采样电容器提供的充电时间不足的后果

图字:模拟I/P;C(采样电容器);电容器充电

我们在ADC转换过程中经常讨论SNR劣化。对于ADC来说可以轻松避免的噪声源是由于开关关闭时间不足而引入的误差,或由于ADC阻抗路径的采样时间过高而引入的误差。基本情况下,Tsampling或Tswitch不符合上述标准。

信道分类

信道可以两种方式进行分类:种方法是根据信道的ENOB(有效位数)规格进行分类,即精密和非精密信道,第二种方法是根据模拟输入的来源划分,是来自于SoC外部还是内部,即外部信道和内部信道。

根据ENOB规格

精密信道是指ENOB(以及SNR)较高的信道。需要确保满足等式1才能符合较高的SNR规格。大多数SoC的设计都通过使精密信道的MUXing深度保持较低水平来实现,因为路径中的每个MUX都会引入一些R以及一些C。此外,SoC中精密信道数也有限,因为信道路径中的MUX的阶决定对模拟输入可见的有效电容(由于电荷共享,其信道的电容器的充电时间会非常高)。

因此MUX的阶必须非常小,这意味着SoC中精密信道的数量也非常少。非精密信道是指SNR规格不严格的信道。精密信道和非精密信道如图2所示。因此,SoC中的非精密信道通常较多,而ADC精密信道的数量有限。

信道可以是内部或外部信道

ADC的信道可以是外部信道(来自于padring)也可以是内部信道(SoC内其它IP的输出)。

内部信道

需要知道一个IP输出到ADC输入的路径电阻的估算值,才能了解ADC能够提供的采样时间。如果采样时间低于该值,那么采样电容器充电会不足,采样值也不正确。然后,这个不正确的值将被量化,从而导致SNR劣化。

外部信道

对于外部信道来说常见的问题是,在两个不同的ADC中同时转换来自于一个焊盘的相同的模拟数据。造成这种情况的原因是,这两个ADC的采样电容器之间存在电荷共享。发生同时采样时,一个ADC的采样电容器上的保持采样电压会受到另一个ADC采样相位的干扰。这是因为应该为一个电容器充电的模拟电压遇到两个需要充电的电容器。由于电荷共享导致采样电容器采样的数值小于输入,从而导致ADC转换了错误的值。

可以保持软件限制以确保不会同时对共享的信道进行采样,从而解决这个问题。另一种解决方案是,如果发生了同时采样,则为个ADC提供较大的采样时间。这将允许个ADC重新设置它需要转换的电压,从而减少转换错误值的机会。

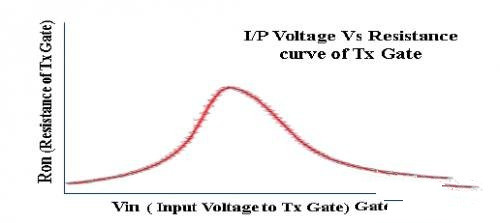

当这些内部/外部信道的路径中存在传输门时,会出现一个常见问题。传输门的电阻取决于输入电压,因此,如果一个动态信号(该信号的值随着时间不断变化)通过该路径到达ADC进行转换,则会出现SNR劣化。这是因为,随着传输门上模拟输入的值不断变化,其电阻也发生变化,导致采样时间也发生了改变。这样,采样数据不准确的几率就更大。解决这个问题的方法是,采用一个改良后的传输(Tx)门,它在整个输入范围内均可保持相当恒定的导通电阻。传输门的导通电阻与采样电容C间应有一个至少为10,000的因子,才能使THD小于80db

图4:传输门的RON与输入电压变化

图字:Ron(传输门电阻);I/P电压对传输门的电阻曲线;Vin(传输门的输入电压)

不同SoC操作模式下的ADC的时钟源

SoC以不同的模式工作。这些模式以芯片的不同活跃等级(电流消耗)区分。SoC可能拥有低功耗模式(部分活动模式)以及主运行模式(完全活动模式)。低活动或部分活动模式是指设备为了降低功耗以较低频率运行,时钟源通常是内部RC振荡器。在这些低功耗模式下,PLL通常被禁用。PLL是抖动非常低的时钟源,而RC振荡器则是抖动的时钟源。

让我们了解一下时钟源的抖动对SNR值的影响。采样周期和采样开始与结束时间以及转换与ADC工作的时钟源保持同步。为了让采样以相同的时间间隔进行,该时钟的沿本身应一致统一。任何有抖动的时钟都会产生不均匀的时钟沿,导致采样不一致。对于某些设计类型的ADC (SAR)来说,输入数据采样可能只在采样周期内在一个时钟沿进行,而对于其它类型(如Σ-Δ[SD] ADC)来说,采样可能在采样周期内在每个沿进行。因此,由于时钟抖动,SD ADC更容易出现SNR劣化。

如果时钟源有抖动,SD ADC可能会产生10-12dB的SNR劣化。但无论什么类型的ADC,时钟抖动在一定程度上都可能会影响采样。ADC工作的时钟源与系统时钟源一样,取决于SoC的工作模式。对于RC振荡器,时钟的抖动较大,因此SNR劣化较高,而对于PLL,抖动较小,因此SNR劣化也较低。因此,需要平衡时钟源导致的SoC电流消耗和ADC的转换质量。

ADC的工作参考电压

SoC中的ADC设计需要既能够在外部电源的参考电压下工作,也能够在内部参考电压下工作。ADC使用的各种参考电压都有其特定的问题。让我们逐一讨论。

外部参考电压

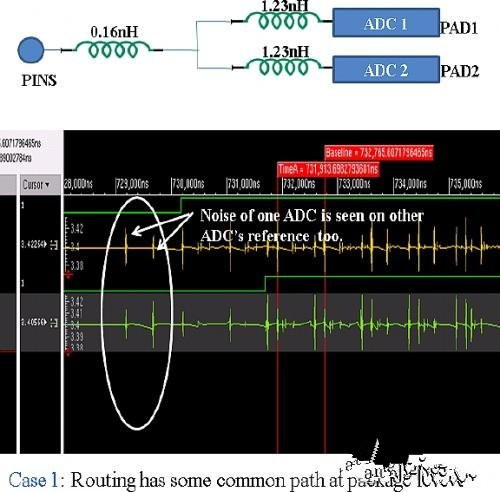

如果ADC使用的参考电压是外部电压,通常会产生与参考共享有关的问题。这是SoC的一个久而未解的问题,原因是一个非常简单的限制,那就是SoC能够拥有的粘合引脚数有限。SoC提供的外部引脚和焊盘数量有限(目的是降低成本),因此通常的做法是使SoC中的不同ADC共享参考电压。这就是由于一个ADC进行转换而导致到达另一个ADC的参考电压不稳定的原因(两个ADC之间的串扰)。这些串扰问题没有在IP层模拟中解决,导致SoC级SNR性能不佳。

避免出现这种问题的一种方法是在设计时将去耦合电容器放在IP的参考焊盘附近,这会减少参考电压的不稳定性。但这会增加芯片的尺寸,进而增加芯片的成本。因此,设计人员想出了了一个替代方案,那就是在封装上减少两个焊盘之间的公共结合线路径,并将引脚电容器放在电路板上。通常,SoC中应避免ADC参考焊盘共享。

如何将ADC模数转换器集成到SoC中去

外部参考

通常来说,内部参考电压是一个带隙参考电压,它是SoC内产生的参考电压。应确保在ADC开始转换之前,该电压值已经稳定下来。如果情况并非如此,那么转换量化相位将出现错误。通常对该问题的推荐变通方案是,SoC中的电源管理单元应向ADC发送指示,告知带隙参考电压已获得了稳定值,ADC可以开始转换流程。

本文小结

SNR劣化现已成为ADC设计人员的术语。SoC本身存在许多集成问题,导致SNR劣化。本文重点介绍了一些常见问题以及可行的解决方案。设计人员需要确保集成正确无误。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。