摘要:为了有效解决金属一氧化物半导体场效应晶体管(MOSFET)在通信设备直流-48 V缓启动应用电路中出现的开关损耗失效问题,通过对MOSFET栅极电荷、极间电容的阐述和导通过程的解剖,定位了MOSFET开关损耗的来源,进而为缓启动电路设计优化,减少MOSFET的开关损耗提供了技术依据。

在采用集中供电的二次电源系统中,板卡插入主机时,主机已经处于稳定的工作状态,所有容性负载均已充电。待插的板卡是不带电的,板卡上的容性负载没有充电,在热插入过程中,待插板卡上的电容瞬间充电。充电过程将在插入的瞬间从系统电源吸纳大量的电流,导致系统电压瞬间跌落,影响其他板卡的正常运行。另外,在电源线接触的瞬间,系统电源的输出电阻和待插板卡的电容组成RC充电通道,由于电源的输出电阻很小,浪涌电流非常大。在拔出板卡的过程中,板卡上的旁路电容放电,和背板之间形成一个低阻通道,也会产生瞬间大电流。浪涌电流携带大量的能量,会毁坏接口器件、连接器和金属连线。为了防止上述情况发生,需要对电源系统进行必要的保护性设计。

解决带电插拔不利影响的根本措施是减少浪涌电流,浪涌电流是由于待插板卡的容性负载在上电瞬间充电引起的。由公式I=Cdv/dt可知,上电时间直接决定了浪涌电流的大小。在一般的带电插拔过程中,充电电压相当于一个阶跃激励,dv/dt极大。我们知道在采用RC充电回路中,电容的充电时间可以简单地通过改变R和C值来设定,如果利用这个渐变的电压控制一个在一定电压下导通的开关MOSFET,就可以缓慢导通二次电源,非常有效地减少浪涌电流的值,从而地减少带电插拔带来的负面影响。

公司网络、数据及无线基站产品各单板基本都应用了由N沟道MOSFET加分立元件组成的缓启动电路来减少直流-48 V上电的浪涌电流。由于该MOSFET在单板上不仅用来实现-48 V缓启动功能,在某些单板也是远程控制上下电的关键器件。一旦MOSFET失效,单板-48 V电源输出就出现故障,更无法实现缓启动功能和远程控制功能,将严重影响产品单板的正常运行。可见,MOSFET在单板缓启动电路中起到了举足轻重的作用,科学分析MOSFET特性,深入了解其导通特性,减少MOSFET的损坏就是整个热插拔缓启动电路的关键。

1 MOSFET在开关应用过程中的问题

公司网络、数据及无线基站产品各单板都采用通过简单的改变RC充电回路中R和C值,产生一个渐变的电压控制一个在一定电压下导通的开关MOSFET,来导通输入直流-48V电压进而减少热插拔过程的浪涌电流。但是因为对于MOSFET本身内部结构、开关过程和损耗了解不全面,造成了大批MOSFET失效的。笔者通过对公司各产品直流-48V缓启动电路MOSFET失效情况分析和统计发现,MOSFET的失效在公司各产品事业部都有发生,失效问题数量比较多,但失效原因却比较单一,都是由于短时过功率烧毁。失效中同时也提出了改善对策,需要我们改进目前-48 V DC缓启动电路的驱动设计减少MOSFET开关过程的损耗,避免MOSFET失效问题的再次发生。

2 MOSFET的开关损耗

由于造成MOSFET失效的原因大多都是由于开关过程损耗过大导致的过功率烧毁。究竟MOSFET的开关损耗是如何产生的,在 MOSFET导通的哪一阶段产生,跟什么因素有关?这个必须从MOSFET本身的寄生栅极电荷、极间电容入手,通过对MOSFET寄生电荷和MOSFET 的开关过程来分析开关损耗产生的因素及其原因。

2.1 栅极电荷QG

在MOSFET中,栅极电荷决定于栅极氧化层的厚度及其它与裸片布线有关的物理参数,它可以表示为驱动电流值与开通时间之积或栅极电容值与栅极电压之积。现在大部分MOS管的栅极电荷QG值从几十纳库仑到一、两百纳库仑。

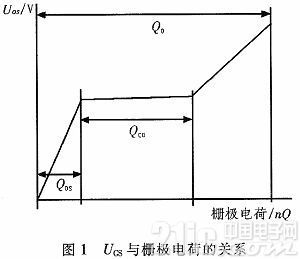

如图1是栅极电压和栅极电荷之间的关系,从中可以看到栅极电荷的非线性特性。这条曲线的斜率可用来估计栅极电容Cgs的数值。曲线的段是线性的,QGS是使栅极电压从0升到门限值所需电荷,此时漏极电流出现,漏极电压开始下降;此段栅极电容Cgs就是Cgs。曲线的第二段是水平的,栅极到漏极电荷QGD是漏极电压下降时克服“Miller”效应所需电荷,所以栅极到漏极电荷QGD也称为“Miller”电荷。此时栅极电压不变、栅极电荷积聚而漏极电压急聚下降。这一段的栅极电容是Cgs加上Cgd的影响(通常称为Miller效应)。

通过观察栅极电压UGS和栅极电荷QG之间的关系可以看出,寄生的栅极电荷QG值虽然很小,但是在MOSFET管导通过程中可分为明显的3个阶段;同时,由于受栅极到漏极电荷QGD即“Miller”电荷的影响使栅极电荷产生了非线性特性,也影响了栅极电压UGS的线性升高。

2.2 MOSFET的极间电容

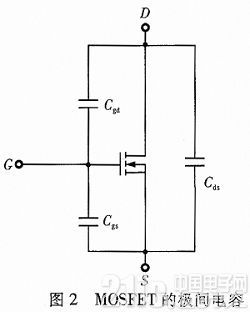

MOSFET其内部极间电容主要有Cgs、Cgd和Cds。并且Cgs>>Cds>>Cgd。其中Cgs为栅源电容、Cgd为栅漏电容,它们是由Mos结构的绝缘层形成的;Cds为漏源电容,由PN结构成。MOSFET极间电容等效电路如图2所示。

MOSFET管的极间电容栅漏电容Cgd、栅源电容Cgs、漏源电容Cds可以由以下公式确定:

Cgd=Crss

Cgs=Ciss-Crss

Cds=Coss-Crss

公式中Ciss、Coss、和Crss分别是MOSFET管的输入电容、输出电容和反馈电容。它们的数值可以在MOS管的手册上查到。

通过观察MOSFET极间电容和寄生栅极电荷QG,可以看到,MOSFET极间电容是由其导电沟道结构及工艺决定,固有的。由于存在反馈电容及栅极到漏极电荷QGD,QGD的大部分用来减小UDS从关断电压到UGS(th)产生的“Miller”效应,此时Vds尚未达到Vsat。对曲线水平段所对应的电容Cgs充电所花费的时间越长,Vgs维持在一个恒定电压上的时间也就越长,MOSFET达到饱和状态所需的时间也就越长。这种情况相应的MOSFET的能量损耗也越大,产生的热量越多、效率越低。

2.3 MOSFET的导通过程

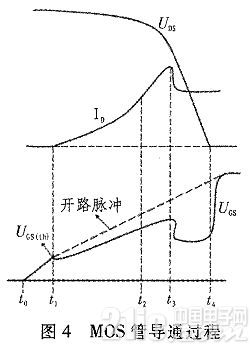

MOSFET极间电容是影响开关时间的主要因素。由于受极问电容的影响,MOSFET的导通过程可分为如下几个阶段(如图4所示)。

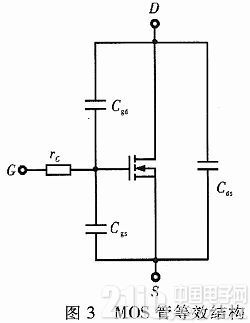

1)t0~t1期间:驱动电压从零上升,经rG对图3 MOSFET等效结构中G端输入电容Ciss充电,电压按虚线上升(开路脉冲),Ciss越小,则电压上升的越快;

2)t1~t2期间:t1瞬时,MOS管的栅源电压达到开启电压UGS(th),漏极电流开始上升;由于漏源等效的输出电容Coss会对MOSFET容性放电,漏极电流ID上升,漏源电压下降;同时受反馈电容Crss的影响G驱动电压Vgs的上升速率特别平缓,(低于开路脉冲);

3)t2~t3期间:t2瞬间,漏极电流ID已经达到稳态幅值,但Coss的电压尚大,电流还会上冲;

4)t3~t4期间:t3瞬时,Coss在漏极峰值电流放电下,漏极电压迅速下降,受反馈电容Crss的影响G驱动电压略有回落,维持漏极电流所需的驱动电压值,保持平衡;

5)t4之后:t4瞬时,Coss的电荷放完,漏源电压近似为零,并保持不变;反馈消失。Vgs升高到开路脉冲,进入稳态导通期。

由此MOSFET开通过程可看,漏极电流在QG波形的QGD阶段出现,由于受极间电容的影响,VDS电压失去了线性的过程,所以一方面在漏极电流出现的过程,该段漏极电压依然很高,漏极电流上升的速度是漏极电压下降速度的几倍,这就造成了MOSFET管功率损耗的增加。另一方面开关导通时,由于受受 “Miller”电荷的影响,电容Cgs充电需花费较长时间,Vgs长时间上升速率特别平缓,(低于开路脉冲),这种情况造成MOSFET的损耗很大并产生大量热量、降低了开关效率;

3 损耗来源

通过对MOSFET特性的分析可以看出,MOSFET并不是单纯的电压控制器件。它的开启和开关速度与电流有关,它取决于驱动电路是否能够在它需要时提供足够的电流,使电容Cgs快速充电。由于在第二段时,受“Miller”电荷及极间电容的影响,电容充电需要较长时间,造成MOSFET 管开关损耗增加,产生大量的热量。同时由于VDS电压失去了线性的过程,开关导通时漏极电流上升的速度是漏极电压下降速度的几倍,这将造成功率损耗增加。在这整个过程中,MOSFET的开关损耗和功率损耗都增加,这就很容易造成MOSFET的烧毁。

所以在第二段迫切要求栅极驱动能够提供足够的电流,在短时间内为第二段曲线对应的栅极电容Cgs充电,使MOSFET迅速地开启。同时,要提供一个合理的 Vgs平台电压(也就是总的QG),在此过程控制VDS电压的线性度,使电流的变化和漏极电压变化率相等,减少功率损耗。

利用MOSFET管及分立器件实现-48 V电源缓启动需要优化电路设计,既要提供栅极电流,又要控制好漏源电压的线性度,从而控制漏极冲击电流,以减少MOSFET的损耗。

4 结论

文章阐述了MOSFET本身的寄生栅极电荷和极间电容,深入分解了MOSFET导通的5个阶段,通过对MOSFET开关特性的分析指出了MOSFET导通过程开关损耗的来源,为直流-48 V电源缓启动电路设计的优化提供了技术依据。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。