本文的主旨是启发读者去考虑电子芯片集成度提高对终测或生产测试的影响。特别的,射频(RF)芯片测试方法的主要转移变得越来越可行。一些关于生产测试的关键项目将在这里进行讨论。它们是:系统级测试:RF晶园探针测试;SIP相对SOC的架构;设计人员的新的责任:RF内置自检(BIST);对于测试系统构架的影响。

系统级测试

现代高集成度的芯片有着“射频到比特流”(“RF-to-bits”)或“射频到模拟基带”的构架。射频部分集成度提高带来的冲击之一是测试模式的转移,即使得系统级的测试成为可能。系统级测试有优点也有缺点,的优点是可以减少测试时间,的缺点是它目前并没有被业界广泛接受。而且,这是一个非常有争议的题目。系统级测试基本上是根据被测件(DUT)将要使用的功能进行测试。它非常类似在数字调制中的通过/不一通过(go/no-go)测试,如比特误码率(BER)和矢量误差幅度(EVM)测试。这种测试通过使用带有数字调制信息的信号来模拟无线芯片在天线端接收的信号或有线RF芯片的输入信号宋达到测试目的。

传统上,连续波(CW),单音或双音(Two tone)信号被广泛用来进行RF测试。这些测试方法被使用是因为简单独立的RF芯片结构(如RF输入和RF输出)。由于这些独立的结构被整合,那么终的芯片结构将变得拥挤和复杂。一些反对系统级测试者认为人们在R&D阶段无法花费足够的时间去考虑是否所有的测试能够保证抓出芯片中所有出问题的部分。为了解决这个问题,同时保证尽量少的测试时间,目前所有的这些系统级测试把传统的功能测试(FuncTIonal TesTIng)加入进来作为补充。当产品成熟或设计和制造者的信心增加时,这些功能测试的数量可以逐渐减少。

另外一个针对生产测试的方法是在全面测试系统级芯片中做一些折衷[1]。那就是,把系统级测试(如BER和EVM)测试作为正常的生产测试计划,但是同时周期性的加入特性测试(CharacterizaTIon Test)计划,如每100个DUT。这样就在保证有效的生产测试的同时也能给设计和制造工程师反馈回有用的信息。采用这种方法,有效的测试时间可以定义为:

例如,如果生产测试讣划的执行时间为2.0s并且每50个DUT(N=50)执行为期60s的特性测试,那么有效的测试时间为3.16s。当产品成熟和需要更少的反馈信息时,就可以通过增加N来降低有效的测试时间。如果N增加到200,那么有效的测试时间就变为2.29s。

射频晶片探针测试

传统上,尤其在RF测试领域,晶片探针测试通常会被封装测试代替,这是因为早期的晶片探针和晶片探针接口的设计难于处理在RF频段上接口之间产生的寄生电容和电感问题,噪声的处理同样也是一个大的问题,然而,随着SIP(System-in-a-package)的出现使封装更复杂和相应的封装成本上升,以及直接销售KGD(Know-good-die),这些改变使得晶片探针测试很有必要。而且,由于不同功能的晶粒(die)组合在一个封装里,举一个坏的情况,一个良率低的便宜的晶粒可能损害整个封装,使得价格昂贵的晶粒(加上封装)都没用。这些需求驱动着RF晶片探针测试技术前进。

SIP的概念同样进入整合的范畴。对于SIP,测试可以在封装后进行,也可以在各个部分整合之前晶片阶段进行。通常,在大部分封装测试前,各个组成的晶粒需要单独进行探针测试,对于RF芯片,现在晶片级必须进行测试,但是在过去对于RF芯片这些测试是尽量避免的。结果就是,KGD使得RF芯片的晶片探针测试逐渐成为主流。

SIP与SOC

SOC的正式定义是在单一芯片上构建一个系统,然而,近引入了多个晶粒在一个封装中,即SIP技术已经发展起来了。在SOC芯片中,核(Core)是在硅片级被整合的。在SIP中,同样的整合是在封装级发生的。随着SIP的出现,不同的IP(Intellectual Property)可以用在同一个封装内。实际上,在某些情况下,不同厂家的晶粒(die)也可以在一起使用。讲到这里我们必须引入一个“内核”的术语,所谓内核是指一个功能模块、电路模块或单独的IP。内核这个术语在传统的SOC芯片设计和测试领域已经使用很多年了,这个概念对于RF测试工程师来说有一点新,这主要是因为只是在近独立的RF芯片功能模块(如低噪声放大器,混频器等)才与数字或模拟功能模块放到同一个晶粒(die)中。RF内核放到SOC或SIP中这两种集成方法的主要不同是各自相应带来的成本好处,这些好处可以分别通过其内部使用核的函数表达,这两种集成方式的不同包括:其内核预期的良率和产品封装的成本。就像决定是去测试各个单独内核还是测试整个SIP,这也是各个独立内核良率的函数。考虑到这里,SIP的整体良率就变成下式:

YSiP=Ycore1&TImes;Ycore2×…×YcoreN

因此,可以非常明显的看到,在一个SIP中有越多的核,SIP的整体良率越依赖于其封装中各个单独核的良率。而且,只要有一个良率不好的核就会导致许多其它好的核和整个封装报废。然而,从正面来看,如果制造过程得到了很好的控制并且良率很高,等到所有的晶粒被封装成SIP时,那么测试的成本就会有非常大的减少,尤其当系统级的测试得以实现时。

设计工程师的新责任

在传统的数字测试领域,终测的算法通常是由芯片的设计人员提供的,而且经常把这些算法写入芯片中。通常,设计人员和测试工程师在整个产品的生命周期中都不会有合作机会。然而,随着芯片集成度的提高,很多事情都发生了改变,如设计人员和测试工程师就必须共同工作解决测试问题。例如,在RF领域,设计人员必须打破成规努力向前看,为新的生产测试方法规划策略和芯片架构。对于RF 、SOC和SIP,除了要考虑成本和管理的问题,还有一些其它的因素需要考虑。它们是:

(1)如何利用RF内核的工程设计和分析工具(EDA)去处理测试成本问题。

(2)没计人员和测试工程师如何积极配合去创建一个具有成本优势的可测性设计(DFT)架构。

(3)如何与测试开发团队合作争取更快的产品上市时间。

数字内核(Core)测试可以使用功能测试或结构测试的方法达到。在过去的几年中,在降低测试成本方面,EDA公司取得主要大的进步是在其工具中引入测试程序产生数据压缩和诊断能力。这些能力可以加速产品面市的时间,降低测试时间,利用低成本的测试机台,EDA公司在数字领域和模拟领域的内置自检技术(BIST)的竞争优势显著增加。但是,估计这样一个优势在RFBIST架构普遍应用之后的一段时间内就会消失,这就意味着RF内核可能成为SOC或SIP芯片中测试成本的部分。当前只有ATE公司在集成的RF内核方面可以提供一些形式的成本降低,另外并行测试的执行需要ATE机台的支持,并行测试是在芯片级进行的,它利用了SOC和SIP芯片内核整合的优点,把多颗芯片(Multi-site)并行测试的概念扩展到同一芯片的多内核(Muti-core)测试中,并行测试需要内核可以独立的访问和控制,这种独立性是可以由SIP芯片的RF内核物理隔离或SOC芯片在设计阶段使IP内核物理隔离达到。在SOC和SIP中,当RF内核可以单独测试或与其它内核并行测试时,它可以与其它测试时间相当的内核共享同样测试时间,从而降低整个测试时间。并行测试必须通过设计人员和测试工程师的合作才能达到。

在SIP中,当有—个物理隔离的晶粒(die),提供封装的连接并不会降低其访问和控制的独立性,因此并行测试应用并不会影响芯片的设计周期。测试工程师只需从设计人员处获得有限信息的就可以执行并行测试,如果说芯片的集成度提高和测试成本降低的需求使得设计人员和测试工程师在项目的早期就必须进行高层次的交流,那么,分离内核的并行测试和RFDFT成功应用就需要测试工程师和设计工程师更直接的交流了,只有通过这样的交流才能了解:并行测试方法对测试时间减少带来的好处以及产品上市时间对这些设计修改的要求。

在SOC芯片出现之前,测试工程师通常被分配给一个芯片并且要求负责实现由设计人员或市场需求定义的所有的测试项目。对于多内核的SOC芯片,通常不期望一个测试工程师具备测试SOC中所有技术(如RF,混合信号,数字信号)的能力,更不期望一个工程师的努力就能够达到产品面市的时间。现在,通常由多个工程师在一起合作测试一个芯片,通过他们不同的测试程序的整合来应用到的晶片或封装测试中,这种在测试领域新的组织结构使得ATE能够提供平滑的测试整合。

RF内置自检测试技术

内置自检测试技术在数字电路的设计和测试中已经使用很多年了,但是在RF电路中应用还是初期。BIST测试的目的是去发现晶体管级的缺陷,一个传统上不为RF测试工程师注意的更细的级别。

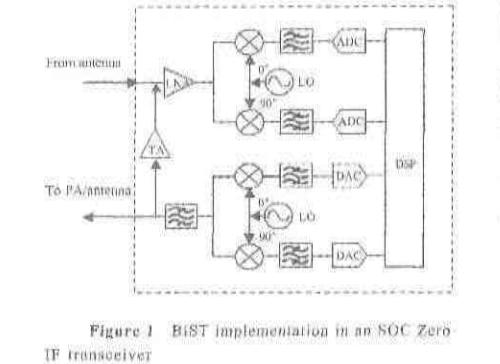

近,在RF芯片上实现BIST的研究已经出现。图1显示了现代零中频(ZIF)无线收发器的架构图。整合出现在所有的功能模块,除了功率放大器,双王器和天线,要么是在同一个硅片上或在同一个封装里 ,在这个例子中,BIST在基带上的实现是通过模数和数模转换器之间的回环测试来实现的,传统上,在RF BIST实现之前,BIST技术是首先在基带部分实现的。,为了执行RF BIST,基带的DSP用激励信号发给射链路,然后通过测试放大器(TA)和接收链路回到基带信号处理器来进行分析。测试放大器在芯片的正常工作时是关机的,而且,必须考虑到测试放大器损坏带来的影响,在这样的情况下,必须做出决定是丢弃整个DUT,还是选择替代的测试方法重新测试。

典型的测试信号是由基带信号发生器产生伪随机序列。典型的BIST算法是产生比特序列,把它进行变换以后送给发射链路,然后通过测试放大器(TA)送到接收链路,再变换后送回到基带处理器,得到比特误码率(BER)。这种方法的一个缺点是诊断问题能力比较低。例如,导致BER比较差的原因可能有:发送链路和接收链路的增益不够;某个放大器的非线性失真;某个RF或混合信号内核的噪声系数不好。

测试系统的架构

随着把RF部分整合到已经具有高速数字电路和混合信号电路的芯片中,单一信号方案的测试系统不再能够测试这样的芯片。在市场上,有众多具有不同功能的测试系统,另外,市场的需求也将使得测试机台整合度提高,这会使得只有RF测试功能的机台消失。在自动测试领域,同时具有模拟、数字和RF测试能力的测试机台已经出现了,就像芯片整合的演化过程一样。如图2所示的测试系统,就是为了迎接市场对测试能力覆盖广的需求而出现的,它具有足够的灵活性以适应不同的市场需求。

结论

芯片的结构和测试成本下降的要求正在改变着测试的方法。在本文中已重点讨论了六大现今主要方面的变化。

随着技术能力的提高和市场的需求,把RF整合到SOC(或SIP)中已经成为一个标准,与模拟、高速电路和数字内核的整合一样,RF的整合使得需要利用RFBIST的优势去进一步减少测试成本。

在硬件层次上,RF可测性设计(DFT)变得有价值并且测试现代SOC芯片的ATE设备是那些可以处理多技术(如RF,混合信号,基带信号,内存和电源管理),并且具有和并行测试能力的测试系统。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。