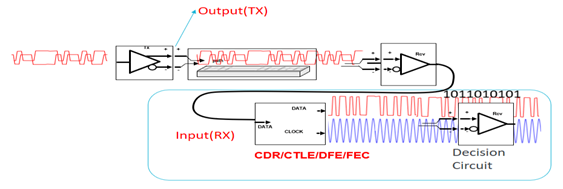

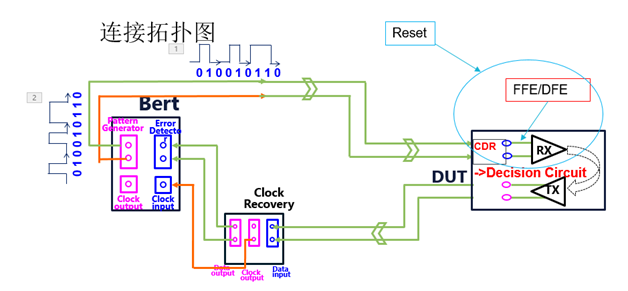

在用户进行系统或者芯片测试的时候,一般主要验证几个方面的性能和可靠性,包括系统发送端的信号质量,链路的损耗/串扰,接收端的容限。如下图1,一个链路系统的基本架构。通常在发送端会使用FFE来补偿链路的损耗,接收端会采用DFE/FFE等方法来进行均衡,一些比较高速率的标准如PCIE 4.0/5.0,SAS4等还会采用FEC来进行纠错,当然接收端还需要CDR来从串行信号里面进行时钟恢复得到同步时钟来对信号进行采样。

图1:高速串行链路的基本架构

对于系统/芯片的接收端测试,会有几个方面的挑战,是loopback (环回)模式的Training,第二是link(链路)training。只有这两个部分的协商正确完成的前提下,才能保证测试的顺利完成。不管是loopback training 还是link training,都要求Bert具备和被测设备自动的协商功能,通过基于协议的握手和双向沟通去使被测设备进入环回模式和均衡的自适应。

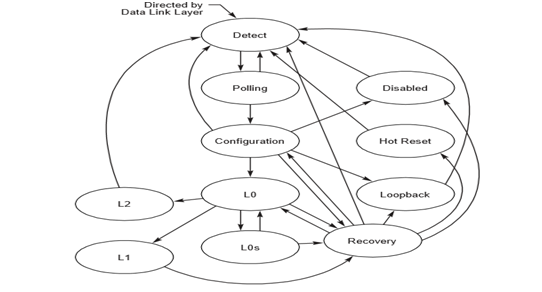

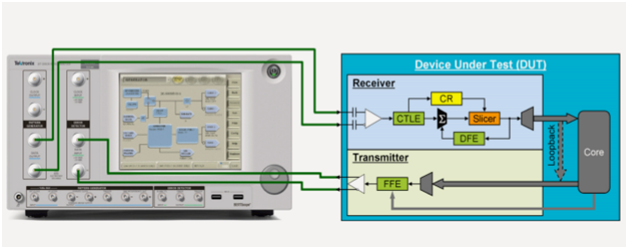

如图二,支持各种协议的系统/芯片在上电后会通过与对端设备的多次协商进入不同的子状态机,在接收端容限测试的时候需要使被测芯片的状态机从Config或者Recovery状态进入loopback的子状态,这个实现需要Bert模拟一个真正的对端设备去发送符合该协议的码型系列去training 被测设备。同时Bert也要能实时的解析被测设备的协议系列以确认其是否被成功training,否则需要重新修改设置来发送training的码型序列。如图3,泰克的BSX系列误码仪可以支持单通道32Gbps的实时数据发送和接收,可以直接产生和接收并同时解析协议的数据包,而不像其他厂商只能在较低速的时候实现数据直接产生和接收,而高速标准则需要通过两个通道合并成单通道进行发送,并在接收端则将单通道再分解成两个通道进行接收。这样会导致高速标准的时候不能实现真正基于协议的协商。

图2:PCIe/USB3.1等协议标准的各种状态机。

图3:BSX系列误码仪支持单通道的高速协议数据的发送和接收解析

如图3,除了loopback training以外,另一个重要的步骤是link training(链路协商),需要Bert和DUT进行FFE/DFE的实时协商来补偿链路的损耗,以达到的误码率。在USB3.1/PCIe协议中发送端会有多个级别的FFE来灵活对信号发送端进行均衡补偿,在接收端也会有CTLE和DFE多级组合来进行补偿。(详细的链路协商步骤细节可以参考泰克的相关应用文章-《克服第4代I/O应用中的接收机测试挑战》)。这个链路协商同样需要Bert能够在一定程度上去模拟一个真实设备和被测设备进行沟通,解析并响应被测设备的要求去调节信号输出的FFE参数,并根据误码率来请求被测设备调节其输出的FFE参数和接收端的CTLE/DFE参数,以达到的误码率。同样这个时候也需要BERT具备单通道直接输出和接收并解析基于协议的码型序列达到与被测设备的实时协商。

除了进行一致性测试以外,对于芯片的验证过程中还经常会进行问题定位,当出现误码的时候,大部分工程师会去搬一台示波器来使用示波器观察信号波形来进行抖动和眼图分析来进行调试,这时候得把信号重新连接到示波器来进行信号的捕获,而且并不容易把误码和示波器捕获的波形直接关联起来找到误码的原因。往往你旁边并没有一台高带宽示波器供你随意使用。由于泰克的BSX系列误码仪能够的统计误码的个数和误码出现的时间,所以能够实现精准的误码定位。这个强大的误码定位功能和抖动眼图分析功能可以供你进行系统和芯片级别的调试,下面会举一些真实用户使用Bert进行调试分析的实例来说明。

一:使用误码仪Error Free interval功能来验证芯片的自适应时间。

客户在做芯片IP的选型验证,该芯片支持的速率为20.62bps,不同IP厂商会给出不同的芯片自适应时间,一般为几百微妙到几百毫秒不等,如前面所述,有一些芯片的关键参数会影响到这个自适应时间,如芯片的FFE/DFE的均衡自适应时间,CDR的锁定时间,误码判决电路的采样点的自动调节等。客户的需求是测试从芯片开始初始化那一刻直至误码率低至10^-12左右的时间。

图4:连接拓扑图

先按照上面图4的连接图连接好,将被测芯片设置为环回模式,设置Bertscope的PG输出为被测速率,码型设置为PRBS31,确认CDR模块可以正确锁定,Error Detector能够正确的Sync码型,并且测试没有误码。将Bert 的Error Detector端设置为Auto-resync。

然后选择Bert scope的View里面的误码分析功能(Error analysis),选择Error free interval。点击Error free interval界面,设置,Hist的end 为500000(bit),这个参数需要根据芯片的特性灵活调节,如果芯片的自适应时间较长,则可以适当增加,以保证整个自适应过程的误码变化情况都能够在所选的时间范围之内。这个界面的横轴是bit,可以根据信号的速率转化为的时间,纵轴是误码个数。我们可以根据误码的变化从而计算出自适应的收敛时间。设置好以后点击auto center。然后点击Run。

设置好误码仪后,用命令将芯片的RX部分进行hot reset,这时候芯片会进行时钟恢复的同步,重新调节DFE,FFE,在Bertscope的Error Free interval里面就可以看到出现大量误码然后再慢慢减少到没有误码的过程。在300000bit左右就不再出现误码,表示这个时候自适应过程就已经完成。为了保证测试结果的重复性和一致性,建议将这个hot reset的过程做十次,Error free interval会自动将这十次的结果进行叠加。从测试的结果看,芯片的自适应时间约为250000X(1/20.62G)约为12.5us左右。

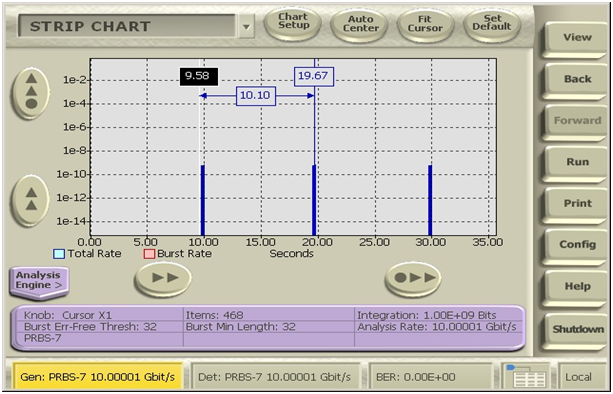

二:使用误码的Strip chart的记录功能来进行长时间的误码分析。

由于客户的系统要进行长时间的(-20到+80度下)的高低温老化测试,客户要看误码的性能和温度变化的相关性,一般的误码仪只能统计温度变化过程中误码的总的个数和误码率,而无法得知在整个十几个小时里面任一时刻误码率的变化。而BSX系列误码仪则可以使用Strip chart的记录功能将整个过程中记录下来,后面可以根据需要查询任意时刻的误码率变化情况。如下图,在第10/20/30秒的时间点出现了一些突发的误码,这个如果仅仅是通过简单的误码统计是无法看到时间相关的细节的,而且其累积记录时间可以长达几十小时甚至几天。

图5:使用Strip chart功能记录整个长时间老化过程误码变化

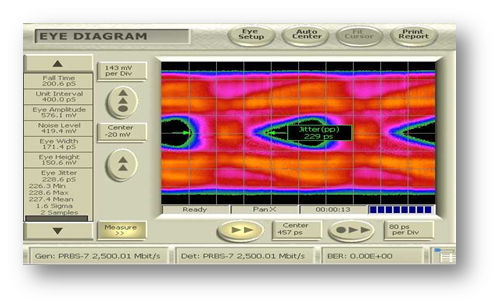

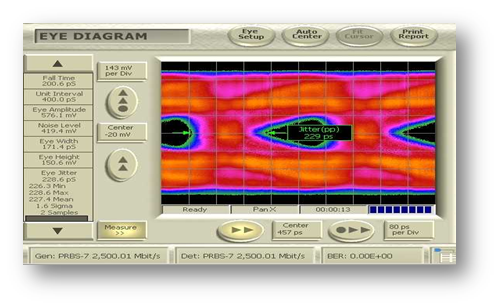

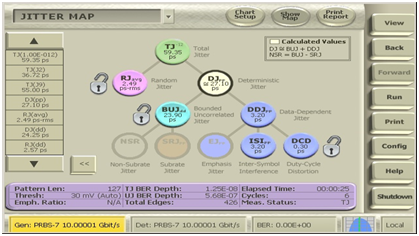

四:使用误码仪的眼图和抖动分析功能进行信号特性的分析。

1.客户在测试误码的同时想快捷的观察TX端输出信号的质量,确保芯片输出的信号是否满足一定的要求。2.客户想真正的测试10^12次方下的总体抖动的值,因为一般示波器的Tj都是通过测量RJ和DJ然后再通过一定的外推算法去得到10^12 次方下的抖动的,由于示波器存储深度和计算时间的限制,无法得到真正的Tj@10^12。但误码仪是可以通过连续bit的测量从而得到真正的10^12的抖动的,并且其内置的带有两个1bit的ADC在实时全速的对每个bit进行扫描和比较,所以能够快速的得到信号的眼图(如图7)。并根据每个bit的与采样点的偏差计算该bit的TIE的抖动偏移量,从而通过算法计算信号的Rj/Dj并进行抖动的进一步细分。同时由于BSX系列的误码检测输入端的带宽高达22GHz以上,所以对高速信号的眼图和抖动分析的非常高。

图6:Bertscope的误码检测端自带的两个1bit ADC的比较器

图7:眼图分析功能

图8:抖动分析功能

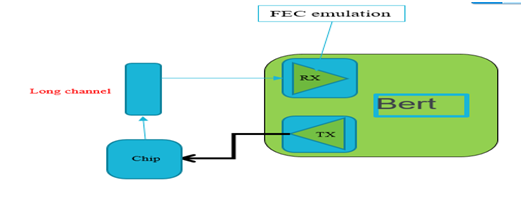

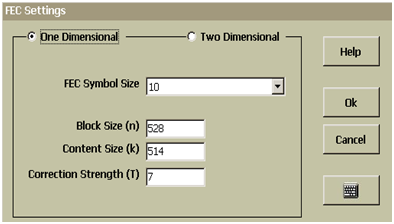

五:使用误码仪的FEC emulation 功能快速模拟芯片的FEC算法。

由于现在芯片和标准的速率越来越高,为了加强容错能力,如SAS4/PCIe 4.0/5.0/25G以太网的标准都广泛使用了FEC来进行纠错,即便是牺牲了一些额外的开销,但能够很大的降低误码率,也是值得的。客户的芯片的接收端可以支持FEC的纠错功能,但要测试在不同的channel条件和不同的发送端均衡的设定下,芯片经过FEC后的误码率能降低到多少,如果将信号直接环回到芯片的输入端的话,需要不停的修改芯片的FEC的参数来进行测试,但由于其芯片每修改FEC的参数如FEC的symbol size, block size,content size等等都需要重新对芯片进行代码编译和,每次需要几分钟的时间,由于不同的条件都要测试,则组合数量很多,导致测试效率非常低。但是BSX系列误码仪的FEC功能能够灵活实时的调节上述各种FEC的参数,并且实时的更新经过FEC后的误码率变化情况,而完全不需要重新芯片的代码(如图11和图12)。大大的提高了测试和调试的效率,而且客户也做过认真的对比,误码仪对FEC后计算得到的误码率和其真实芯片经过FEC的误码率是非常匹配的。这个功能使客户之前几天的时间进行调试过程缩短到一天之内完成,作为泰克工程师的我之前也没有怎么用过这个功能,觉得它是个鸡肋,当现场看到客户的调试过程后也是感叹不已。

图9:用户的测试拓扑结构

图10:RS-FEC的设定,可以任意修改,即使生效。

图11:FEC的仿真功能,实时计算出FEC之前和之后的误码率的变化。

六:使用BSX的pattern sensitivity的功能定位误码出现的特定比特位.

在客户进行误码测试的时候,由于链路的损耗和芯片的输出特性,导致出现了误码,但客户却想知道究竟是哪一个bit位出现了误码,以定位误码出现的根源。设置Bert的输出/输入端设置为PRBS7的码型,在误码分析功能里面选择Patten Sensitivity,则可以直接观察PRBS7的127个比特的每一位所出现误码的个数,看多误码所对应的比特位的前后特性,如下图十三,移动光标到任意一个比特上面,可以看到连续多个0而中间有一个1跳变的bit即127比特的第94比特出现误码的个数多,达到5043598个误码。从而判断由于链路ISI的影响导致突然的跳变位出现较高的误码率。

图12:基于码型系列的误码定位

从上述的用户实际可以看出,Bertscope 的眼图抖动和误码定位分析可以给客户带来很多调试的手段,把时域和误码极好的相关联起来,帮用户极大的提高了测试和调试的效率。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。