(注:表笔为1倍倍率)

CT脚在494芯片内部接两个重要的比较器的反相端。理解CT脚上的锯齿波,是理解494波形产生过程的关键之一。

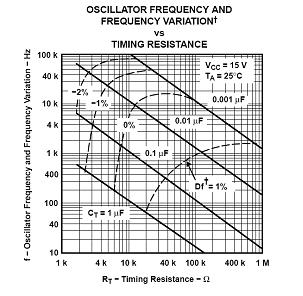

下图,是德州仪器数据表中494的CT、RT的取值与振荡频率的关系图。

不难看出,当RT恒定时,振荡频率随CT的增大而减小;当CT恒定时,振荡频率随RT的增大而减小。

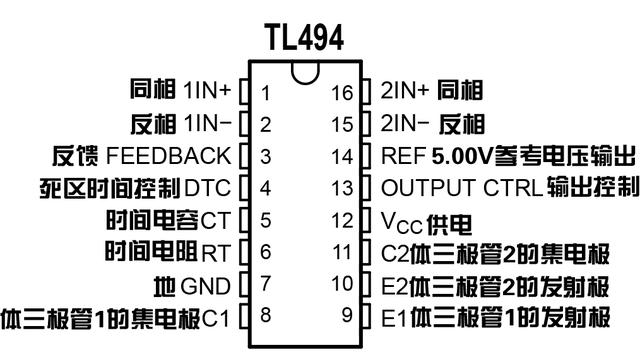

Pin8(C1)、Pin9(E1)、Pin10(C2)、Pin11(E2):他们分别是芯片集成的两个体NPN驱动三极管的集电极、发射极。C1、C2是494发出的驱动方波的源头。但是,这两个体NPN驱动三极管的驱动能力有限,还不足以直接驱动驱动变压器.因此,在电源主板上还设计有与之匹配的两个用于放大驱动方波的NPN三极管(直接驱动驱动变压器)。

Pin12(Vcc):芯片的供电。494的供电来自于辅助电源回路。辅助变压器的刺激绕组有两个抽头,一个抽头产生5VSB供电,另一个抽头产生B+。此脚经整流二极管后与辅助变压器的对应针脚相连。德州仪器推荐的的Vcc范围为7V到40V,实践中实测多为12V到24V。

Pin13(OUTPUT CTRL):输出控制脚。若下拉到地,则芯片集成的两个体NPN驱动三极管会同时截止或导通(两个当一个来用);若上拉到14脚REF,则两个体NPN驱动三极管中的一个在导通时,另一个截止(反之亦然),即它们工作在推挽模式。

Pin13(REF):参考电压输出脚,5V。很多芯片都有参考电压脚。在芯片内部,整个电压是由低压差线性稳压器(LDO)产生的。LDO是一种傻瓜式供电,只要有合适输入,就应该有准确的输出。其重要意义不仅仅是为了提供一路供电,更重要的在于为芯片其他引脚的工作提供了一个可参考的标准环境(REF始终是稳定的,不会变化的5V,)。

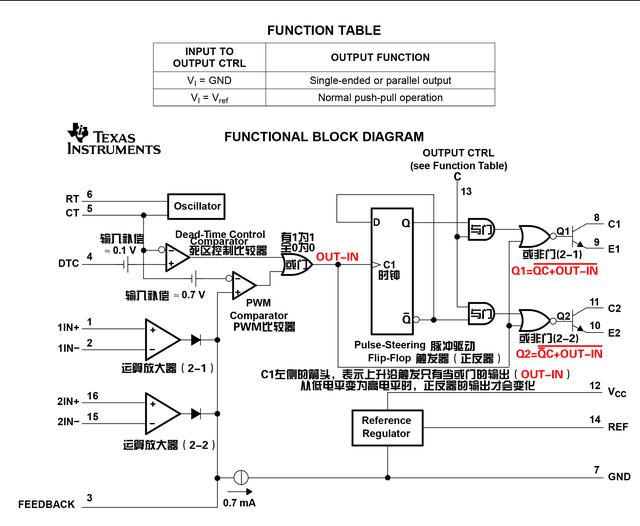

接下来,我们根据其内部框架图来分析一下494的工作原理和过程,如下图所示。

494作为PWM芯片,其功能就是产生驱动方波。那么,494是如何通过四个电平比较元件(两个运算放大器[即1、2脚,16、15脚之间的两个运放]、两个比较器[“死区控制比较器”,“PWM比较器”])来控制后续元件(一个或门、脉冲驱动触发器[正反器]、两个与门、两个或非门)终驱动Q1和Q2,才能产生方波波形呢?

任何PWM芯片在输出振荡之前所需要首先确定的一件事情就是确定其振荡周期(周期的具体时长),494是通过CT的容量和RT的阻值来确定这个事情的:CT经时间电容到地,RT经时间电阻到地。

接下来,以图中或门为界,将图划分为左侧和右侧,并将或门的输出定义为OUT-IN。这是因为对于左侧而言,OUT-IN是的输出,而对于右侧而言,OUT-IN又是其的输入。可见,只要分析清楚了OUT-IN是如何作为输出而产生的,和如何作为输入而引起下级电路发生后续动作的,就能把494产生方波的全部过程分析清楚,这是没有问题的。

我们先分析一下OUT-IN为高电平情况。

作为或门输出的OUT-IN如果为高电平,就说明其两个输入至少有一个为高电平。三种可能的情况如下:

1.死区控制比较器当前输出高电平,PWM比较器当前输出低电平(此可能是正常ATX待机时的真实输出)

2.PWM比较器当前输出高电平,死区控制比较器当前输出低电平(此可能是正常ATX正常工作时的真实输出)

3.死区控制比较器和PWM比较器同时输出高电平(此种可能不存在)

在对这三种可能性做出分析之前,我们首先来思考一个问题:对于正常的ATX而言,“死区控制比较器”和“PWM比较器”这两个比较器究竟谁工作?答案当然是“死区控制比较器”。

有两个理由:1)DTC是开机脚(拉低PSON令ATX电源开机的本质是拉低DTC脚的电压),负责开机的“死区控制比较器”当然应该早于“PWM比较器”而工作。2)既然“PWM比较器”中有PWM的字样,那么说明它有意义的时段一定是在已经有了PWM振荡波形之后,在ATX没有开机的时段,“PWM比较器”是不工作的(存在但无意义)。

实际上,494集成在1、2脚,16、15脚之间的两个运放都是在开机后才工作。他们中的一个被用于稳压控制(本书将494中此用途的体运放称为“稳压运放”),一个被用于保护芯片(关闭Q1和Q2输出,本书将494中此用途的体运放称为“保护运放”)及电源。换句话说,在ATX正常待机时,1、2脚,16、15脚之间的两个运放是不工作的。要真正理解这个问题,就必须了解,1、2、16、15脚的外围电路。

无论是通过实物跑线还是图纸分析。我们会发现,这两个运放的同相脚都是低压直流输出经过阻容反馈网络后来的,而其反相脚要么直接接494的REF(保护运放的反相脚)要么接来自REF的分压电阻(稳压运放的反相脚)。

总之,对于正常的ATX而言,在待机时,PWM比较器不工作,它输出低电平。死区控制比较器的DTC上到高电平,输出高电平。

我们接着分析一下作为下级电路输入的高电平的OUT-IN,重点是分析它对Q1和Q2的控制。

从模块图中不难看出,OUT-IN是两个或非门的输入,当OUT-IN为高电平时,或非门应该输出低电平(此时,两个与门的输出对或非门无影响),即两个体NPN三极管处于截止状态。

有想象力的朋友应该会做如下猜测:既然OUT-IN为高电平时,Q1和Q2截止,那么是不是当OUT-IN为低电平时,Q1和Q2就开始(轮流)导通了呢?事实的确如此。

我们再分析一下OUT-IN为低电平的情况。

作为或门输出的OUT-IN如果为低电平,就说明其两个输入全部为低电平,即死区控制比较器和PWM比较器同时输出低电平。

实际上,当我们短接PSON与地之后,已经人为的拉低了DTC的电平(因为有0.1V的电压补偿,DTC脚电压不会被拉低到0V),而此时“PWM比较器”刚刚开始工作,其输出(开机一刻为低电平)即将根据反馈发生变化。

当OUT-IN为低电平时,或非门的输出开始受触发器和两个与门的影响。作为触发器输出的Q和Q#是反相的,我们可以任意假定一种情况分析。两个与门的一个输入来自13脚OUTPUT CTRL,它要么接地,要么拉高到5VREF。总之,与门的四个输入一共有四种可能。 此文里指分析Q为高电平,Q#为低电平,13脚接地的情况。

当Q为高电平时,上方的与门一个输入为高,另一个输入为低(接地),与门将输出低电平;于此同时,Q#为低电平,下方的与门一个输入为低,另一个一个输入低(接地),与门输出低电平。对于两个或门门而言,其所有输入都是低电平,其输出则都为高电平,Q1和Q2同时导通(Q1和Q2工作在单边模式[single-edge mode]——两个管子当作一个用)。

常识告诉我们,开关管不能不受控制的导通。那么什么时候去关闭它呢?当然是根据反馈。在前面的内容中,我们已经将494两个体运放中的一个命名为稳压运放。接下来,我们就介绍一下这个稳压运放的是如何在合适的时间去关闭开关管的。这个过程,就是主回路的稳压过程。

稳压运放的同相脚外接“反馈”阻容网络,当DTC被拉低后,494并不会立刻去打开开关管,这是因为芯片内置在DTC脚上的0.1V的补偿电压会提供脉宽5%左右的固有死区时间。

这是因为“死区控制比较器”要想输出对应开关管打开的低电平的OUT-IN,CT脚的锯齿波就需要先达到0.1V的电压,从其波形不难看出,锯齿波是从低于0.1V的某个电平线性上升的,必然要经历这段固有死区时间(固有死区的存在是为了保护芯片)。

当锯齿波上升到0.1V后,“死区控制比较器”才能够发出低电平,或非门也才能输出低电平的OUT-IN,Q1和Q2才开始(轮流)导通,主电路回路才开始工作。

当主供电回路开始工作之后,稳压运放通过(反馈)阻容网络对实际输出进行采样,一旦达到了反相脚设定的门限值,稳压运放的输出就从低电平变为高电平,“PWM比较器”的输出也会紧跟着变为高电平,或门也会输出高电平的OUT-IN,终去关闭Q1和Q2。随着负载对输出电能的消耗,实际输出电压有下降的趋势,终会又会导致稳压运放的输出从高电平的输出反相为低电平的输出,芯片将进入下一轮振荡。

感兴趣的朋友,还可以进一步分析一下494的时序图(此图可见于摩托罗拉或FIC公司生产的的494的数据表)。因其已经远远超出了维修需要,在此不再赘述。

综上所述,我们通过分析得到了两个结论。

结论一:在OUT-IN为高电平时,Q1和Q2截止;在OUT-IN为低电平时,Q1和Q2(轮流)导通。

显然,Q1和Q2的截止与导通,必将影响到“双NPN放大电路”中两个NPN放大管的导通与截止。但并没有做如下判定:当Q1或Q2导通时,与之匹配的NPN放大管也随之导通。也没有做如下的判定:当Q1或Q2截止时,与之匹配的NPN放大管也随之截止。因为这与事实不符。因为在ATX待机时,可以在NPN放大管的基极B上测到一个高电平(2.3V左右),既然NPN型的三极管是高电平导通,那么此时的两个NPN放大管究竟是处于放大/饱和,亦或是截止状态呢?(感兴趣的朋友可自行搜索“双NPN放大电路”。)

结论二:导致OUT-IN为高电平的原因有两个:1)“死区控制比较器”输出高电平。2)“PWM比较器”输出高电平。“死区控制比较器”实际上是它激励源的使能,而“PWM比较器”则是它激励源的脉宽调制。二者既有联系又有区别。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。