在选择变量控制下,从多路输入数据中选中某一路数据送至输出端。对于一个具有2n个输入和1个输出的多路选择器,有n个选择变量。

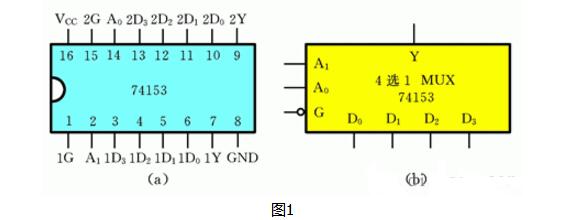

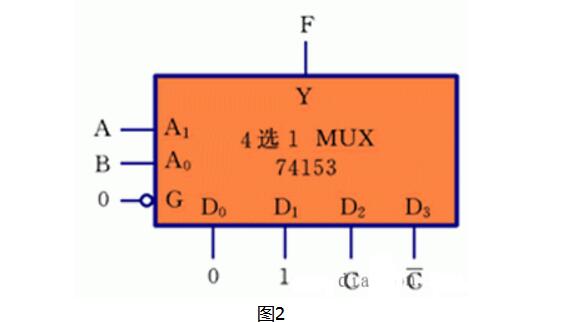

典型中规模多路选择器有双4路数据选择器74153,其引脚排列图和逻辑符号如图1(a)、(b)所示。

数据选择器74153芯片含两个4路数据选择器,每个选择器接收4路数据输入,产生一个输出,两个4路数据选择器共用两个选择变量。芯片有16条引线,其中1D0~1D3,2D0~2D3为8条数据输入线,A1和A0为选择输入线,1Y、2Y为2条输出线,1G、2G为使能控制端,另外有1条电源线和1条地线。

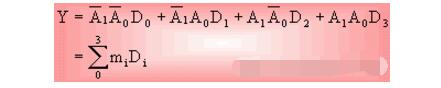

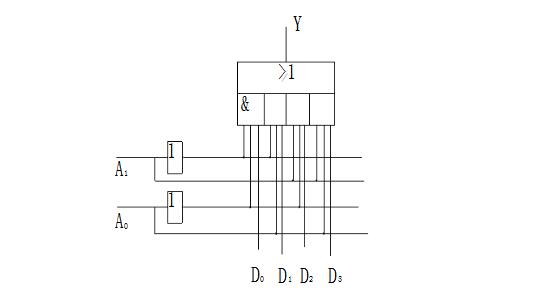

4路数据选择器的输出函数表达式为

式中,mi为选择变量构成的项。

多路选择器除完成对多路数据进行选择的基本功能外,还可用来实现数据的并-串转换、序列信号产生以及实现各种逻辑函数功能。

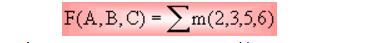

例如采用4路选择器74153实现如下逻辑函数的功能

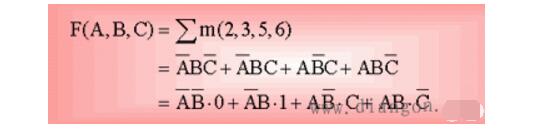

解给定函数为一个3变量函数,由于4路选择器具有2个选择控制变量,所以用来实现3变量函数功能时,应该首先从函数的3个变量中任选2个作为选择控制变量,然后再确定选择器的数据输入。假定选A、B与选择控制端A1、A0相连,则可将函数F的表达式表示成如下形式:

显然,要使4路选择器的输出Y与函数F相等,只需:。据此,可画出逻辑电路如图2所示。类似地,也可以选择A、C或B、C作为选择控制变量,选择控制变量不同,数据输入也不同。

设计背景:

该设计是以数字电子技术为基础,实现数据从四位数据中按照输入的信号选中一个数,来实现所期望的逻辑功能。

设计方案:

用拨码开关作四位数据及两位控制端的输入,LED作输出,通过拨码开关组成控制输入端s1和s0不同组合,观察LED与数据输入端a,b,c,d的关系,验证四选一数据选择器设计的正确性。使用逻辑门电路与、或、非的组合来表达4选1数据选择器,通过控制输入的信号来控制输出的信号值。

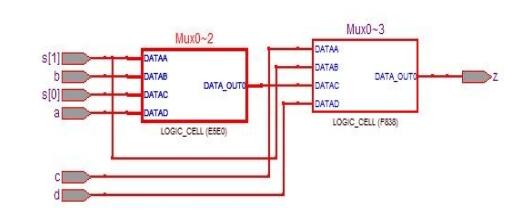

其逻辑电路如下图:

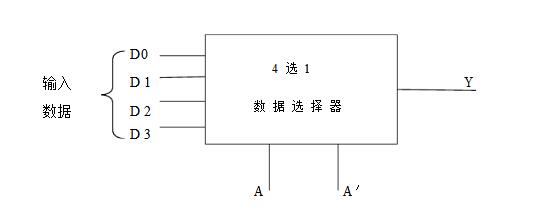

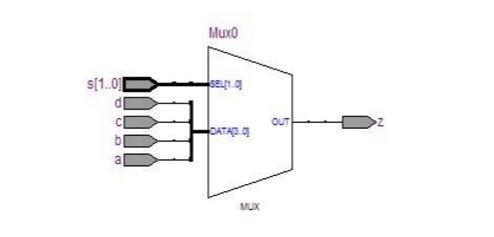

其示意框图如下:

其中输入数据端口为DO、D1、D2、D3,A、A为控制信号,Y为输出。

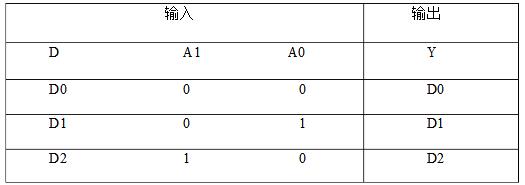

令AA‘=“OO”时,输出Y=D0;

令AA’=“01”时,输出Y=D1;

令AA‘=“10”时,输出Y=D2;

令AA’=“11”时,输出Y=D3;

真值表如下:

(1)设计思路

四选一多路选择器设计时,定义输入s为标准以内漏记为SIDLOGIC输出的信号Z的数据类型定义为2位标准逻辑矢量位STD_LOGIC_VECTOR(1DOWNTO0)。使用LBRATY语句和USE语句,来打开IEEE库的程序包STDLOGIC_1164.ALL。当输入信号时,程序按照输入的指令来选择输出,例如输入信号为“OO”时,将a的值给z,进而输出z的值,输入信号为“11”是,将a的值给z,进而输出z的值。若输入信号是已经定义的四个信号之外的值时(即当正条件语句不满足时),输出值为x,并将x的值给输出信号Z。这样即可实现四选一数据选择的功能。

程序

LIBRARY正EE:

USE

IEEE.STD_LOGIC_1164.ALL:

ENTITYmux41is

PORT(a,b.c.d:NSTD_LOGIC:

INSTD_LOGIC_VECTOR(1

DOWNTO0):

STD_LOGIC):

OUT

END

mux41:

IS

ARCHITECTUREoneOF

mux41

BEGIN

PROCESS(s,a.b.c.d)

BEGIN

IS

CASES

WHEN“00”=》z《=a:

WHEN“01”=》z《=b:

WHEN“10”=》z《=c:

WHEN“11”=》z《=d:

WHENOTHERS=》z《-=null:

END

CASE;

ENDPROCESS:

END

one;

运行结果

当输入信号“OO”时,输出信号z的值为‘a’:

当输入信号“01”时,输出信号z的值为‘b’;

当输入信号“10”时,输出信号z的值为‘c’:

当输入信号“11”时,输出信号z的值为‘d’:

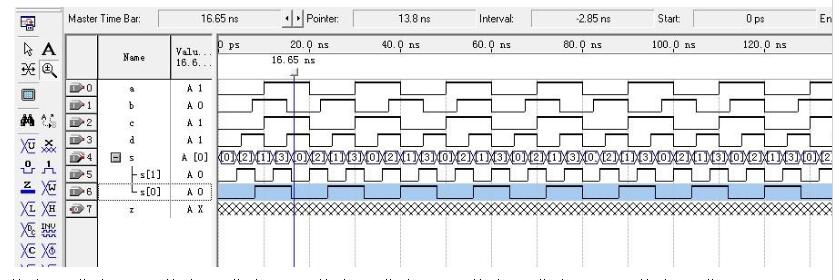

波形仿真及描述

输入:

的波形周期为10ns,b的波形周期为5ns,c的波形周期为15ns,d的波形周期为8nsos[1]的波形周期为5ns.s的波形周期为10ns。

(2)设计思路

定义6个输入信号,一个输出信号,当控制信号A=‘1’时,muxval 的值加1,即muxval=muxva1+1当控制信号 B= ‘1’时muxval的值加2,即muxval-muxval+2。当输入值为‘i0’时,输出q的值为0,当输入的值为“i1’时,输出q的值为1,当输入值为‘i2’时,输出q的值为2,当输入值为‘i3’时,输出q的值为3。

程序

USE 正EE.STD LOGIC 1164.ALL;

ENTITY mus41

IS

(i0ji1,i2,i3,a,b :N STD_LOGIC;

PORT

:OUT

STD_LOGIC );

ENS mux4;

OF

mux4 IS

ARCH ITE CT URE b_mux4

BE G N

Process (i0,il,i2,i3,a,)

Variable

0;

downto

musval

:integer rang

Begin

m uxv al :=0;

if (a=‘l’)

musval:muxval+ l; end if;

then

if (b=‘I’) then

muxval :muxwal + 2; end

if;

is

muxval

case

w hen 0= 》 q 《= i0;

when l= 》 q 《= il;

when2=》q《=2;

when3=》q《=i3;

others= 》null;

When

end

ca se;

end process;

END b_mux4;

运行结果

当输入信号“OO”时,输出信号z的值为‘i0’:

当输入信号“01”时,输出信号z的值为‘i1’:

当输入信号“10”时,输出信号z的值为‘i2’:

当输入信号“11”时,输出信号z的值为‘i3’;

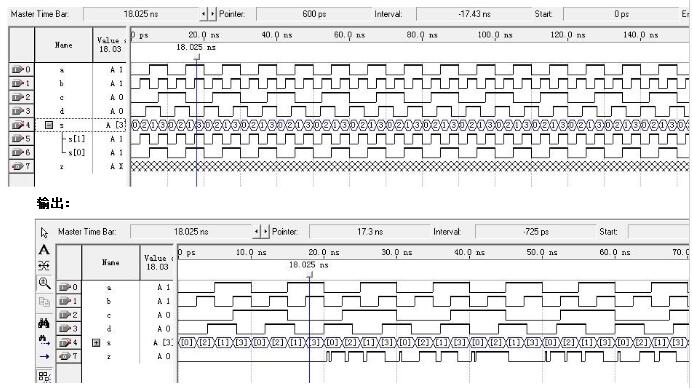

波形仿真及描述

a的波形周期为20ns,b 的波形周期为15ns,c 的波形周期为20ns,d 的波形周期为15ns,s的波形周期为8ns,s的波形周期为16ns。

输出

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。