一、集成门电路

数字集成电路按其内部有源器件的不同可以分为两大类:一类为双极型晶体管集成电路(TTL电路);另一类为单极型集成电路(MOS管组成的电路)。

1.TTL集成逻辑门电路

(1)TTL与非门

CT74S肖特基系列TTL与非门的电路组成如图2-19(a)所示,它由输入级、中间级、输出级3个部分组成。

图2-19 TTL与非门电路图

输入级:由多发射极管VT1和电阻R1组成,多发射极管的3个发射结为3个PN结。其作用是对输入变量A、B、C实现逻辑与,所以它相当于一个与门。

中间级:由VT2、R2和VT6、RB、RC组成,VT2集电极和发射极同时输出两个逻辑电平相反的信号,用以驱动VT3和VT5。

输出级:由VT3、VT4、VT5和R4、R5组成,它采用了达林顿结构,VT3和VT4组成复合管降低了输出高电平时的输出电阻,提高了带负载能力。

TTL 与非门的逻辑符号如图 2-19(b)所示;逻辑表达式为:

对图2-19所示电路,如果高电平用1表示,低电平用0表示,则可列出图2-19所示的真值表,如表2-1所示。

表2-1 TTL与非门真值表

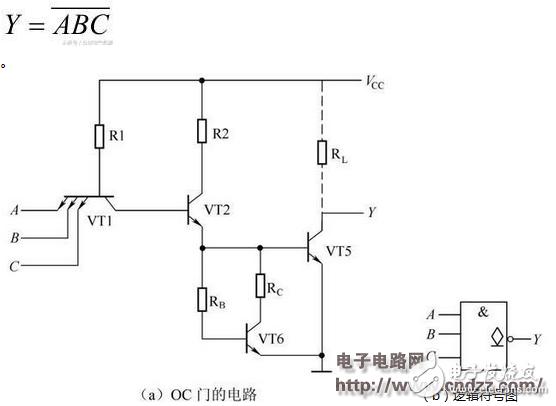

(2)集电极开路与非门(OC门)

① 工作原理。

集电极开路与非门也叫 OC 门,能使门电路输出的电压高于电路的高电平电压值,且门电路的输出端可以并联以实现逻辑与功能,即线与(一般的TTL门电路不能线与)。

OC门的电路如图2-20(a)所示,逻辑符号如图2-20(b)所示,逻辑表达式为:

图2-20 集电极开路与非门及逻辑符号

② OC 门的应用。

OC门可以实现线与,如图2-21所示,逻辑表达式为![]() ;驱动显示器、实现电平转换,如图2-22所示。

;驱动显示器、实现电平转换,如图2-22所示。

图2-21 用OC门实现线与

(3)与或非门

与或非门电路如图2-23(a)所示,逻辑符号如图2-23(b)所示,逻辑表达式为:

图2-22 驱动显示器、实现电平转换

图2-23 与或非门及逻辑符号

(4)三态输出门

三态输出门是指不仅可输出高电平、低电平两个状态,而且还可输出高阻状态的门电路,如图2-24所示,![]() 为控制端。

为控制端。

当![]() =0时,G输出P=1,VD截止,输出Y=

=0时,G输出P=1,VD截止,输出Y=![]() ,三态门处于工作状态。

,三态门处于工作状态。![]() 低电平有效。

低电平有效。

图2-24 三态输出与非门及其逻辑符号

当![]() =1时,G输出P=0,VD导通,输出高阻状态。

=1时,G输出P=0,VD导通,输出高阻状态。

2.CMOS集成逻辑门

和 TTL 数字集成电路相比,CMOS 电路的突出特点是微功耗、高抗干扰能力。

(1)CMOS反相器

由两个场效应管组成互补工作状态,如图 2-25 所示。逻辑表达式为:

图2-25 CMOS 反相器

(2)CMOS与非门

如图2-26所示,两个串联的增强型NMOS管VTN1和VTN2为驱动管,两个并联的增强型PMOS管VTP1和VTP2为负载管,组成CMOS与非门,逻辑表达式为: 。

。

(3)CMOS或非门

如图2-27所示,两个并联的增强型NMOS管VTN1和VTN2为驱动管,两个串联的增强型PMOS管VTP1和VTP2为负载管,组成CMOS或非门,逻辑表达式为:

图2-26 CMOS 与非门

图2-27 CMOS 或非门

(4)CMOS传输门

将两个参数对称一致的增强型NMOS管VTN和PMOS管VTP并联可构成CMOS传输门,电路和逻辑符号如图2-28所示。

图2-28 CMOS 传输门及逻辑符号

(5)CMOS三态门

图 2-29(a)所示为低电平控制的三态门输出,图 2-29(b)为逻辑符号。

图2-29 CMOS 三态门输出及逻辑符号

当![]() 时,VTP2和VTN2导通,VTN1和VTP1组成的CMOS反相器工作,所以

时,VTP2和VTN2导通,VTN1和VTP1组成的CMOS反相器工作,所以 。

。

当![]() ,VTP2和VTN2同时截止,输出Y对地和对电源VDD都呈高阻状态。

,VTP2和VTN2同时截止,输出Y对地和对电源VDD都呈高阻状态。

(6)CMOS异或门

图2-30(a)所示为异或门,图2-30(b)为逻辑符号。

图2-30 CMOS 异或门及逻辑符号

当输入A=B=0或A=B=1时,即输入信号相同,输出Y=0;当输入A=1或B=1时,即输入信号不同,输出Y=1。其真值表如表2-2所示。

表2-2 异或门真值表

3.复合门电路

除了上述介绍的逻辑门电路外,还有或非门、异或门、同或门等,表2-3是基本门和常用复合门的逻辑符号、逻辑表达式及逻辑功能。

表2-3 基本门和常用复合门的对照表

二、组合逻辑电路

逻辑电路在任何时刻的输出状态只取决于这一时刻的输入状态,而与电路的原来状态无关,则该电路称为组合逻辑电路。

1.组合逻辑电路的分析方法

(1)分析步骤

① 根据给定的逻辑电路写出输出逻辑关系式。一般从输入端向输出端逐级写出各个门输出对其输入的逻辑表达式,从而写出整个逻辑电路的输出对输入变量的逻辑函数式。必要时,可进行化简,求出输出逻辑函数式。

② 列出逻辑函数的真值表。将输入变量的状态以自然二进制数顺序的各种取值组合代入输出逻辑函数式,求出相应的输出状态,并填入表中,即得真值表。

③ 根据真值表和逻辑表达式对逻辑电路进行分析,确定其功能。

(2)分析举例

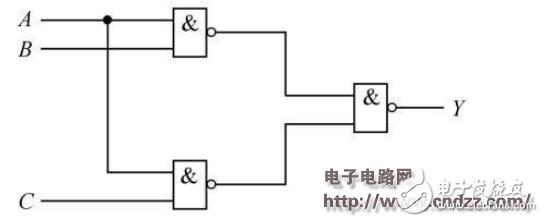

分析图2-31所示逻辑电路的功能。

图2-31 逻辑电路

① 写出输出逻辑函数表达式:

② 列出逻辑函数的真值表。将输入A、B、C取值的各种组合代入式(2-5)中,求出输出Y的值。由此列出真值表,见表2-4。

表2-4 真值表

续表

③ 逻辑功能分析。由表2-4可知:在输入A、B、C这3个变量中,有奇数个1时,输出Y为1,否则Y为0,由此可知,图2-34为这3位奇校验电路。

2.组合逻辑电路的设计方法

(1)设计步骤

组合逻辑电路的设计,应以电路简单、所用器件少为目标,其设计步骤为:

① 分析设计要求,列出真值表;

② 根据真值表写出输出逻辑函数表达式;

③ 对输出逻辑函数进行化简;

④ 根据简输出逻辑函数式画逻辑图。

(2)设计举例

设计一个A、B、C3个人表决电路。当表决某个提案时,多数人同意,提案通过,同时A具有否决权。用与非门实现。

① 分析设计要求,列出真值表,见表2-5。设A、B、C同意提案用1表示,不同意用0表示,Y为表决结果,提案通过为1,通不过为0。

表2-5 真值表

续表

② 将输出逻辑函数化简,变换为与非表达式。由图 2-32 的卡诺图进行化简,可得

图2-32 卡诺图

将上式变化为与非表达式

③ 根据输出逻辑函数式(2-6)画逻辑图,如图2-33所示。

3.组合逻辑电路中的竞争冒险

(1)竞争冒险现象及其产生的原因

信号通过导线和门电路时,都存在时间的延迟,信号发生变化时也有一定的上升时间和下降时间。因此,同一个门的一组输入信号,通过不同数目的门,经过不同长度导线的传输,到达门输入端的时间会有先有后,这种现象称为竞争。

图2-33 逻辑电路

逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲(又称过渡干扰脉冲)的现象,称为冒险。如图2-34所示。

图2-34 产生正尖峰干扰脉冲冒险

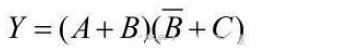

(2)冒险现象的判别

在组合逻辑电路中,是否存在冒险现象,可通过逻辑函数来判别。如果根据组合逻辑电路写出的输出逻辑函数在一定条件下可简化成下列两种形式时,则该组合逻辑电路存在冒险现象,即:

例如,函数式 ,在A=C=0时,

,在A=C=0时, 。若直接根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。

。若直接根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。

(3)消除冒险现象的方法

①增加多余项。例如: ,当A=1,C=1时,存在着竞争冒险。根据逻辑代数的基本公式,增加一项 AC,函数式不变,却消除了竞争冒险,即

,当A=1,C=1时,存在着竞争冒险。根据逻辑代数的基本公式,增加一项 AC,函数式不变,却消除了竞争冒险,即 。

。

② 加封锁脉冲。在输入信号产生竞争冒险时间内,引入一个脉冲将可能产生尖峰干扰脉冲的门封锁住。封锁脉冲应在输入信号转换前到来,转换后消失。

③ 加选通脉冲。对输入可能产生尖峰干扰脉冲的门电路增加一个接选通信号的输入端,只有在输入信号转换完成并稳定后,才引入选通脉冲将它打开,此时才允许有输出。

④ 接入滤波电容。如果逻辑电路在较慢速度下工作,可以在输出端并联一电容器。由于尖峰干扰脉冲的宽度一般都很窄,因此用电容即可吸收掉尖峰干扰脉冲。

⑤ 修改逻辑设计。

三、时序逻辑电路

与组合逻辑电路不同,时序逻辑电路在任何一个时刻的输出状态不仅取决于当时的输入信号,而且还取决于电路原来的状态。

1.同步时序逻辑电路的分析方法

(1)分析步骤

① 写方程式。写出时序逻辑电路的输出逻辑表达式(即输出方程)、各触发器输入端的逻辑表达式(即驱动方程)和时序逻辑电路的状态方程。

② 列状态转换真值表。将电路现状的各种取值代入状态方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。

③ 逻辑功能的说明。根据状态转换真值表来说明电路的逻辑功能。

④ 画出状态图和时序图。

(2)分析举例

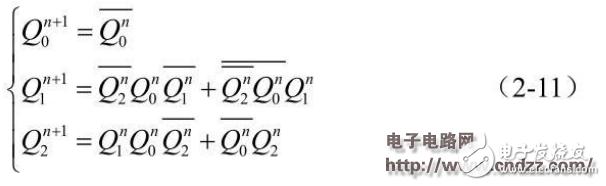

分析图 2-35 所示电路的逻辑功能,并画出状态转换图和时序图。

图2-35 待分析逻辑电路图

① 写方程式:

输出方程:![]()

驱动方程:

状态方程:将驱动方程式代入 JK 触发器的特性方程Qn+1=![]() ,得到电路的状态方程为

,得到电路的状态方程为

②列状态转换真值表:该电路的现状为![]() ,代入输出方程(2-9)和状态方程(2-11)中进行计算后得 Y=0 和

,代入输出方程(2-9)和状态方程(2-11)中进行计算后得 Y=0 和![]() ,然后再将001当作现态代入状态方程式(2-11),得

,然后再将001当作现态代入状态方程式(2-11),得![]() ,以此类推。可求得可求得表2-6所示的状态转换真值表。

,以此类推。可求得可求得表2-6所示的状态转换真值表。

表2-6 状态转换真值表

③ 逻辑功能说明:由表2-6可看出,图2-35所示电路在输入第六个计数脉冲CP,返回原来的状态,同时输出端Y输出一个进位脉冲。因此,该电路为同步六进制计数器。

图2-36 状态转换图和时序图

④ 画状态转换图和时序图。根据表2-6可画出图2-36(a)所示的状态转换图。图中的圆圈内表示电路一个状态,箭头表示状态转换方向,箭头线上方标注X/Y为转换条件,X为转换前输入变量的取值, Y为输出值,由于本例没有输入变量,故X未标上数值。

2.同步时序逻辑电路的设计方法

同步时序逻辑电路的设计和分析正好相反,根据给定逻辑功能的要求,设计同步时序逻辑电路。设计的关键是根据设计要求确定状态转换的规律和求出各触发器的驱动方程。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。