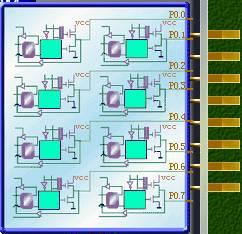

8051单片机有四个8位并行I/O端口,记作P0,P1,P2和P3.每个端口都是8位准双向口,共占有32条引脚。每一条I/O线都 可以独立的用作输入或输出。

每个端口都包括锁存器,一个输出驱动器,作输出时数据可以锁存,作输入时数据可以缓冲。在无片外扩展存储器的系统中,这四个端口的每一位都可以作为准双向通用I/O端口使用。

在具有片外扩展存储器系统中,P2口送出高8位地址,为双向总线,分别送出低8位地址和数据输入/输出。8051单片机四个I/O端口的电路设计非常巧妙,熟悉I/O端口逻辑电路,不但有利于正确合理地使用端口,而且会对设计单片机外围逻辑电路有所启发。

P0口的每一位由一个输出锁存器 ,二个三态输入,输出驱动电路,控制电路与门,器,MUX控制构成。当CPU使控制线C=0时,数控开关MUX向下,P0口为通用I/O口;当C=1时,开关拔向反相器的输出,端口分时为地址/数据总线使用。

我们先来看P0口作为I/O口使用的情况:

当8051组成的系统无外扩存储器,CPU对片内存储器和I/O口读写时 。执行MOV指令,或EA=1的条件下执行MOVC指令时,由硬件自动使控制线C=0,开关MUX倒向下,它输出级T2与锁存器的Q反端接通;同时,因与门输出为0,输出级中的上拉场效应管T1处于截止状态,因此,输出级是漏极开路电路。这时P0口可作一般I/O口用。

一般I/O口又有输入和输出两种操作,我们先来看看P0用作输出口的情况。当CPU执行输出指令时,写入脉冲加在D锁存器上,这样与内部总线相连的数据取 反相后就出现在Q上,若D端数据为0,则反端数据为1,场效应管T2导通,输出0.此时引脚被拉成高,这样数据总线上的信号1被准确的送出到引脚上 。

8051有几条输出指令功能特别强,属于“读-改-写”指令。例如,执行一条ANL P0,A。指令的过程是:不直接读引脚上的数据,而是读P0口D端锁存器中的数据,当“读锁存器”信号有效,三态缓冲器1导通,Q端数据内部总线和累加器A中的数据进行“逻辑与”操作,结果送回P0端口锁存器。此时,锁存器的内部和引脚是一致的。

下面分析P0口作输入口的情况,缓冲器2用于CPU直接读口数据。当执行一条由端口输入的指令时,“读引脚”脉冲把该三态缓冲器打开,这样,端口上的数据经过缓冲器2读入到内部总线。这类操作由数据传送指令实现。在读入端口引脚数据时,由于输出驱动场效应管T2并接在引脚上,如果T2导通就会将输入的高电平拉成低电平,以至于产生误读。所以,在端口进行输入操作前,应先向端口锁存器写入“1”,也就是使锁存器Q反=0,因为控制线C=0,因此T1和T2截止,引脚处于悬浮状态,可作高输入。

下面我们看看控制线C=0时,P0口作为地址/数据总线使用的情况。当8031外扩存储器组成系统,CPU对外存储器读写,CPU片外存储器读写,即执行MOVX指令,或在EA=0的条件下执行MOVC指令时,由内部硬件自动使控制线C=1,开关MUX拨向反相器3输出端。这时P0可作地址/数据总线分别使用,并且又分为两种情况。

1、P0口可作输出地址/数据总线。在扩展系统中,一种是以P0口引脚输入低8位地址或数据信息。

2、另一种情况是有P0口输入数据。这种情况是在“读引脚”信号有效时打开输入缓冲器使数据进入内部总线。

综上所述,P0即可作一般I/O端口使用, 也可作地址/数据总线使用。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。