摘要:文中设计并实现了一个窄脉冲小信号运放电路。在文章的开始首先介绍了运放的使用背景以及这次设计的目的,然后介绍了设计思路和具体的电路实现,对该运放进行测试。测试表明该运放能够对上升沿为50ns的窄脉冲小信号进行放大。

运算放大器是具有很高放大倍数的电路单元。在实际电路中,通常结合反馈网络共同组成某种功能模块。由于早期应用于模拟计算机中,用以实现数学运算,故得名"运算放大器".运放是一个从功能的角度命名的电路单元,可以由分立的器件实现,也可以实现在半导体芯片当中。随着半导体技术的发展,大部分的运放是以单芯片的形式存在。运放的种类繁多,广泛应用于电子行业中。

文中介绍的就是一种以三个芯片级联而成的差分运算放大器,该运放能实现窄脉冲小信号放大,脉冲的上升沿可以达到50ns.

根据项目需要,本次设计的差分运算放大器是用于放大检波器输出的信号的,由于接收机接受的信号是小信号脉冲调制,因此设计的运放必要能够放大小信号窄脉冲。因为在小信号情况下,检波器输出为毫伏级别,而指标要求输出在-2~+2V之间,所以设计的差分放大电路放大倍数约100倍。

由于此次设计的运放是为了放大脉冲信号的,所以必须要考虑脉冲信号上升沿的问题,如果上升沿时间太大会导致脉冲信号的失真,因此设计的初就是要限定脉冲信号上升沿时间T<50ns.由于脉冲信号的带宽和上升沿存在如下关系:F&mes;T=3.5(F表示带宽),可知上升沿时间越小,带宽就越大,当上升沿时间T=50ns时。带宽就要达到70MHz.因为运放的带宽和增益成反比,如果只使用运放,在达到要求带宽的同时增益就达不到要求的100,因此本次设计的运放采用两级放大结构,每级放大10倍。

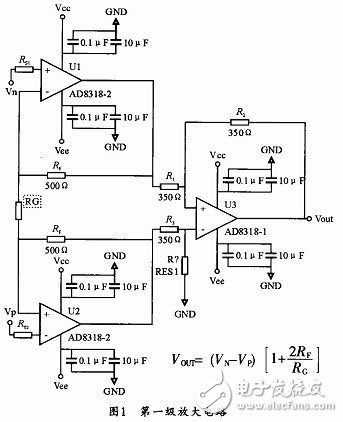

从以上分析可知本次运放电路采用两级结构。级首先对基带信号进行差分放大,芯片选择AD公司的ADA4817-1和ADA4817-2,级放大电路如图1所示。

级放大所用的芯片ADA4817-1(单通道)和ADA4817-2 (双通道)FastFET放大器是单位增益稳定、超高速电压反馈型放大器,具有FET输入。这些放大器采用ADI公司专有的超高速互补双极型(XFCB)工艺,这一工艺可使放大器实现高速和超低的噪声(4nV/√Hz;2.5 fA/√Hz)以及极高的输入阻抗。

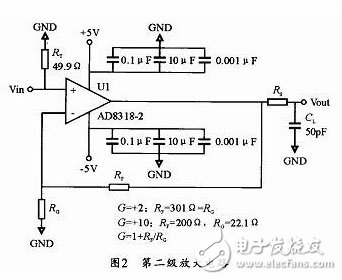

将级输出的信号进行二次放大,第二级放大选择AD公司的AD8009芯片。图2所示是第二级放大电路。

第二级放大所用的芯片AD8009是一款超高速电流反馈型放大器,压摆率达到惊人的5 500 V/μs,上升时间仅为545ps,因而非常适合用作脉冲放大器。

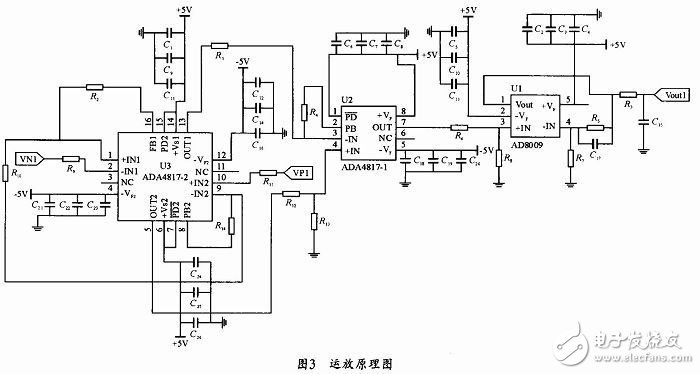

此外为了防止自激,在两级放大的中间连接了一个10Ω电阻。图3是差分运放的整体原理图。

综上所述,说明该运放几乎无失真的将检波器输出的毫伏级窄脉冲小信号放大了接近100倍。这证明本次设计的差分运放是能够满足要求的并且性能良好。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。