自2002年美国联邦通信委员会授权可以无执照使用超宽带(UWB)无线电技术以来,大多数采用该技术的商业应用(如无线USB),都是基于用于高数据速率传输的频域调制技术(如OFDM)。UWB这种成熟的技术还可用于纳秒级的超短脉冲数据传输。这种被称为脉冲无线电(IR)的系统可通过调制诸如位置或者振幅等脉冲参数来传输信息。同时,通过测量脉冲的传输时间,还可以进行到厘米的测距。这为物流(包裹跟踪)、制造、搜救(如与救火队员的通信与定位)或智能导游等不同领域内的大量新型位置感知应用开辟了广阔的新天地。

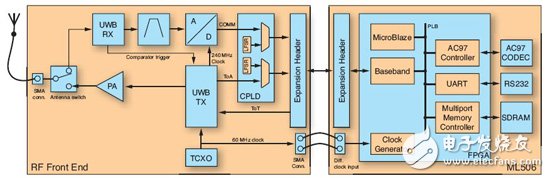

图1:该系统由非定制的赛灵思ML506板与定制的UWB子板连接而成。

欧洲的PULSERS二期是一项由业界主导的UWB无线电技术合作项目,参与的重要行业和学术组织有30家,旨在设计和实施一种可实现每秒百万比特的数据传输速率、测距达4厘米的IR-UWB通信和测距系统。该系统由一整套相同的自主节点组成,每个节点都可以与网络中的其他节点通信并确定与其之间的距离。每个节点由一个定制UWB子板与一个现成的赛灵思ML506开发板上(见图1)连接而成。Virtex-5 SXT架构的卓越性能与MicroBlaze软处理器的灵活性相得益彰,使得我们在单个FPGA内即可部署整个基带信号链及所有系统层。

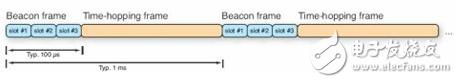

图2:由三个信标槽组成的周期信标帧夹杂在跳时帧之间。

IR-UWB通信和测距

该系统使用支持四种可能的时间位移(4-PPM)的简单脉冲定位调制来传输信息,其中每个脉冲编码两个数据位。如图2所示,脉冲将分组为帧并在预定义的信标帧和跳时帧组成的栅格中传输。每个信标帧包含三个相同的可让客户用来进行测距或者通信的信标槽。我们原本计划将跳时帧用于基于跳时编码的高数据速率传输,不过我们将在此后的产品使用该技术,而现在所有的数据传输只在信标帧中进行。

我们现在用双向测距的方法进行测距。双向测距是通过测量从发送测距请求到从远程节点(见下表)收到回复的时间延迟来实现的。测距请求一般在信标槽1中发送,而测距回复则一般返回到信标槽3中。这给予了远程节点一个完整的信标槽间隔(信标槽2,大约33微秒)来处理收到的测距请求并计划输回的测距答复。

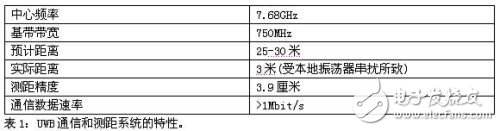

表1:UWB通信和测距系统的特性。

超宽带子板上带有脉冲发射器和非相干接收器ASIC,这是我们专门采用IHP的0.25微米SiGe:C BiCMOS技术为该项目设计的。

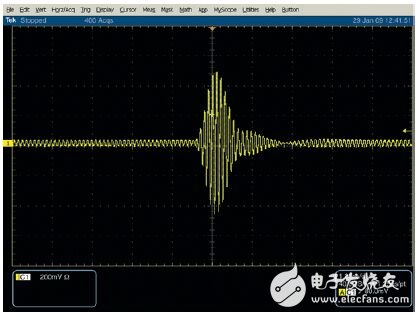

如图3所示,用来产生UWB脉冲的发射器ASIC能够对所产生脉冲的振幅和位置进行调制。其包括的3.84GHz计数器可以地计划输出脉冲的传输时间并测量所接收脉冲的到达时间。

图3:UWB脉冲由7.68GHz的载波和高斯包络构成。

接收路径在接收器ASIC中分为两支。带宽相对较窄(120MHz)的个分支主要用于通信和不太的脉冲计时,而的脉冲计时则通过采用全脉冲带宽(750MHz)的第二个分支来完成。传入的脉冲由该分支上的高速比较器来加以探测。其输出结果可触发运行在发射器ASIC内部的3.84GHz计数器的读出。因此,每个接收到的脉冲到达时间可以260皮秒分辨率进行测量,也即空间分辨率大约为8厘米。

子板与Virtex-5 FPGA内的基带模块通过两条120MHz的数据总线进行通信。通信(COMM)总线负责传输ADC样本,而到达时间总线负责传输与收到的脉冲相关的高分辨率时间戳。两条总线都会通过XC95144XV CPLD,虽然并非必需,但其仍不失为一个出色的调试工具。我们可以设定CPLD在通往FPGA的总线上输出一系列伪随机数字。然后我们利用CPLD输出来调节FPGA的输入时序并验证总线线路的完整性。如果在不了解传输数据序列的前提下验证总线线路将会非常困难。

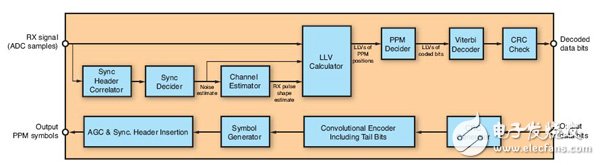

在FPGA内部,基带模块(见图4)同时负责对发出的脉冲进行编码并解码收到的脉冲。而基带模块的传输相对简单,主要包括外部(CRC)和内部(卷积)编码。接收部分的实施还另外涉及一个信道估计器和一个定制的Viterbi解码器,因而要占用更多的资源。基带模块通过处理器局部总线(PLB)接口与处理器系统相连接。

图4:基带模块的接受(顶部)和传输链。

众所周知,可编程逻辑比软件更难调试,不过配置有集成逻辑分析器和总线分析器的ChipScopeTM Pro工具将能在调试期间为我们助上一臂之力。事实证明该逻辑分析器非常有用,因其可同时获取突发COMM和到达时间样本,从而为MATLAB模拟器提供真实环境下的数据。而总线分析器则有助于调试一些与基带模块PLB接口有关的问题。

处理器系统可通过Xilinx Platform Studio(XPS)设计工具中的基础系统构建器(Base System Builder)向导加以生成,这可使我们获得一个完美的起始工作系统。随后,我们逐步修改基本系统,以获得图1所示FPGA部分的系统。这些修改工作此外还涉及转换到差分时钟输入并将基带模块连接至PLB。

该软件应用运行在Xilkernel顶部的嵌入式MicroBlaze处理器中,Xilkernel是一种非常适用于小型应用的实时操作系统。该应用可分为同时运行的三个线程:UWB线程管理基带模块的配置和运行;在系统处于数据传输模式时,应用线程负责获取并播放音频内容;

RS232线程负责与运行演示图形用户界面的外部PC进行通信。

由于XPS使用的GNU开发链在其他一些平台上也可应用,我们可以很方便地在主机PC(如使用Cygwin环境)上,而非在嵌入式目标上编译并测试与硬件无关的代码模块。这样一来,调试工作就变得非常容易了。只有终的测试工作需要在嵌入式目标上完成,而采用如GDB之类的源代码级调试器会受益颇多。赛灵思的应用指南《XAPP1037》为我们提供了许多有用的软件调试技巧。

该系统当初预计的距离范围在25至30米之间,但受一些存在于UWB ASIC中的硬件问题的限制,目前的标称距离仅为3米。不过,我们还是能够同时展示该系统强大的通信和测距功能,而这些功能就是该项目的成功之处。

将来可能还要重新设计UWB ASIC以增加系统的操作距离并实施多点定位功能,将测距系统发展为真正的室内定位系统。

双向测距解说

在脉冲无线电UWB系统中应用的双向测距技术应用中,节点A和节点B之间的距离是通过下列技术确定的(见图):节点A向节点B发送测距请求,并启动高分辨率时钟(3.84GHz);节点B在信号传输延迟prop后收到测距请求,该延迟与节点A和B之间的距离成正比;节点B在已知的处理延迟proc后将测距答复发送回节点A。

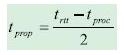

在收到测距答复后,节点A在时间rtt停止时钟。随后,即可根据下面公式:

计算出单程信号传输延迟,再乘以光速后,就得到了A和B之间的距离。

3.84GHz时钟的260皮秒时间分辨率为可实现大约8厘米的空间分辨率。不过,由于无线信号在两个节点之间被传输了两次,因而可以4cm的分辨率确定距离。

在知道自身与三个非共线参考节点的距离之后,移动节点可计算出其2D位置。而使用4个非共面的参考节点,甚至可确定出其3D位置。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。