在汽车电子、航空、航天以及工业监测等领域中,整体测试系统通常所需要同时监控的I/O非常庞大,如此庞大的测试点需要大量的数据采集卡进行同步。由于工业计算机插槽数量有限以及CompactPCI无法同步各个测试模块,所以本系统选用 PXI Express平台通过定时和同步时钟卡利用触发总线、星形触发以及系统参考时钟来实现的多设备同步。本文以带有高精准度恒温晶振的PS PXIe-3102定时和同步模块为例,详细讲述如何进行路由关系配置完成两个PXIe-9108机箱的同步。

1 多机箱原理

多机箱同步与多板卡同步类似,同样需要保证各个机箱间的板卡都在同一个时钟沿开始启动采集,即共享同一个时钟源和同步触发信号,同时为了消除对时钟源分频后的相位差,也要共享同步脉冲信号。因此,在实现多机箱同步时,需要考虑的主要问题就是如何在多机箱间共享这三个信号:时钟源、同步触发、同步脉冲。

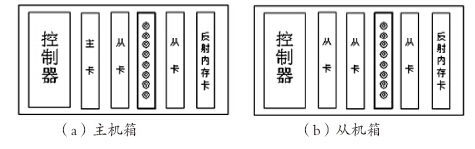

对于两机箱同步,选择其中一个机箱作为主机箱,同时分别在主从机箱的星型触发槽中插入一块时钟卡,该时钟卡可以路由时钟信号和触发信号。在此以泛华PS PXIe-3102定时和同步模块举例说明。

1.1 机箱间共享时钟源

PS PXIe-3102本身自带一个温度补偿晶振,相比背板参考时钟可以提供更高的时钟卡(PS PXIe-3102时钟卡引脚图如图2所示)。因此可以将PS PXIe-3102的10MHz时钟路由到两个机箱中,替代机箱背板的参考时钟,然后各个槽位的板卡都选用背板参考时钟作为采样时基。具体配置过程如下:

图1 PS PXIe-9108两机箱插卡示意图

图2 PS PXIe-9108引脚图

图3 PS PXIe-9108主机箱与从机箱中时钟卡链接示意图

(1)在主从机箱的星型触发槽中各插入一块PS PXIe-3102;

(2)将主机箱PS PXIe-3102的本地晶振(Oscillator)路由到背板10MHz输入端(PXI_CLK10_In)上代替主机箱背板的10MHz参考时钟源,软件配置如图4所示;

图4 替换主机背板参考时钟

(3)将主机箱中的背板参考时钟源(PXI_CLK10)路由到3102的输出端(CLKOut)。背板参考时钟源的路由软件配置如图5所示;

图5 路由背板参考时钟

(4)如图3所示,通过同轴线缆[1]连接主机箱中时钟卡3102的时钟输出端CLKOut和从机箱中时钟卡3102的时钟输入端;

(5)将从机箱中时钟卡3102的时钟输入端(CLKIn)的信号路由至背板参考时钟输入(PXI_CLK10_In)来代替背板参考时钟源。软件配置如图6所示。

图6 替换从机箱背板参考时钟

1.2 机箱间共享同步脉冲

共享同步脉冲的目的是为了消除板卡采样时钟之间的相位差。同步脉冲在每张板卡启动时都会产生,为保证产生的同步脉冲有效,在多机箱同步中也需要考虑同步脉冲在机箱间的路由关系。

将主机箱中的动态信号采集卡作为主卡,将其产生的同步脉冲信号路由到背板的PXITrig线上,实现同机箱中同步脉冲信号的共享。同时,需要将此脉冲信号通过本机箱星型触发槽中PS PXIe-3102的MFIO端口输出路由到从机箱中(MFIO是用于静态数字输入、静态数字输出、AI/AO/DI/DO 或计数器/定时器所需的时钟输入及时钟输出的多功能数字I/O),具体配置过程如下:

(1)选择主机箱中的任意一块卡作为主卡,将其产生的同步脉冲信号路由到背板PXITrig0上(也可选择PXITrig<0..7>中的其它触发线),软件配置如图7所示;

图7 路由同步脉冲信号至主机箱背板触发总线

(2) 将此同步脉冲从PXITrig0上路由至主机箱3102的任一个MFIO端口上,此处以MFIO0为例,软件配置过程如图8所示;

图8 路由同步脉冲信号至主机箱3102MFIO

3)如图3所示,通过同轴线缆[2],连接主机箱3102的MFIO0端和从机箱的MFIO0端;

(4)将同步脉冲由主机箱3102的MFIO0路由至从机箱背板的PXITrig0上(也可选择PXITrig<0..7>中的其它触发线),软件配置过程如图9所示;

图9 路由同步脉冲信号至从机箱背板触发总线

(5)为保证两个机箱间同步脉冲的延迟化,需将主机箱路由出去的同步脉冲再路由回主机箱。首先,将同步脉冲通过主机箱3102的MFIO2路由出来;然后,通过同轴线缆连接MFIO2和MFIO3端口,如图3所示,再将同步脉冲由MFIO3路由至主机箱的背板PXITrig<1..7>的一个触发线上,供主机箱的板卡使用;

(6)根据实际的信号路由路径,配置主机箱和从机箱中每个板卡的同步脉冲源输入,软件配置过程如图10所示。

图10 配置同步脉冲源

1.3 机箱间共享同步触发

完成了采样时钟的同步,就需要机箱间的所有板卡共享同一个触发信号来保证板卡间同步的开始采集。对于同步触发信号,可以有两种。

外部接入的触发信号只能接到主卡上,由主卡来确认有效的触发,然后路由给其它板卡作同步触发。主卡内部产生的软件触发,主卡不需要显式的配置外部触发信号,而是在开始后由主卡软件自动产生触发信号,然后将此信号路由至其它板卡实现同步触发。共享同步触发信号的具体配置过程如下:

(1)选择一块卡作为主卡,为了统一起见,选择发出同步脉冲的主卡同时作为触发的主卡,配置主卡的触发源,如果没有配置,则默认为主卡软件触发;

(2)将主卡的开始触发信号或者参考触发信号(取决于实际的触发模式,开始触发或参考触发)路由至背板PXITrig1上(PXITrig触发线),软件配置如图11所示:

图11 主卡路由触发信号至主机箱背板

(3)通过PS PXIe-3102将主卡的触发信号由机箱背板的PXITrig1上路由至MFIO1上,软件配置如图12所示:

图12 路由触发信号至主机箱3102MFIO1

(4)如图3所示,通过同轴线缆[3],连接主机箱3102的MFIO1端和从机箱3102的MFIO1端;

(5)在从机箱中通过3102将MFIO1端口的触发信号路由至背板的PXITrig1上,以供机箱板卡作为触发使用,软件配置如图13所示;

图13 路由触发信号至从机箱背板触发总线

(6)除主卡以外,所有的板卡都选择背板PXITrig1作为本卡的触发源,软件配置如图14所示。

完成上述路由关系软件配置以及硬件连接后,就可以进行两机箱同步实验了,图15为两机箱同步现场测试平台图片。

2 系统结构

系统由两个高性能的3U 8槽PS PXIe-9108机箱作为测试平台,由高性能2.1GHz四核零槽控制器PS PXIe-3070作为控制器,定时及同步模块选用带有高精准度恒温晶振的PS PXIe-3102,选用动态信号采集卡PS PXIe-3342作为信号采集卡,选用Agilent33522A信号源为采集卡提供同一信号。,为了实时计算两机箱信号的同步选用了两张PS PXI-3550反射内存卡,将其中一个机箱上的采样数据实时映射到另一机箱上进行同步运算。在同步采集过程中,应特别注意先运行从卡的采集程序,等待主卡发送开始触发信号,然后运行主卡采集程序。

3 数据分析

如图16所示,主机箱以及从机箱的采集波形基本重合,计算两张PS PXIe-3342动态信号采集卡的同步为86.0459ns。

4 结束语

介绍了两机箱之间同步的方法后,现简要介绍多机箱同步的实现方式。对于多机箱同步,方法和两机箱同步相同,如果机箱比较多,可以选择一个机箱专门用来放置路由时钟和信号的时钟卡(eg:PS PXIe-3102),同时,其它机箱的星型触发槽中也需要分别插入一块PS PXIe-3102,以完成多机箱间的同步。信号路由的过程和方法如下:

(1)在专门放置时钟卡PS PXIe-3102的机箱中,将星型触发槽中3102的高晶振路由至机箱背板代替机箱的背板参考时钟,然后机箱中的所有3102都可以将背板的参考时钟通过CLKOut端口路由出来给其它机箱使用;

(2)其它机箱中3102通过CLKIn端口将步骤(1)中路由出来的参考时钟与本机箱的背板进行锁相,从而实现多机箱之间共用了同一个参考时钟源;

(3)选择一个机箱中的采集卡作为主卡,将主卡产生的同步脉冲信号路由至本机箱背板的PXITrig的任一未被占用的触发线,然后通过本机箱星型触发槽中的3102将此同步脉冲信号通过MFIO的端口路由至专门放置时钟卡的机箱中;

(4)通过专门放置时钟卡机箱星型触发槽中的3102将主卡发出的同步脉冲信号路由至本机箱背板的PXITrig的任一触发线,然后所有的3102都可以通过此触发线将此同步脉冲信号经过3102的MFIO端口路由至其他所有的机箱中;

(5)为了保证主卡机箱中的同步脉冲与其它多个机箱间将同步脉冲信号的延迟化,可以通过专门放置时钟卡机箱中的任一3102将此同步脉冲再路由回来至主卡机箱,此时保证此同步脉冲到达各个机箱间的导线长度相等就可以保证机箱收到的同步脉冲间延迟化;

(6)将主卡判断出的有效触发脉冲信号通过本机箱的3102路由至专门放置时钟卡的机箱中,方法同路由同步脉冲方法相同。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。