通过磁性图案存储信息的技术早出现在音频记录领域。从那以后,这个概念已被扩展应用于许多不同产品,如软盘、音频/视频磁带、硬盘以及磁条卡。本文将主要讨论在金融交易和门禁控制中得到广泛使用的磁条卡。

读取磁条卡除了需要解码数据的数字逻辑外还要求很重要的模拟电路。在磁卡上记录数据是数字化的过程,通过沿着磁条长度磁化粒子完成。而成功读取磁卡具有相当大的挑战性,因为在实际应用中传感器信号的幅度会随着划卡速度、磁卡质量和读卡磁头的灵敏度而变化。此外,频率也会随着划卡速度变化而变化。这就要求模拟电路能够适应这种变化,无失真地处理传感器信号。本文将介绍如何处理传感器信号变化的机制。

磁性与磁卡

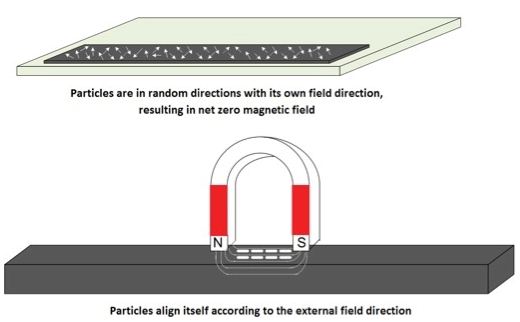

为了理解划卡速度、磁卡质量和传感器灵敏度的影响,了解信息是如何存储在卡上的以及如何被读卡头检测出来很重要。在磁性存储系统中,信息用诸如氧化铁等磁化材料上的极性图案表示。图1显示了涂覆在磁化材料上的磁条。磁化材料上的颗粒可能处于某种特定的排列方向,或者因以前没有受到特定方向磁场的照射而处于随机方向。然而,如果施加一定的外部磁场,磁条上的颗粒将按照外部磁场排列方向。

图1:在外部磁场的影响下磁化材料按特定方向排列

在实用化系统中需要用到一个写入磁头,它其实就是绕在磁心上的一个线圈。通过控制线圈中的电流方向可以很容易编程磁场方向。这有助于在磁卡上形成南北极图案。磁极之间的空隙越窄,磁卡上能够编程的数据密度就越高。

在F2F编码机制中,如果在比特周期内发生磁极转换,那就代表逻辑1,否则代表逻辑0.例如图3所示,如果比特周期是Δ,而磁极转换发生在Δ/2处,那么这个比特就是逻辑1,否则就是逻辑0.注意,逻辑1和逻辑0在磁卡上占据的长度是相同的。不过比特周期Δ会随划卡速度而变化,这个问题在读卡中必须加以解决。

图2:用电磁体磁化磁条表示逻辑1和逻辑0,其中用到了F2F编码机制

图3:磁极图案和数据

值得注意的是,比特周期长度对逻辑1和逻辑0来说都是相同的。

根据信息量的多少,数据将被编码在不同的行,这个行被称为磁道。一个磁卡上多可以有3条磁道。

图4:磁卡上的磁道

读过程正好相反,它需要使用一个结构上与图2所示的线圈-磁芯相同的读卡头。需要注意的是,每个磁道要有一个传感器。在划卡时,源自磁条的磁场将在读卡头线圈中感应出电压。图5显示了从读卡头得到的波形。

图5:读卡头(传感器)信号

信号在每次磁通量转换时出现峰值。这是因为在磁极边缘具有高密度的磁通量。正如你看到的那样,信息是用信号峰值的位置表示的。峰值检测器电路可以解码这个信号,或者使用阈值非常接近信号峰值的磁滞比较器。不过在我们将这个信号交给检测器电路之前,还需要进行额外的处理,原因如下:

划卡速度:划卡速度的单位规定为英寸/每秒(IPS)。一般来说,要求磁卡读卡器能在5 IPS至50 IPS的划卡速度范围内正常工作。传感器信号的幅度随划卡速度变化而变化。划卡速度增加,读卡头中的线圈切割的磁通量变化速度也增加,因此信号幅度会变大。与之相反,当划卡速度变慢时,信号幅度将降低,从而增加数据读取的难度。

磁卡质量:随着时间的推移以及使用量的增加,卡的质量将随着磁场强度的降低以及由于磁卡上的灰尘与刮擦而引起的失真加大而下降。这些因素综合在一起将降低传感器信号的幅度。

读卡头灵敏度:读卡头灵敏度取决于线圈匝数以及读卡头与磁条之间的间距。

由于所有这些参数的影响,信号幅度可能在几百个uV至几十个mV之间变化。这个范围可以用放大器进行补偿。但不能用固定增益放大器。当划卡速度很高,卡的质量又很好时,放大器输出可以饱和到电源轨电压。而当信号饱和时,用两个连续峰值之间的时间差代表的信息将丢失。因此如实地放大传感器信号、不至于使波形发生饱和或改变很重要。这就要求使用增益可配置的放大器,以便我们随时调整增益。要做到这一点,系统必须能够检测信号变弱的时刻。这可以用跟踪传感器信号的ADC寻找近似的信号峰值来实现。

图6显示了一个完整的系统。将放大电路做成两级,用ADC接收级电路的输出。这样就无需高分辨率ADC,8位ADC就足以满足这种应用需求。级可以是固定增益的放大器,也可以是可变增益放大器。第二级是可变增益放大器。CPU读取ADC结果,并通过调整增益使第二级放大器的信号输出达到。第二级放大器的输出送到峰值检测器/磁滞比较器电路进行峰值检测。来自检测器的脉冲输出被馈送至定时器进行时间差测量,然后由CPU解码出1和0。

图6:磁卡读卡器框图

至此仍然存在增益更新之前是否有数据丢失的问题。为了避免这个问题,磁卡的两头会用前导零进行编码以实现同步(这样可以支持双向划卡)。这样做的目的是使解码器同步于划卡速度。举例来说,在磁道1中,共有约62个前导零。磁道1具有210个比特的数据密度。因此我们可以估算出划卡速度为5 IPS时前导零将持续约60ms时间,划卡速度为50 IPS时前导零将持续6ms.对另外两个磁道来说或多或少是相同的,如图7所示。在人为划卡时一开始就是50 IPS的划卡速度是不可能,因此系统具有比6ms长得多的时间来测量峰值并调整增益。图8显示了增益控制过程。

图7:磁卡中三个磁道的内容

需要注意的是,CPU在划卡期间可能会持续精细调整增益以适应变化的幅度。正常情况下,顺着划卡的方向,划卡速度会增加,从而增加信号幅度。注意,在使用以恒定速度划卡的自动划卡机时这个观点是不正确的。

图8:增益改变过程

实现磁卡读卡器

图9显示了基于赛普拉斯PSoC 1的双磁道磁卡读卡器实现方案。PSoC 1处理器具有与8位处理器内核集成在一起的可配置模拟和数字块,在单颗芯片上集成了所有的功能。需要注意的是,图中所示的无源器件是在处理器的外部。

图9:PSoC 1磁卡读卡器

由于传感器信号可能是负的,因此必须用直流进行偏置。在PSoC 1中,模拟信号可以以不同于电源地的地为参考。这个地被称为模拟地(AGND),输入信号被钳位到这个模拟地。信号随后用可编程增益放大器(PGA)进行两级放大。PGA是用连续时间模拟模块实现的。它具有一个电阻阵列,当配置为放大器时用于改变增益。增益可以被配置为1至48之间18个选项之一。CY8C28243 PSoC 1集成了一个采样速率为150ksps的10位SAR ADC。

CPU读取ADC,然后控制放大器增益。放大后的信号送到磁滞比较器产生边沿接近信号峰值的数字信号。CPU随后必须调整放大器增益,使其阈值接近峰值但不超过峰值。这有助于避免磁卡发生抖动时出现定时误差。磁滞比较器输出则送到定时器进行脉冲宽度测量。CPU读取定时器输出,并解码为逻辑1或0的数据。当划卡结束时,CPU打包数据比特,检查是否有错误,然后通过I2C、SPI或UART接口将数据送给主机。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。