导读:本文旨在研究基于FPGA技术对嵌入式SoC系统进行在线监控的方法。设计了一个FPGA片上通信系统,该系统内部固化基于UART接口的Modbus通讯协议栈,可通过串口与PC上位机进行通信;且采用双口RAM作为与监控对象间共享的数据缓存区,通过中断机制实现数据的同步交换,既确保了监控数据的实时性,也避免了嵌入式系统因处理监控通信过程而带来性能损失。采用VHDL语言设计实现了通信系统的各组成部分,在Altera的cycloneII系列芯片开发板上验证了方案的可行性。

在SoC系统的设计及使用过程中,对其内部行为的实时监控十分重要,目前普遍通过监控端和目标系统间的监控信息通信来实现,UART常用作通信信道。

目标SoC系统常使用中断方式或轮询方式获取监控通信数据包,对其解析并进行相应数据操作后回复应答信息。中断方式中SoC需完成保存中断现场、调用中断服务程序、恢复现场系列任务,上下文的切换占据了系统额外开销;轮询方式中,系统定时检查设备请求,若有数据到达则调用相应处理程序,固定的轮询周期增加了数据等待处理时间,数据量较小时频繁查询造成对CPU资源的浪费。

针对上述问题,提出一种的新监控方法,设计一个FPGA通信系统,由其作为SoC与监控计算机数据交互的桥梁,负责完成在线监控的通信过程,保证被调试系统和调试主机之间调试信息和命令的交互可靠性,可避免目标SoC频繁的处理通信中断,提高其控制性能。监控功能实现机制与通信系统主要模块的设计方法将被讨论,通过对比嵌入式CPU在不同监控方法中的通信时间消耗,说明该方法具有一定实用价值。

1 系统组成结构

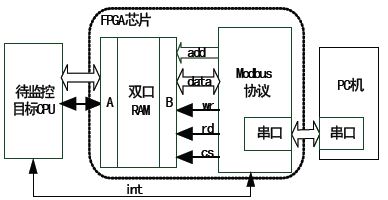

基于FPGA设计片上通信系统如图1所示,其主要组成部分为Modbus解析模块和双口RAM存储模块。上位机发出监控命令帧数据时,由Modbus模块完成命令帧的接收、解析过程,并将待操作地址、数据等信息存入双口RAM中,目标CPU据此将自身内存映像区的相应数据搬入双口RAM,搬移完毕后,Modbus协议模块进行应答数据组帧,并向监控上位机发回应答数据,实现对监控数据的实时可靠采集。

图 1 通信系统组成结构

2 基于双口RAM的数据交互设计

2.1 双口RAM定制及内存映射设计

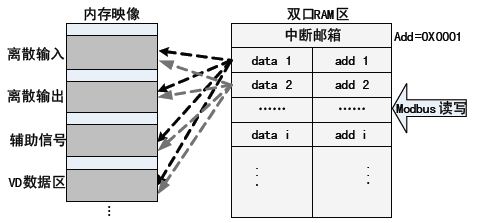

目标SoC中的待监控数据状态量在内存中的存储方式,可抽象表示为如图2中内存映像。

图 2 双口 RAM 的内存映射机制

双口RAM中存储当前待监控数据对象集合,是目标CPU内存映像区的一个数据子集。由于当前监控对象可随机落在内存映像区的任意存储块上,双口RAM的内存映射方式选取为随机映射,如图2所示。

分散存放于CPU内存映像区的监控对象,映射为双口RAM中的连续存储区。上位机基于Modbus协议与FPGA片上系统通信时,访问连续的地址单元,保证了数据访问速度,提高系统的通信效率。

2.2 双口RAM中的数据操作设计

2.2.1 上位机对双口RAM的读写操作

PC上位机为通信发起方,通过串口与FPGA片上系统连接,采用Modbus-RTU协议进行数据通信,完成对运行参数的读取和写入等操作,实现监控功能。

表 1 监控通信过程占用 CPU 时间

用户在人机界面输入本次待监控对象信息, 后台软件依据Modbus帧结构及约定的双口RAM内存映射机制,组成监控命令帧并通过串口发出。FPGA片上系统对收到的命令帧进行解析,获取操作功能码、目标地址、数据包大小等信息,据此向双口RAM区写入待操作数据地址集,写入完毕后向目标CPU申请通信中断。根据Modbus命令帧中给出的数据操作长度,可对多个数据单元进行读/写操作。

2.2.2 目标CPU对双口RAM的读写操作

目标CPU收到通信中断请求后,读双口RAM区的中断邮箱,邮箱信息包含本次申请功能(读或写)及申请的数据项个数等。根据申请地址集,将自身内存映像区相应数据集搬入双口RAM,或将双口RAM中数据集搬入内存映像区相应地址处,搬移完毕后,清空中断邮箱,向监控模块发出中断应答。

3 Modbus协议栈模块的设计与实现

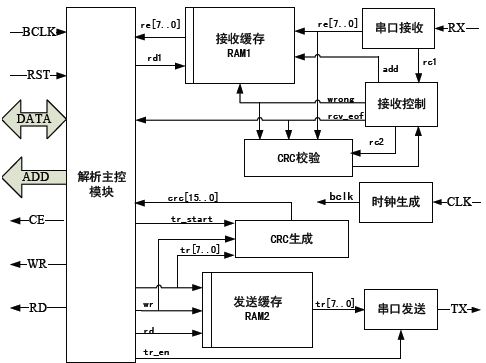

采用自顶向下的设计方法,根据功能需求设计Modbus协议栈顶层原理框图如图3。使用VHDL硬件描述语言编程实现各组成子模块,功能如下述。

图 3 Modbus 协议栈顶层框图

(1)时钟生成模块:通过分频和相移产生位时钟clk和1/16位时钟bclk,作为控制其他模块的运行节拍,保证系统运行同步。

(2)串口接收模块:以bclk作为控制时钟,对接收的位数据作中点采样,进行串并装换得到字节数据。

(3)串口发送模块:以bclk作为控制时钟,发送使能信号有效时,输入端的字节数据进行并串装换,通过串口发出。

(4)接收控制模块:判断帧的起始、结束、是否接收错误;提供地址数据,接收的字节数据被存储至RAM1中相应存储单元。

(5)CRC校验/生成模块:使用基于字节的CRC_16校验码运算方法。接收端的校验过程与数据接收同步进行,接收控制模块每收到一个字节数据,CRC校验模块对其作CRC码计算;CRC生成模块运行机制类同。同步运算可有效减少对帧数据的遍历。

(6)解析主控模块:作为系统的,负责解析收到的命令帧,根据解析信息进行数据读写操作,组成应答帧,控制串口发送模块发送应答数据等多项任务。收到一个校验无误的命令帧后,控制读取接收缓存区RAM1中数据,比照Modbus帧格式解析命令帧含义,通过对外数据、地址等接口完成对双口RAM的读写操作;解析及操作完毕后,控制应答帧组帧过程,将应答数据依次写入RAM2发送缓存区,全部写入后,将CRC生成模块中CRC_16校验值按低位在前高位在后顺序,依次存放到发送缓存的下两个地址位置处,此时应答帧准备完毕;控制发出应答帧,依次读取出发送缓存区数据(读脉冲间的时间间隔至少大于串口发送单个字节所需时间),每取出一个数据,提供发送使能脉冲供串口发送模块工作,脉宽等于串口发送单个字节所需时间,直至应答帧全部发送完毕。

(7)接收缓存RAM1/发送缓存RAM2:存储串口接收模块收到的字节数据/存储待发送的应答帧。

4 性能分析

分析监控通信对Soc系统性能的影响,设定一系列参数如下:时间基数T(min)、监控频率m(帧/min)、监控命令帧平均长度n(byte/帧)、Soc主循环平均周期k(ms)、通信波特率B(bit/s)、中断处理指令数r(条)、查询语句指令数s(条)、处理器主频f(HZ)。针对常用的轮询监控、中断监控,及该文所提出的基于FPGA的DRAM监控方法,可按照表1公式计算其监控通信过程占用的CPU时间。

对于常用ARM处理器,可例举部分参数值f=72M,r=15,s=5。设定其余参数值T=1,m=100,n=30,k=0.05,B=115200。在当前设定下,计算得出三种监控方法对CPU的时间占用百分比,如表1所示。对比应用单一的中断或轮询方式,使用该文提出的监控方法时,嵌入式系统CPU的利用率得到了明显的提高。

5 结语

该文提出一种针对嵌入式片上系统的在线监控方法。利用FPGA技术设计了辅助监控系统,由该系统完成监控通信过程中的接收通信命令帧、解析命令帧及组成应答数据帧等任务,加快了对通信数据的处理速度。SoC有效减少了处理监控所需时间,更集中于其控制功能的执行,从而获得更高的实时性。设计工作在Altera公司的QuartusII开发平台上采用VHDL语言完成,使用CycoloneII系列芯片作功能验证,通信系统的Modbus接口与上位机在115200的波特率下收发正确,双口RAM内数据交互稳定,达到了预计效果。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。