1 引言

低温共烧陶瓷(LTCC)是用于实现高集成度、高性能电子封装的三维多层封装技术。在微波、毫米波系统中,可广泛应用于多芯片模块(MCM)电路设计中。在三维MCM系统集成技术中,LTCC技术集高密度多层互连、内埋无源元件和气密性封装于一体,使多种电路封装在同一多层结构中,可集成数字、模拟、RF/微波电路,这些优点使其成为实现系统级封装(SIP)的技术。

在瞬时测频、测量仪器及高速数字电路等领域中,宽带微波延迟线是关键部件,其性能指标主要取决于延迟线的长度和相位。传统的延迟线一般用同轴电缆实现,不仅体积庞大,而且制作过程引入许多人为因素,一致性较差,对后级电路处理带来不良影响。也有采用平面弯折的带线结构来实现延迟线,但这种二维结构的相邻线段间距离必须保持足够大,以减小线间耦合,这无疑增加了延迟线的尺寸;而采用LTCC多层基板制作的延迟线通过三维互连技术,将弯折线分别置于不同层,不但体积大大缩小,而且一致性获得了提高。

2 LTCC多层结构中带线之间的转换设计

在LTCC多层基板中,位于表层的微带线与埋置于中间层的带状线之间,以及中间层间的带状线之间的转换可以通过一种“类同轴垂直转换结构”来实现。其概念来自于同轴传输线结构,它是由一组连接不同金属化地层的通孔作为外圈屏蔽层组成,被这些屏蔽通孔围绕的中心通孔类似于同轴线的中心导体以连接不同层间的信号线,如图1所示。

(a)俯视图

(b)微带线与带状线的类同轴垂直转换

图1 LTCC多层基板中的类同轴垂直转换结构

根据同轴传输线理论,图1所示的多层类同轴垂直转换可以采用同轴线的特性阻抗公式(1),通过调整外层屏蔽通孔圈的直径D0,来获得50W标准阻抗。

(1)

(1)

由(2)式可以计算出50W传输线的外径D0。

(2)

(2)

对于er=5.9的LTCC基板,由式(2)算得D0=1.5mm,而中心通孔直径Di=0.1mm,外圈屏蔽通孔直径为0.1mm。经仿真在保证获得良好信号传输性能的条件下,外圈屏蔽通孔的数量约为6。在有足够屏蔽通孔数(如8~10个)的情况下,过多地增加通孔个数对S参数传输性能没有太大地改善。正如图1(b)所示的结构所示,信号通孔在穿越微带线地层(带状线上层地)时,在地层上开孔,使地包围垂直通孔,起到较好的屏蔽作用,其传输结构不是50W标准阻抗,所以这种三维通孔结构是重要的设计考虑。通过在频域进行三维全波电磁仿真优化,可得到地层开孔直径dT=0.54mm。

此外,带状线与垂直通孔连接处的焊盘尺寸对传输性能也有一定影响,为了有助于将电磁信号较好地通过垂直通孔传输到下层的带状线上,经优化其焊盘直径为0.21mm。图2给出了图1(b)所示结构(微带-带状线-微带)的仿真和测量S参数,结果显示:随着频率增加,插损逐渐增大;测量结果较仿真值插损大,值在-1dB。这主要是由于LTCC基板介质的实际损耗会随频率增加而增大引起的。此外,实测插损值中还包括了测试架及输入输出SMA接头的插损。

图2 LTCC基板类同轴垂直转换的测试和仿真结果

3 LTCC多层延迟线设计

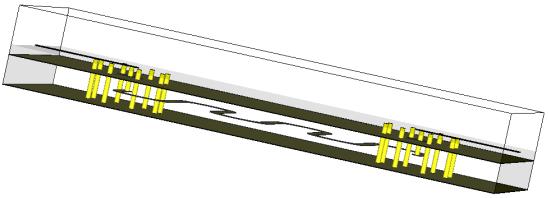

利用LTCC基片设计了0.2nS和0.55nS两种延迟线,层数分别为8层和20层,每层厚度:0.1mm。0.2nS多层延迟线的结构与S参数测试、仿真结果如图3所示,LTCC基板厚0.8mm。其中,微带线基片为两层,厚度0.2mm;带状线基片为六层,导带居中,上、下基片对称各为三层,厚度0.6mm。微带线、带状线及类同轴垂直转换结构均按50W特性阻抗来设计。类同轴转换的接地通孔贯穿整个LTCC基板,连接上下两层地面,为信号线提供良好的屏蔽。微带线作为输入/输出馈线,带状线采用弯折线结构来获得所需的延迟效果。根据式(3),可以计算出所需弯折线的长度l:

(3)

(3)

其中,t为延迟时间,c为光速。再利用三维全波电磁仿真优化该多层延迟线,获得4~8GHz频率内,延迟时间为0.2nS时,所需的弯折带线长度。

(a)0.2nS LTCC多层延迟线

(b)0.2nS LTCC多层延迟线测试和仿真结果

图3 0.2nSLTCC多层延迟线

由于弯折线段间的串扰影响,弯折带状线间的水平间距一般为在4Ws左右,Ws为带状线的线宽;从而在尽可能小的线间距下,减小互扰。为了获得良好的屏蔽及传输效果,除了顶层及其表面以外,LTCC基板侧面及底层均覆金属地(镀银),且所有金属地均与各层地相连接。

0.55nS延迟线的LTCC基板总厚度:2mm.其中,微带线基片为两层,厚度0.2mm。带状线分三层垂直放置,而每个带状线的基片有六层,导带居中,上、下基片对称各为三层,厚度0.6mm.类同轴垂直转换通孔为不同层之间的带状线提供连接。不同层的延迟线仍采用弯折带状线,其设计如同0.2nS延迟线,图4所示为结构与测试、仿真结果。正如图4(a)所示,自基片顶层向下,信号从顶层输入微带线经转换过孔传输至层带状线;再以同样方式传至第二、第三层带状线;,由第三层带状线经转换过孔直接传至顶层微带线输出。输入输出微带线周围的地过孔自上而下,贯穿整个基板;层带状线至第二层带状线转换周围的地过孔由微带线地层穿至第三层带状线的上地层,共六层基片,此接地过孔长度0.6mm。文献[7]报道的两层带状延迟线的输入输出端口在同一侧,且相距较近;而本文所提出的三层带状延迟线输入输出端口分别位于基板的两侧,有利于与系统其它部件电路相连接;且弯折线为半圆弧线平滑过渡拐弯,其传输线线宽不变,以保持传输线阻抗连续性弯折线直角拐弯不连续性,可以减小反射,获得较好的微波信号传输性能。

利用我所8 英寸LTCC 产品生产线加工制作的0.2nS、0.55nS延迟线,其实物照片如图5所示,尺寸分别为:10×5×0.8mm、5.6×7.1×2mm。

(a)0.55nS LTCC多层延迟线

(b)0.55nS LTCC多层延迟线测试和仿真结果

图4 0.55nS LTCC多层延迟线

(a) 0.2nS延迟线 (b) 0.55nS延迟线

图5 LTCC多层延迟线实物图

4 结论

本文提出的基于多层LTCC基片的三维弯折延迟线在4~8GHz频段内,提供了所需的延迟时间,并获得了较好的传输特性。类同轴垂直转换结构除了提供不同层间传输线的连接以外,还可以极大地改善多层电路传输性能。对于给定的延迟时间,多层LTCC延迟线以其结构紧凑、体积小和良好的信号完整性,可以与其它多层功能电路一起集成在同一封装内,构成SIP系统。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。