网络/无线/云计算、数字消费、自动测试设备(ATE)/工业等应用市场的不断发展令时钟技术在性能和灵活性的结合越趋重要,而且越来越多的应用要求实时时钟在宽温度范围内有极高的计时。安森美半导体(ON Semiconductor)为满足市场对更高时钟的需求,不断开发和拓展完整时钟解决方案,降低时间抖动和相位噪声,同时使系统设计更加简单易行。

不同应用市场对时钟方案的需求

不同应用市场对时钟方案的需求各有特点。例如,网络、无线和云计算领域需要低于1ps的抖动及低相位噪声,采用晶体振荡器(XO)或压控晶体振荡器(VCXO),并且在网络/无线基站时钟中集成更高的灵活性及更多的功能。数字消费领域则需要具有专用时钟合成、压控晶体振荡器、可编程能力(系统设计灵活性)、多PLL可配置频率、扩频有源降低电磁干扰(EMI),以及快速提供样品和上市,还需要降低成本。ATE和工业领域需要高速精密时钟及数据管理器件。

PCIe接口的应用优势及行业普及趋势

作为一种重要的总线接口技术,外围组件快速互连(PCIe)具有很多优势,如在带宽、模块化及多内核器件方面提供更高性能,采用标准独特连接时可以优化成本及可靠性等。在PCIe应用渐趋普及的今天,越来越多的存储设备已经开始从SATA接口转向PCIe,固态硬盘(SSD)存储器也开始转向PCIe;NEC家庭网关(HGW)自2010年开始使用PCIe;某些机顶盒芯片组(消费类)参考设计在2010年加入PCIe接口;不同架构的数据中心在大幅增加高速PCIe的使用方面发挥了关键作用。我们看到,PCIe在PC/图形/工作站、服务器和存储、数据通信、嵌入式/企业、消费、SSD存储等行业日渐普及。

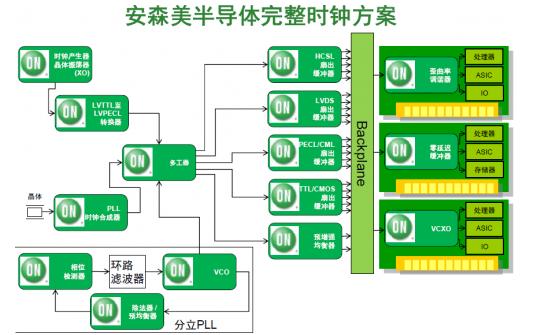

图1:安森美半导体完整时钟方案

正是为了配合时钟市场及时钟生成技术的应用趋势,安森美半导体凭借先进的半导体工艺和模拟技术专长,提供完整的时钟方案(图1)。这些产品可以在系统中提供犹如心脏有规律跳动的准确频率,在实现更高性能的同时简化系统复杂度,实现的系统同步。

安森美半导体用于服务器系统的PCIe时序产品和方案

以服务器技术的变迁为例,首先可以看到其三个变化方向:关键任务/数据分析(大数据)、企业和超大规模。其次,企业服务器市场将继续繁荣发展,用于低交易量、高计算工作负荷的服务器市场不断扩大,并逐步采用内部部署(On-premise) 、云计算、虚拟化、数据库等。第三,网络级数据中心演进带来了新商机,高交易量、低计算工作负荷不断增加;Web 2.0数据中心、视频传送、用户鉴别持续得到采用。安森美半导体用于服务器系统的时序产品如图2所示。

图2:安森美半导体用于服务器系统的时序产品

安森美半导体PCIe时钟方案具有一些共同特性和优势,包括带单路、双路及四路输出的PCIe时钟合成器;带1:6、1:8、1:10及1:21扇出的PCIe缓冲器;提供用于1、2、6、8、10及21通道应用的方案;具有超低歪曲率(skew);传播延迟变化小(多达21路输出);抖动符合PCIe第1代、第2代及第3代规范;直接器件接口省去外部端子元件,减少物料单(BOM)。

1)NB3N3002

NB3N3002是一款3.3 V晶体至单高速电流驱动逻辑(HCSL)合成器,特性包括:频率25 MHz、100 MHz、125 MHz和200 MHz;HCSL差分输出;支持PCI-Express和以太网需求;使用25MHz基本并联谐振晶体;3.3 V电源;无需外部环路滤波器;引脚兼容无扩频ICS557-01、5V41064、5V41234.此外还有NB3N5573 3.3 V晶体至双高速电流驱动逻辑 (HCSL)合成器。图3是NB3N3002的简化框图。

图3:NB3N3002以100 MHz驱动NB3N106K/108K/111K扇出缓冲器

符合PCIe 1,2,3抖动及相位噪声规范。

2)NB3N51034、NB3N51044和NB3N51054

这些都是新推出的产品,特性包括:采用25 MHz基本模式并联谐振晶体;掉电模式;不需要外部环路滤波器;四个低歪曲率HCSL输出;OE三态输出;扩频选择为-0.5%、-1.0%、-1.5%和无扩频;PCI Express Gen 1、2、3抖动要求;引脚兼容IDT557-05、5V41236、5V40166。

在100MHz条件下,NB3N51034与竞争对手(PCIe Gen3) 相比,其均方根(RMS)抖动仅为0.41ps (12 kHz~20 MHz),而竞争对手为65 ps (12 kHz~20 MHz),见图4。

图4:安森美半导体NB3N51034均方根抖动性能明显优于竞争器件

另一款是NB3N51044 3.3 V四输出HCSL/LVDS合成器,带单独输出启用 (OE),增加了LVCMOS/LVTTL输入,支持四个100 MHz (PCIe)或125 MHz (sRIO) HCSL输出;FSEL引脚可在100 MHz/125 MHz之间切换;PLL旁路模式;每个输出三态输出单独OE;引脚兼容IDT841604A.

还有一款新产品是NB3N51054 3.3 V、1:4 HCSL/LVDS合成器。其特性在于具有减少EMI的扩频;启用/禁用每个输出和选择/关扩频ON/OFF的I2C接口;引脚兼容ICS841S104I。

3)NB3N3002/5573

它具有以100 MHz频率驱动NB3N106K/108K/111K的输出性能。在扇出缓冲器输出进行测量的结果显示,含25 MHz晶体的NB3N3002/5573(时钟生成器)以100 MHz模式驱动NB3N106K/108K/111K扇出缓冲器符合PCIe 1、2、3抖动及相位噪声规范;为NB3N3002/557增加扇出缓冲器不会产生足够的抖动或相位噪声以产生无法符合PCIe 1、2、3相位噪声及抖动规范的“系统”。

4)用于PCIe应用的时钟分配器件ZDB及扇出缓冲器

服务器平台有3种时钟拓扑结构:内部系统时钟、混合系统时钟和外部系统时钟。针对PCIe外部时钟架构,安森美半导体提供多种专用时钟选择,包括时钟产生器(NB3N3002/NB3N5573/NB3N51034/NB3N51054/NB3N51054/NB3N51044) 、零延迟缓冲器(ZDB) NB3N1200K/NB3W1200L (可用于PCIe混合时钟架构),以及HCSL至HCSL扇出缓冲器(不需要调节时钟沿使其与ZDB输出同步的多PCIe参考时钟产生器)。

例如,NB3N1200K/NB3W1200L零延迟缓冲器(ZDB)带12路HCSL/NMOS推挽输出,特性包括:支持DIF SRC时钟;12个差分时钟输出对@0.7V (NB3N1200K);12个低功耗NMOS推挽输出对(NB3W1200L);针对100MHz和133 MHz优化,符合PCIe 第2代/第3代和英特尔QPI相位抖动规范;符合低EMI扩频;输入至输出延迟变化的伪外部固定反馈;每12个输出的单独OE控制引脚。两者的相位噪声均优于竞争对手,见图5。

图5:NB3N1200K与竞争器件的相位噪声性能比较

使用NB3N1200K或NB3W1200L时需注意,NB3W1200L是低能耗版本,用于要求低能耗的系统,用于长度小于20英寸的较短长度输出传输线路;NB3N1200K使用标准HCSL输出设计,在输出使用恒流源,可维持长于20英寸输出传输线路的信号完整性。

另外,多个PLL分层布置时,用户可调节带宽对时钟树进行系统优化。使用HBW(高带宽)扩频时钟时用于维持扩频特性,从而将输入与输出相位差减至;使用LBW (低带宽)可滤除PLL带宽内的时钟输入抖动。

以下情况应该使用ZDB或扇出缓冲器:使用零延迟缓冲器 (ZDB) (PLL模式) 时;维护同步时钟沿对齐时;当时钟生成至输出传播延迟至关重要时;用作扇出缓冲器时;当时钟生成至扇出输出传播延迟不重要时。

5)新产品

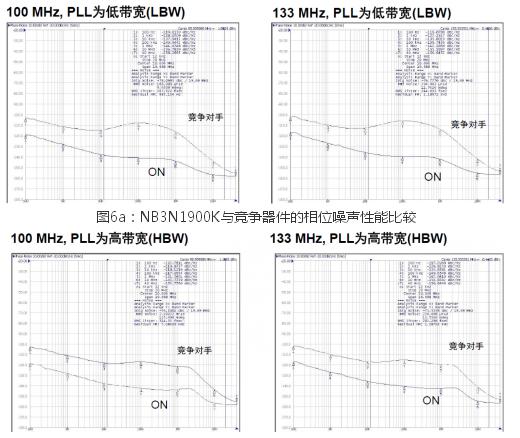

安森美半导体还在开发一系列新产品来满足英特尔白皮书规范,如带19路HCSL/NMOS报推挽输出的NB3N1900K/NB3W1900L ZDB,带8路低能耗NMOS推挽输出的NB3W800L ZDB,带HCSL输出的NB3N208K 1:8扇出缓冲器,以及带HCSL输出的扇出缓冲器NB3N106K、NB3N108K、NB3N111K和NB3N121K等。以上介绍的器件工作范围为3.3 V ± 5-10 %,工业级温度范围均为-40°C至85°C,目标市场及应用涵盖服务器(PCIe、QPI和FB-DIMM),以及网络(PCIe) 等。这些器件提供优异性能。以NB3N1900K为例,其相位噪声性能优于竞争器件,见图6。

图6b:NB3N1900K与竞争器件的相位噪声性能比较(续)

总结:

作为服务器应用及其它多种应用的时序方案供应商,安森美半导体提供包括时钟产生、零延迟缓冲器(ZDB)及扇出缓冲器等在内的完整方案。公司的产品涵盖计算机应用的宽广产品阵容,具有一流的相位噪声和抖动性能以及极高的性价比优势,符合及超越第1代、第2代及第3代PCIe要求,可以直接升级众多现有工业标准方案。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。