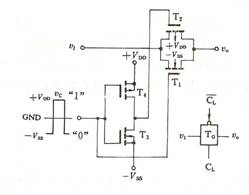

图1为CMOS模拟开关电路原理图。它克服了NMOS模拟开关电路Ron虽vI增大而增大的缺点,扩大输入信号幅度的范围;而且可以在CMOS电路基础上增设辅助电路,消除NMOSFET的衬底效应对Ron的影响。

图1 CMOS开关电路原理

假定控制信号vc高电平VCH=VDD为逻辑“1”,低电平VCL=-Vss(取Vss=VDD)为逻辑“0”.T1衬底电压VB1=-Vss,T2衬底电压VB2=VDD.从图可知,vc直接输送到T1的栅极,而T2的栅极电压是vc经非门(T3、T4组成)倒相后的电压。当vc=“1”时,VG1=VDD,VG2=-Vss.所以当vI为接近-Vss低电平时,vGS1=(vG2-vI)=(VDD-vI)>VT,T1完全导通,vGS2=(vG2-vI)=(Vss-vI),即vGS2<VT,T2截止,iD2=0;反之,当vI为接近VDD高电平时,则T2完全导通,T1截止。而当vc=“0”时,T1、T2均截止。由于开关闭合时,T1和T2并联,互相补偿,使vI在-Vss~VDD范围内变化,Ron基本不变。CMOS开关Ron与vI的关系如图2所示。

为了消除NMOSFET的衬底调制效应对Ron的不良影响,通常在CMOS开关原理电路基础上增设辅助电路。如图3所示CMOS开关电路 中,增加了非门PI2和T3~T5.当vc=“1”时,因非门PI1、PI2倒相,T5截止,vI经T3、T4加到T1衬底B1上,同时,vI又直接加到T1的源极S1上,于是vBS1=0,且与vI大小无关,从而消除了T1的衬底调制效应。T2为PMOSFET,虽然vB2=VDD,但因PMOSFET的衬底调制效应很小,故vBS2随vI变化对Ron的影响可略。

图1 CMOS开关Ron与vI的关系 图2 含辅助电路CMOS开关电路

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。