摘要:本文介绍了一种基于Flash的高速数据采集记录装置的实现方案;文中采用了Flash高速存储技术与FPGA的二级缓冲技术,提高了存储速度,突破存储芯片的瓶颈,成功实现了数据存储速率与传输速率完美的匹配;同时通过设计合理的电路降低了存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储。

1.系统方案设计

本文设计的数据记录系统由以下几部分组成:两台完全相同的数据记录仪、一个地面综合测试台、上位机、配套软件以及配套电缆。主要用于记录由雷达系统产生的视频回波、图像及遥测三路LVDS高速信号。系统工作时,由雷达系统首先发来启动记录信号,使已处于采集状态的两台记录仪同时工作,二者互为备份。地面测试台产生的模拟信号供记录仪存储,同时可以控制记录仪进入不同的工作状态,通过内置的USB接口读取记录仪的数据;上位机通过USB电缆与地面测试台相接,对回读的数据进行分析,同时验证记录仪是否正常工作。

2.系统硬件设计

该系统采用隔离变压器隔离接收三路LVDS数据,使得隔离前后的电路没有电气连接特性,然后再将隔离后的信号传送给存储模块;经过存储模块的均衡、解串后传给FPGA中心控制器,存入两片Flash中。

遥测系统输出的三路数据都有各自的启动记录信号。当记录仪接收到启动控制信号,开始记录对应路的数据,并存储到相应的存储模块中。飞行试验完毕后,可以利用备用读数电缆,将各个存储模块中数据通过测试台上传至上位机中进行分析,以便对记录仪的存储功能进行验证。在飞行模式下记录仪的供电由雷达系统完成。

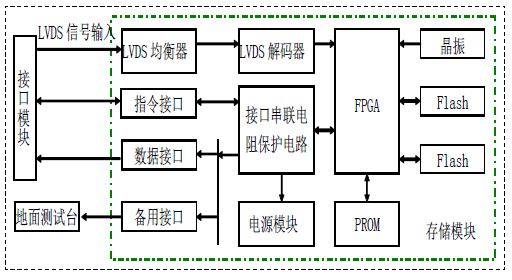

记录仪由三个存储模块和一个接口模块组成。存储模块主要接收遥测系统的视频回波、图像及遥测三路LVDS信号,并对其中的有效数据进行实时存储。该模块主要包括以下几个部分:中心逻辑控制芯片FPGA、配置芯片PROM、LVDS电缆均衡器、LVDS解串芯片、存储芯片Flash、电源模块以及60MHz晶振等。如图所示:

接口模块主要包括LVDS高速读数接口、RS-422长线接口、视频及图像遥测雷达信号输入接口、各个存储模块的LVDS输入接口以及数据上传和指令下发接口。高速读数接口与地面测试台主控卡的相应接口连接,通过LVDS接口高速读取其中的数据;422长线接口通过双绞线电缆与地面测试台连接,主要实现记录仪与地面测试台之间的通信。

3.系统逻辑设计

3.1 Flash高速存储技术设计

由于Flash是基于页读写、块擦除的工作模式,在对其进行读、写以及擦除操作都需要一定的等待时间,通过建立无效块列表,有效地提高了读写速率。由FPGA内部时序控制转换将生成的4K并行数据轮流写入两片Flash中,单片Flash采用交替双平面页编程方式,存储速率能够达到29.85MB/s.采用两片Flash进行存储,从时间上看两个数据流同时流入两片Flash中,相当于数据总线增加了一倍,实现数据存储速率能够达到单片Flash存储速率的两倍,即有效数据存储率为59.7MB/s,大于有效数据的传输速率59MB/s,能够保证对每路数据源的可靠存储。

3.2 存储模块逻辑设计

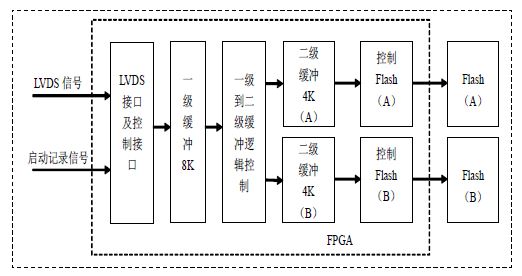

LVDS数据流可以直接按字节方式分离并存储,该方式虽然可以降低FPGA内部资源的消耗,但是加大了对存储数据恢复的复杂程度,并其中一路存储时出现丢数,容易影响到另一路数据的存储,造成数据结构的紊乱,导致存储数据无法恢复。因此采用FPGA内部双口RAM资源,实现8Kbyte数据的缓冲,之后增加两个4K双口RAM,构成了二级缓冲。

对于单路的I/P/Q信号,数据在60M的时钟下写入缓冲(8K)中,当判断写入数据大于7106后,以60M的速率连续读取4096个数据给二级缓冲A,同时控制Flash(A)模块对二级缓冲A中的数据进行判断,当写入数据大于10个后,以30M的速率连续读取4096个并写入Flash(A)中;当再次判断缓冲(8K)中读写地址差值大于7106后,同样以60M的速率连续读取4096个数据,并写入二级缓冲B,当控制Flash(B)模块判断二级缓冲B中数据大于10个后,同样以30M的速率读取4096个后写满Flash(B)中的一页。上述操作交替进行,实现LVDS数据流中的有效数据轮流有序地存入两片Flash中。存储模块内部实现两级缓冲的逻辑原理框图见图:

4.系统可靠性设计

记录仪的正常工作离不开其可靠性设计。若电路设计的不合理,记录仪的工作性能得不到保障,严重时会损坏设备,可见电路的可靠性设计[4]是记录仪正常运行的首要保障。

4.1 降低存储模块功耗的可靠性设计

存储模块的供电经过电源芯片进行电压转换,给存储模块内部芯片供电。在未灌封之前进行多次常温测试发现,工作时电源芯片和XC3S200表面温度较高,而且由于对记录仪小体积的要求,要求内部芯片焊接很集中;而且记录仪在高空试验环境中会受到高冲击、高过载的影响,必须对记录仪存储模块进行灌封,增加抗冲击能力。为了解决上述问题,降低消耗在存储模块电源芯片本身的功耗。下面对存储模块进行温度测试试验。为了获得存储单元灌封后的内部温度,我们使用热电偶对内部多点进行测量,实时显示温度。在试验一和试验二中,我们选定以下七个点,试验三中增加了中壳体外壁一点。

通过以上设计的试验可以看出,当存储模块的供电电源输入为3.6V左右时,测试各点的温度都所有下降,在芯片正常工作范围内,且存储模块在长达十几小时的高温环境中仍能正常工作,说明存储模块输入电源采用3.6V供电的可靠性。

4.2 记录仪通信的可靠性设计

在整个存储设备中,RS-422传输协议主要实现记录仪与测试台之间的通信功能,控制记录仪的工作状态,另外,还可以完成记录仪的长线读数功能。数据是以串行差分形式传输,测试台主控卡向记录仪下发传输命令的长度都是以6个字节为基本单位,其中,前两个字节为固定帧头“55H”、“AAH”;第3个字节为命令长度,为固定的“02H”;第4、5个字节为命令字,针对不同的命令会有对应的命令字;第6个字节是校验和,大小等于两个命令字的和。记录仪也采用相同的命令格式进行返回命令的上传。

为保证控制指令传输的可靠性,数据校验是必不可少的,因此,我们在协议中设计了校验码。同时,协议中还设计了命令信号从测试台、接口板、存储板、接口板,返回测试台指令反馈机制,增强了系统对错误命令的识别能力,提高了系统执行命令的抗干扰能力。

5.结论

文中研究的高速数据记录仪设备采用了双片选、双平面交替编程进行数据存储,并通过FPGA内部的二级缓冲技术,使得记录仪的总体写入速度加倍,采用合理的电路降低存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储,完全满足设计的高速存储要求。目前该系统通过了高低温、振动、冲击及电磁兼容等环境试验,能够满足实际的工程要求。(作者:侯泽雄,沈小林,姜旭刚)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。