3 性能评估

相对于现有的灵活多核处理器结构,FTPA在灵活性和通信开销上都有巨大进步,前者为FTPA 功耗和资源利用率的改进提供了巨大的优化空间,而后者则对性能带来有效提升。 本节量化评估FTPA 的低通信开销设计对程序性能的影响。3. 1 实验环境介绍

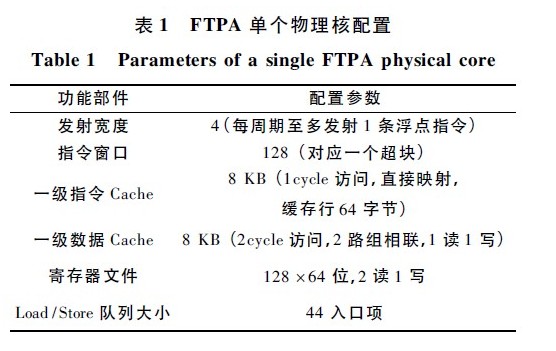

FTPA 采用EDGE 指令集,因此我们复用了TFlex 软件模拟器的指令集定义部分,而重写了微结构部分。 SPEC2K 测试程序使用Scale[16]编译器生成可执行程序,超块内指令调度拓扑选项设为4,对应每个物理核内的4 个指令子队列。 测试程序均采用Ref 输入集。 鉴于软件模拟器的速度限制,每个测试程序运行50 M 个超块。 FTPA 每个物理核的配置在表1 中列出。

3.2 实验结果及分析

使用时钟的FTPA 模拟器,我们评估了16 个物理核组成的FTPA 逻辑核性能。 图4 示出了FTPA 物理核分别配置为4 发射和16 发射时的性能对比,数据相对配置为1 发射时的性能进行了归一化处理。 从实验结果可以看到,对于SPEC2K 这样的通用应用,物理核从1 发射增加到4 发射对性能的影响显着,平均提升33. 6% .但是,物理核从4 发射增加到16 发射,对性能的提升非常小,平均只有1. 5% 的提升。 该实验结果验证了FTPA 的4 发射物理核设计的合理性。

FTPA 通信开销减小主要来自2 部分: 指令间通信和寄存器文件访问,分别对应第4 节物理核和逻辑核设计。 图5 示出了2 种通信开销的降低对性能的影响。 图5 中第1 项数据是TFlex 的性能数据,第2 项为实现4 发射物理核但仍采用全局共享寄存器文件的性能数据。 从该结果可以看出,超块内指令间通信开销的减小为程序整体性能带来了平均13. 3% 的提升。 第3 项显示了采用寄存器私有化后FTPA 的性能,从结果可以看出,寄存器文件访问通信的减少又带来平均5. 2% 的性能提升。 从而,相比于TFlex,指令间数据通信和寄存器文件访问通信开销的减少,总共为FTPA带来了平均19. 2% 的性能提升。

4 讨论

在改进通信开销和灵活性的同时,FTPA 也对处理器设计提出了新的挑战。 下一步工作主要从2 方面展开: 首先是探索何时对计算资源、何时对共享资源进行调整。 我们的思路是通过周期性统计IPC、执行部件利用率和各级高速缓存命中率,来判断对资源的调整时机; 其次,本文量化评估的程序主要是SPEC2K 这样的通用应用,对单个超块粒度而言,4 发射可以满足大部分并行需求。 但是对于数据级并行应用,4 发射物理核往往无法满足性能需求。 我们的初步想法是在逻辑核层面再增加,即首先由多个物理核组成逻辑核,每个超块对应一个逻辑核; 然后多个逻辑核再组成环形拓扑的二级逻辑核,这样在保证超块内并行性的同时,在各级逻辑上也能保持高灵活性。

5 结论

本文针对处理器核可配置的灵活多核处理器结构存在的问题,特别是在指令间通信开销、逻辑核重构开销和灵活性3 方面的不足,设计了具有低通信开销和高灵活性的FTPA 结构。 结合对通用应用的超块并行性的分析,发现4 发射的物理核可以在满足并行性的前提下,化超块内指令的数据通信开销; 同时,显式数据流编码的超块,可以通过编译器对指令放置进行静态调度,从而硬件上能够将指令窗口划分为4 个独立的子队列,有效简化指令发射逻辑的复杂度。 针对物理核中寄存器文件和高速缓存等共享资源对逻辑核灵活性的约束,FTPA 将寄存器文件对物理核私有化,同时将重构开销很大的高速缓存与容易扩展的计算资源进行逻辑上的分离,构建了逻辑拓扑环形、物理Mesh 的灵活多核处理器结构FTPA.

运行SPEC2K 测试程序的结果显示,在提供了很好的灵活性的同时,相对于采用相同指令集的TFlex 结构,指令间通信和寄存器文件访问通信开销的减少,共为FTPA 带来了平均19. 2% 的性能提升。

本文出自于中国科学院研究生院学报,作者孙涛,安虹,毛梦捷,任永青,王涛,张海博。

参考文献

[1 ] Hill M D,Marty M R. Amdahl's law in the multICore era[J].IEEE Computer,2008,41( 7) : 33-38.

[2 ] Sherwood T,Perelman E,Hamerly G,et al. Discovering andexploiting program phases[J]. IEEE Micro,2003,23 ( 6 ) :84-93.

[3 ] Ipek E, Kirman M, Kirman N, et al. Core fusion:accommodating software persity in chip multiprocessors[C]∥Tullsen D ( ed ) . Proceedings of ISCA'07. New York:ACM Press,2007: 186-197.

[4 ] Tarjan D,Boyer M,Skadron K. Federation: boosting perthreadperformance of througHPut-oriented manycorearchitectures[J]. ACM Transactions on Architecture andCode Optimization,2010,7( 4) : ( article 19) 1-38.

[5 ] Zhong H,Lieberman S A,Mahlke S A. Extending multicorearchitectures to exploit hybrid parallelism in single-threadapplications[C]∥Louri A ( ed) . Proceedings of HPCA'07.Washington: IEEE CS,2007: 25-36.

[6 ] Watanabe Y,Davis J D,Wood D A. WiDGET: wisconsindecoupled grid execution tiles [C] ∥ Seznec A ( ed ) .Proceedings of ISCA'10. New York: ACM Press,2010: 2-13.

[7 ] Kim C,Sethumadhavan S,Govindan M,et al. Composablelightweight processors[C]∥Bellas N ( ed ) . Proceedings ofMICRO'07. Washington: IEEE CS,2007: 381-394.

[8 ] Gulati D,Kim C, Sethumadhavan S, et al. Multitaskingworkload scheduling on flexible-core chip multiprocessors[C]∥Moshovos A ( ed ) . Proceedings of PACT'08. New York:ACM Press,2008: 187-196.

[9 ] Gebhart M,Maher B A,Coons K E,et al. An evaluation ofthe TRIPS computer system [C] ∥ Soffa M L ( ed ) .Proceedings of ASPLOS'09. New York: ACM Press,2009: 1-12.

[10] Burger D,Keckler S,McKinley K,et al. Scaling to the endof silicon with EDGE architectures[J]. IEEE Computer,2004,37( 7) : 44-55.

[11] Mahlke S A,Lin D C,Chen W Y,et al. Effective compilersupport for predicated execution using the hyperblock[C]∥Hwu W ( ed) . Proceedings of MICRO'92. Washington: IEEECS,1992: 45-54.

[12] Ranganathan N,Burger D,Keckler S W. Analysis of theTRIPS prototype block predictor[C]∥ Tullsen D ( ed ) .Proceedings of ISPASS'09. Washington: IEEE CS,2009:195-206.

[13] Robatmili B,Coons K E,Burger D, et al. Strategies formapping data flow blocks to distributed hardware [C]∥Gonzalez A ( ed ) . Proceedings of MICRO'08. Washington:IEEE CS,2008: 23-34.

[14] Chaudhry,Cypher S,Ekman R, et al. ROCK: A highperformanceSPARC CMT processor[J]. IEEE Micro,2009,29( 2) : 6-16.

[15] Ren Y,An H,Sun T,et al. Dynamic resource tuning forflexible core chip multiprocessors [C]∥ Hus C ( ed ) .Proceedings of ICA3PP'10. Heidelberg: Springer-VerlagBerlin,2010: 32-41.

[16] University of Massachusetts. Scale Compiler Toolset. http: ∥www. cs. utexas. edu / users / cart / Scale / index. html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。