摘要:为了在嵌入式系统设计中实现对SDRAM存储器的访问,本文提出了一种基于AMBA-AHB总线规范的SDRAM控制器设计方案。方案首先简要介绍了AMBA总线规范,然后在完成整个存储控制器的整体框架设计的基础上给出了SDRAM控制器的实现原理以及详细的子模块划分。整个控制器的设计已用Verilog HDL语言实现并通过了Modelsim仿真和FPGA验证。仿真结果表明所设计的控制器符合SDRAM内部指令操作,并且满足了严格的时序要求。

0 引言

随着大规模集成电路和高速、低功耗、高密度存储技术的发展,SDRAM动态存储器因容量大、速度快、价格低廉等优点,现已成为PC内存的主流。然而SDRAM存储器内部控制逻辑十分复杂,时序要求也非常严格,因此需要设计专门的SDRAM 控制器来实现系统对SDRAM的访问。

存储控制器是嵌入式微处理器中AMBA-AHB总线与片外存储设备之间的接口,完成总线主设备(CPU或DMA)与片外存储设备(SDRAM或SRAM)的数据传输,其功能与性能决定着嵌入式微处理器所支持的外部存储器的类型以及外部存储器的访问速度,进而决定着整个嵌入式系统的处理速度。AMBA总线规范成为嵌入了式微处理器内片上总线的标准,设计基于AMBA总线标准,支持嵌入式系统常用存储器类型的存储控制器IP具有非常大的现实意义。

1 AMBA 总线简介

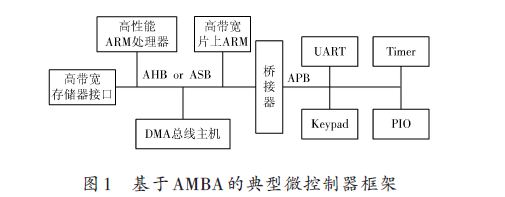

典型的基于AMBA总线的微控制器架构如图1所示。

它包含一个作为系统骨架的AHB(Advanced High-Performance Bus)或ASB总线,可实现CPU或DMA模块与片外存储器之间的大量数据通信,以获得大的带宽。

另外,在这条高性能总线上还有一个桥接器以连接低带宽的APB,而在APB上连接着大多数的系统外设。用户可以各自独立设计基于这个规范的微处理器以及外围IP,提高了系统的开发效率及模块的可重用型[6].

其中,AHB 总线是一种支持多总线主机的高性能总线,用于高性能、高时钟频率的系统,它保证了处理器与片外存储器的有效连接。一个完整的AHB传输过程可以分为地址传输阶段和数据传输阶段,地址传输阶段传输地址和控制信号,而数据传输阶段传输的是读写数据和响应信号。AHB 总线支持流水线传输,也就是说在前一个数据传输阶段可以同时进行下一个地址传输阶段,前后不同的传输阶段可以重叠起来以提高系统的数据处理速度。

2 SDRAM 工作原理

SDRAM 是一种高速高容量同步动态存储器,相比于SRAM 等静态存储器具有容量大、速度快、价格低廉等优点,成为图像处理中常用的数据存储器。但因SDRAM存储结构的特殊性,需要对SDRAM不断进行预充电、刷新等操作以保持数据不丢失。SDRAM 内部的操作是通过总线命令实现的,命令由RASN、CASN 和WEN信号联合产生,如表1所示(H表示高电平,L表示低电平)。

SDRAM上电后必须按一种确定的方式初始化。在上电稳定后100 μs时间内存储器不接受除NOP以外的任何命令。当100 μs过后,通过控制器向SDRAM所有bank 发出预充电(Precharge)命令[8],使SDRAM 所有bank进入待机状态。之后,要对SDRAM 连续执行两个自动刷新操作,使SDRAM 芯片内部的刷新及计数器进入正常运行状态。两个刷新周期完毕之后,开始对SDRAM 的模式寄存器(Mode Register)进行操作,模式寄存器用来决定SDRAM将以何种工作模式工作。整个初始化过程如图2所示。

3 SDRAM 控制器与AMBA-AHB 总线的关系

本设计基于AMBA-AHB总线的slave模块,SDRAM控制器处在片内AHB 总线与片外存储设备之间,作为一个从机挂在AHB总线上。它一边需要通过AHB总线接口模块与AHB总线通信,因此必须符合AHB总线标准;另一边又需要给外部存储设备提供控制信号,以实现对外部存储设备的读写操作。控制器接收来自总线主设备的符合AMBA-AHB 总线规范的数据传输请求,产生正确的读写控制信号给SDRAM 存储器,以完成总线的数据传输请求。

AMBA 2.0总线为嵌入式微控制器定义了一套片上总线标准,因此本设计是独立设计的基于该规范的外围IP.

4 SDRAM 控制器系统设计架构

SDRAM 控制器与AHB 总线接口在整个系统中的连接关系如图3所示。

4.1 AHB-slave总线接口电路

AHB-slave总线接口电路用来实现SDRAM 控制逻辑与AHB-master之间的信号传输。

按照AMBA 总线规范要求,AHB 总线从设备(slave)在总线时钟上升沿,HREADY信号(由从设备发出)为高的情况下,必须锁存来自AHB总线的总线控制信号、数据信号、地址信号等,以供内部译码模块以及其他各模块使用。

4.2 总线地址译码

AHB 总线可以挂多个从设备,如图3 所示的从机A,从机B.因此在读写操作中,需要对来自总线的读写地址进行译码,以判断总线是对哪个从设备进行访问,并产生相应的内部片选信号。

4.3 SDRAM控制器

SDRAM 控制器由5个模块组成:SDRAM 控制器模块、控制接口模块、命令解析模块、地址数据复用总线模块和数据通路模块。SDRAM 控制器模块是顶层模块,通过例化其他4个子模块将其连成一个整体。

4.3.1 控制接口模块

控制接口模块对来自AHB 总线信号和SDRAM 控制寄存器的信号解码并寄存,传送已经解码的NOP、WRITEA、READA、REFRESH、PRECHARGE 和LOAD_MODE命令和ADDR给命令解析模块。

控制接口模块还含有一个用于给命令解析模块产生周期刷新命令的刷新电路,用于给命令模块发送刷新请求。收到命令模块的刷新请求后,减法计数器重新装入数值,重复以上过程。

本设计所使用的MT48LC16M4A2 型号SDRAM 存储器具有每64 ms刷新4 096次的要求,因此由64 ms/4 096=15.625 09 μs知,器件必须至少每15.625 09 μs刷新。假如存储器和SDRAM控制器工作在100 MHz的时钟周期下,那么刷新间隔周期的数值是15.625 μs/0.01 μs=1 562 d.

4.3.2 命令解析模块

命令解析模块接收控制接口模块输出的已经解码的命令和周期性输出的刷新请求,产生合适的命令给SDRAM器件。从刷新控制逻辑电路发出的刷新请求比主机接口的命令的优先级别高,因此模块还含有一个简易的仲裁电路,用于仲裁主机的命令和刷新控制逻辑所产生的刷新请求。

在仲裁电路已经接受主机命令后,命令被送到模块的命令发生器部分,命令模块使用3个移位寄存器来产生命令之间的时序,一个移位寄存器用于控制ACT 命令;第二个用于控制读或写命令发出的时间;第三个用于对命令的持续时间定时,这样仲裁其就可以判断近请求的操作是否已经完成。

命令解析模块所产生的输出信号OE用于控制数据通路模块的输入数据通路的三态缓冲。

4.3.3 地址数据复用总线模块

该模块实现SDRAM的地址复用,地址的行部分在ACT(RAS)命令时复用到SDRAM输出的A[11:0],地址的列部分在读(CAS)或写命令时复用到SDRAM地址线上。

4.3.4 数据通路模块

数据通路模块提供了SDRAM和主机之间的数据接口,负责SDRAM控制器与外部SDRAM存储器之间的数据交换,具体说就是在对SDRAM写操作时将来自AHB总线的数据放到外部数据线上,在对SDRAM读操作时,将来自SDRAM的数据正确送到AHB总线上。

5 设计实现与仿真结果

本文使用Micron 公司提供的型号为MT48LC16M4A2 的Verilog 仿真模型进行仿真验证,证明了设计的正确性。仿真结果如图4,图5所示,图4是SDRAM写操作的仿真时序图,即将AHB总线控制操作转化成SDRAM 写操作指令;图5 表示的是将写入SDRAM的数据连续读出的仿真时序。

6 结语

本方案设计了一个基于AMBA-AHB 总线的SDRAM控制器,将AMBA-AHB 总线的控制操作转化成了符合SDRAM 操作规范的控制指令,的仿真波形证实了该设计的正确性。(作者:韩良,刘卫东)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。