摘要:针对降低多模式开关电源控制芯片在轻载与待机工作模式下功耗,提高其全负载条件下工作效率的需要,提出一种开关电源控制芯片供电系统的设计方案,实现了其在启动、关断、重载、轻载以及待机等各种工作情况下的高效率低功耗工作。该供电系统主要包括欠压锁定电路、数字模块电源单元和两种不同的模拟模块电源单元,以及状态检测模块和模式控制逻辑单元,能够实现电源的上电、掉电控制,同时能够根据电源的负载条件控制各模块的开通关断以实现低功耗工作。该系统已应用于绿色多模式反激式开关控制器的设计中,取得了提高电源效率、降低待机功耗的作用。芯片采用1.5 um BiCMOS工艺设计制成。测试表明,所设计电源的各项指标均已达到设计要求。

引 言

开关电源的效率与功耗已成为设计师关注的焦点,而多模式控制已经成为电源控制芯片中高效率低功耗设计的主流趋势。

所谓多模式控制就是在开关电源的工作中根据负载情况的不同采用不同的控制策略,以降低其功耗,提高效率。它是针对常用开关电源在轻载和待机条件下效率低的特点提出的,其设计思想可描述为:在重载下采用PWM 模式,以发挥其重载下效率高的优点;在轻载下采取PFM 模式,通过降低开关频率来降低功耗;而在极轻载条件下(待机模式下)则采取BURST模式来降低功耗。

目前,由于能源紧缺,国际国内均对降低用电设备的轻载和待机功耗给予了极大注意。应指出的是,传统的多模式控制策略虽然改善了开关电源的轻载与待机效率,但未对控制芯片本身的静态功耗予以足够的重视,考虑到家电、办公设备等设备数量巨大,倘能将控制芯片的静态电流由毫安级降低一至两个数量级,其节电效能就十分可观。

文中给出一种低功耗开关电源控制芯片供电系统的设计并予以实现,其特点是可以降低控制芯片在轻载与待机模式下的功耗。

针对当前应用广泛的系统芯片的需要,分别设置了一个数字模块供电单元和两个模拟模块供电单元,其中一个模拟模块供电单元专门用于在重载条件下为控制模块供电,而在轻载和待机模式下则被关断,以降低芯片的静态功耗。

1 系统与电路设计

1.1 系统构成

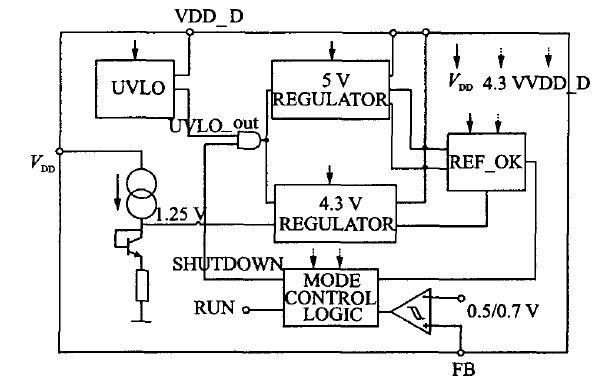

整个系统的构成如图1所示。系统中包括一个欠压锁定电路(UVLO,Under voltage lockout),用于保证电路在合适的电压范围内正常工作;一个带隙基准电压源和一个专为数字模块供电的电压源(记为VDD_D),分别为芯片提供基准偏置和数字部分的电源。具体构成时此两模块包含在UVLO模块内。两个电压调整器(REGULATOR)分别产生一个5 V和一个4.3 V 的稳定电压,其中5 V稳定电压源输出记为REG,用于在重载时为控制器供电(轻载时关断);4.3 V 稳定电压源输出记为VDD_AD,用于轻载时的供电。当然,必要时还可以利用带隙基准产生更多不同的电压以满足复杂控制模式的需要。

图1电源系统框图

此外,本设计中还设置了一个REF-OK模块来判断上电后电源系统是否已进入正常工作状态。

1.2 欠压锁定电路的设计

欠压锁定电路又称UVLO,见图2.图中 VDD为芯片外部供电电源,设计值为12 V.欠压锁定电路的窗口设置为7~9.5 V,即上电后电压上升到大于9.5V 时芯片开始正常工作,而当供电电压小于7 V时芯片停止工作。考虑到欠压锁定电路在电源控制芯片中的重要性,设计给出了两种实现方案,并对两种控制策略的性能进行了分析与比较。

图2 两个比较器实现的欠压锁定电路

图2给出种欠压锁定电路的原理图,称为U-VLO1,这是用两个比较器实现的欠压锁定电路。VDD是外部供电电压源,K1、K2 是小于1的常数,且K1>K2,VREF为1.25 V带隙基准电压,LATCH是由两个反相器组成的锁存器。图中标的UVLO_out代表欠压锁定信号,状态设置是UVLO_out=0时有效。

电路的工作原理可简述如下:12 V供电电压可在VDD比较低时建立一个PTAT (Proportional toabsolute temperature)电流源,然后利用其建立起带隙基准电压源;当VDD由0上升时,带隙基准电压r首先建立,此时两个比较器的输出为低电位,P1导通,输出为高电位;当K1VDD大于 r时,COMP1输出跳变,N1管导通,锁存器锁存上一个信号,UVLO为高电位(注意其为低电位有效);当K2VDD大于VREF 时,N2导通,则UVLO-out为低电位,使能其他模块;随着VDD减小,K2VDD首先小于VREF,N2关断,则锁存器锁存信号,UVLO-out保持;当 VDD减小到K1 VDD小于VREF时COMP1跳变,P1导通,N1关断,则输出UVLO-out为高电位,关断整个控制芯片。

表1 UVLO 的状态对应表

另一个方案是利用一个比较器实现的UVLO电路,称UVLO2.该电路的特点是通过外部迟滞实现了欠压锁定功能,可应用于高压和低压场合,如图3.电路的工作原理如下:当VDD由0上升到一个比较小的值时,带隙基准电压VREF首先建立,当VDD上升到:

时,比较器开始跳变,N1关断,UVLO-out为0,使能整个控制芯片。当外部电源电压开始减小到:

时,比较器跳转,N1开通,UVLO-out开始变l.通过合理设置R1、R2、R3值就可以使VDD1=9.5 V,VDD2=7V,即VDD上升到9.5 V时UVLO输出为零,芯片正常工作; VDD下降到7 V 时芯片停止工作。

图3 用外部迟滞实现的欠压锁定电路

两种方案的工作特性对比结果如表2所列。需要指出的是,若直接用门电路实现施密特触发,由于"的工艺离散性,将使触发电压难以准确控制。

表2 两种欠压锁定电路比较

经比较可知,UVL02结构较为简单,面积小,启动电流小,有利于降低功耗。因此,本设计终采用了UVL02方案。此外,为限度减小功耗,设计中将带隙基准电压、数字电源和欠压锁定电路集成在一起。具体电路图见图4。

图4 欠压锁定和数字电源的具体电路图

图中利用带隙基准电压加上四个二极管连接的三极管产生一个大于4 V 的电压,然后经过M0S管产生一个大约2.65 V左右的电压。这个电压在基准电压建立后就产生了,主要用于为欠压锁定电路的数字部分供电,并且担任了为整个系统的数字电路供电的任务。

1.3 5 V基准电压源(REG)

图5为5 V稳定电压源(REG)的电路原理。其中P1、P2、P3、P4组成共源共栅结构,可以提高电流镜的镜像,同时提高电源抑制比。Q3、Q4、R 1、R2组成一个带隙基准电压,这样可以减小额外的电流支路,降低功耗。Q1、Q2组成达林顿结构,增加输出能力。P5、P6增加匹配,减小沟道长度调制效应。Q1、Q2、R3、R4、R5、R6、Q4、P5、P6组成一个负反馈环路,将REG电压稳定在5 V。图中C具有两种作用:1、记忆直流工作点;2、补偿环路电容。

稳压机理如下:当负载增加时,REG电压下降,则Q4基极下降,集电极升高,经过P5、P6,使得Q1、Q2基极升高,REG 电压升高;反之亦然。

REG电压是片上多数模块的供电电压,驱动能力设计为4mA。

图5 5 V 稳定电压源

1.4 4.3 V稳定电压源

4.3 V 的稳定电压源(VDD-AD)用来在轻载时为系统供电,始终保持工作,在BURST模式下由它为模拟模块供电。

图6 4.3 V 的稳定电压源

是带隙基准电压,通过一个运放、一个达林顿结构的晶体管和一个电阻分压网络组成负反馈环路来产生4.3 V 的稳定电压。其稳压机理如下:当负载增大时,VDD-AD电压下降,此时A点电压下降,使运放的输出上升,则Q1、Q2基极升高,REG电压重新升高,获得稳定;反之亦然。

VDD-AD是检测模块的供电电压,设计驱动能力为2 mA.芯片负载减小时,关断REG,减小了芯片的静态功耗,这样既能保证芯片的驱动能力,又同时降低了芯片的静态功耗。

图7 REF-OK 电路的设计

1.5 REF_OK模块

REF_0K模块用以标志电源系统是否建立好,以控制决定供电单元是否正常开始工作。其中两个比较参考电平REFOK1、REF0K2的关系始终保持为REFOK1<REF0K2.电路的工作原理如表3,形成的滞回窗口不仅保证了REG的,而且提高了整个供电单元的抗干扰性能。

表3 REF_OK 的基本功能表

1.6 模式控制逻辑

模式控制逻辑用以保证在进行模式选择时,电源系统正常工作。当FB电压底于0.5 V时,该控制逻辑通过内部电流滞回比较器自动选择进入待机模式。RUN信号(其为高电位有效)用来关断绿色多模式反激变换器中的其它控制模块,以实现低待机功耗。

图8 模式控制逻辑

2.版图设计及测试结果

2.1 版图设计

图9给出了制得的多模式开关电源控制芯片的显微照片,其中用线框标出的部分就是所设计的供电模块,包括:欠压锁定电路,数字电源,模拟电压源(5 V稳定电压源,4.3 V稳定电压源),REF_OK等子模块。两个模拟电压源因功率较大,可视为热源,将其统一放置在版图的左边,而PTAT、带隙基准等敏感模块则尽量远离热源,放置在版图的右边,欠压锁定电路也放置在版图的右上角。

图9 芯片的显微照片

2.2 Regulator的测试

5 V 电压的PSR测试波形如图10所示。由此图可见,其PSR可以达到-60 dB.该供电模块在工作频率为40~130 kHz的绿色多模式反激式控制器中的应用表明,它对来自电源的干扰具有较好的抑制能力。

图10 5 V电源的PSR

2.3 供电系统的测试

UVLO的启动电流测量值仅为17.8 A,实现了系统的低启动电流。系统上电和掉电的测试结果如图11和图12所示。可见系统在VDD的设置门限内工作良好,REF-OK可以正确指示各个供电模块正常工作。掉电过程正好相反。

图11 供电模块的上电和掉电过程(1)

图12 供电模块的上电和掉电过程(2)

2.4 模式控制和效率测试

系统的多模式控制测试结果见图13。中载或重载下系统采用PWM 模式工作,许多单元的供电电源为REG=5 V.极轻载条件下则关断5 V的供电电源,减小系统的待机功耗,同时也有利于减小EMI和噪声。其过程如下:当FB电压低于一个阈值时,待机模式选择,则SHUTDOWN信号变高,关断5 V 电压源REG模块,同时VDD-AD继续给芯片供电,保证在轻载时芯片的检测能够连续实现。

图13 供电单元多模式下的节能过程

图14给出了集成了该低功耗电源系统的绿色多模式反激式控制器的效率图(工作频率为40~130kHz),并与传统的反激变换器效率进行了比较。由图可知,采用多模式反激式控制降低了芯片的轻载功耗,提高了效率。

图14 反激变换器效率比较

3 结 论

提出了一种开关电源控制芯片供电系统的设计方案,可在不同负载条件下为芯片提供合适的供电方案,保证其高效低功耗工作。设置的UVLO模块保证了芯片在电源波动过程中的正常工作。芯片测试的结果很好地验证了设计思想。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。