摘 要: LVDS是一种小振幅差分信号技术,使用这种技术传输速率可以达到数百兆,甚至更高; LVDS具有更低的功耗、更好的噪声性能和更可靠的稳定性。简要地介绍了LVDS的原理及优势,分析了LVDS接口设计要注意的问题,着重研究了LVDS与LVPECL、CML间的接口设计;同时给出了不同耦合方式下的电路设计图。

1 引 言

对于高速电路,尤其是高速数据总线,常用的器件一般有ECL、BTL和GTL等。这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大。此外, 采用单端信号的BTL 和GTL器件,电磁辐射也较强。目前, NS公司率先推出的CMOS工艺的低电压差分信号器件, 即LVDS给了人们另一种选择。

2 LVDS技术简介

LVDS(Low Voltage Differential Signaling)是一种小振幅差分信号技术,使用非常低的幅度信号(约350 mV)通过一对差分PCB走线或平衡电缆传输数据。它允许单个信道传输速率达到每秒数百兆比特,其特有的低振幅及恒流源模式驱动只产生极低的噪声,消耗非常小的功率。

LVDS定义在2个国际标准中: IEEE P1596.3 (1996 年3 月通过) , 主要面向SC I ( ScalableCoherent Interface) ,定义了LVDS的电特性,还定义了SC I协议中包交换时的编码; ANSI /EIA -644 (1995年11月通过) ,主要定义了LVDS的电特性,并建议了655 Mb / s的速率和1. 823Gb / s的无失真媒质上的理论极限速率。在2个标准中都指定了与物理媒质无关的特性,这保证了LVDS能成为多用途的接口标准。

3 LVDS器件的工作原理

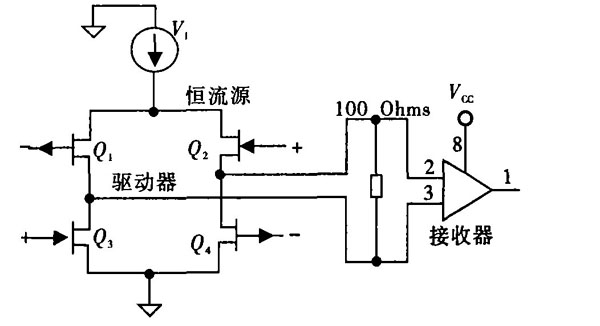

LVDS器件的工作原理如图1所示。

图1 LVDS的工作原理图

LVDS驱动器由一个驱动差分线对的电流源组成,通常为3. 5 mA.LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350 mV的电压。当驱动器翻转时,它改变流经电阻的电流方向,产生有效的逻辑"1"和逻辑"0"状态。

驱动器只有一个恒流源,这个差分驱动器采用奇模(Odd - mode)的传输方式,即等量的方向相反的电流分别在传输线路上传送。电流会重新回流到双绞线内,加上电流环路面积较小,因此产生少电磁干扰。电源将供电加以限制,以免转变时产生突变电流。由于并无突变电流出现,因此数据传输速度高达1. 5 Gb / s,但又不会大幅增加功耗。此外,恒流驱动器的输出可以容许传输线路出现短路情况或接地,而且即使这样也不会产生散热上的问题。

差分接收器是一款高阻抗芯片,可以检测小至20 mV的差分信号,然后将这些信号放大,以至达到标准逻辑电位。由于差分信号具有1. 2 V的典型驱动器补偿电压,而接收器可以接受由接地至2. 4 V的输入电压,因此可以抑制高达±1 V来自传输线路的共模噪声。

由于逻辑状态之间只有300 mV 的电压差别,因此电压变化极快, 但转换速率不会加快。

又由于转变速度减慢,使得辐射场的强度也大幅减弱。同样,传输路线阻抗不连续性的反射也不会成为大问题,有助减低电波辐射量及信号的串扰。

4 LVDS与其他几种逻辑电路的接口设计

由于LVDS是一种新技术, 因而在使用时LVDS和其他逻辑电路的接口设计就很重要,设计时,应注意以下几个问题:

(1)根据系统的工作电源配置情况和需要传输的数据电平,合理选用驱动器和接收器芯片,或者根据接口芯片的情况,对被传输的数据首先进行电平转换。

(2) 注意阻抗匹配。根据接收器输入端的情况确定是否需要外接100 Ω 电阻,同时要根据PCB的板材和参数合理设计驱动器的线输出阻抗,使其在90~107Ω 范围内。PCB传输线要尽可能地短,因为过长的线路,不但传输衰耗加大,降低了传输速率,而且阻抗也容易失配,并可能影响到信号的完整性。

(3) 根据数据传输速率和传输电缆长度的关系,确定合适的电缆长度以满足系统的要求。一般地采用LVDS方式传输数据,假定负载电阻为100Ω,当双绞线长度为10 m时,传输速率可达400Mb / s;当电缆长度增加为20 m时,速率降为100Mb / s;而当电缆长度为100 m时,速率只能达到10Mb / s左右。

(4)多数LVDS接口芯片的使能端在片内没有接上拉或下拉电阻。如果没有驱动信号输入,它们会不确定地被直接与地或VCC相连,有可能造成逻辑错误,所以除非有特别说明,接口芯片的使能输入端不要悬空。

4. 1 LVDS之间的连接

由于LVDS的芯片内输入端一般含有匹配阻抗,因此LVDS驱动器和LVDS接收器可以用一段连接线直接相连。

4. 2 LVPECL 到LVDS的互连

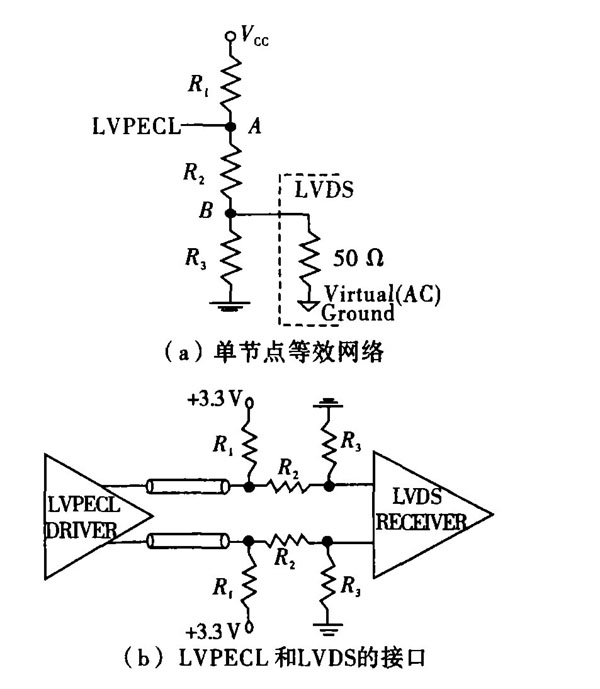

4. 2. 1 直流耦合。

LVDS和LVPECL间的直流耦合要有一个转移网络,如图2所示。首先LVPECL 输出阻抗是50Ω;另外, LVPECL 电路经过衰减网络的输出信号要在LVDS的输入范围内。下面的公式可以得到电阻的值。

图2 LVPECL 和LVDS间的直流耦合

把VCC = 3. 3 V代入(1)式,得R1 = 182Ω, R2= 47. 5Ω, R3 = 47. 5 Ω,另外VA = 1. 13 V, RAC =51. 5Ω, RDC = 62. 4Ω , Gain = 0. 337.若当使用该网络连接LVPECL 的输出端和LVDS的输入端时,那么测量的共模电压VA = 2. 1 V, VB =1. 06 V.假定LVPECL 的差分输出是930mV,那么LVDS输入端的电压就是313 mV,满足了LVDS 的输入条件。另一方面, 如果LVPECL的差分输出是1. 9 V,那么LVDS输入端的电压就是640 mV,同样满足LVDS的输入规范。

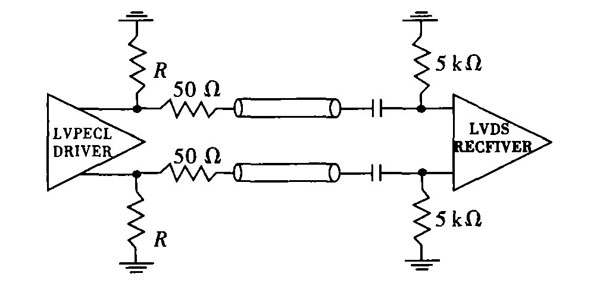

4. 2. 2 交流耦合。

LVPECL 和LVDS间的交流耦合的电路如图3所示。

图3 LVPECL 和LVDS间的交流耦合电路

LVPECL输出通过直流偏置电阻R (142Ω~200Ω )接地。50 Ω 的串联电阻来减弱LVPECL的输出电压来满足LVDS的输入要求。在LVDS输入端每端接1个5. 0 kΩ的电阻到地用来减弱共模电压。

4. 3 LVDS到LVPECL的接口

4. 3. 1 直流耦合。

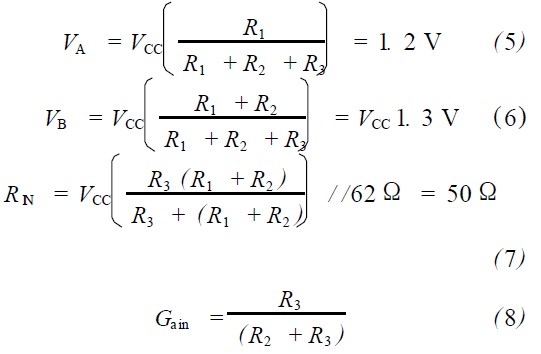

直流耦合的电路如图4所示。

图4 LVDS到LVPECL 的直流耦合。

这个电阻网络把LVDS直流输出电压从1. 2V变到LVPECL的输入(VCC - 1. 3 V) .这是因为LVDS的输出电压是参考地,而LVPECL 输入电压参考VCC ,这个网络可以使LVDS的输出不受电压变化的影响;另外考虑的就是功耗和速度的平衡。如果R1、R2、R3 选择低电阻,那么这个网络的时间常数和LVPECL的寄生参数都很小,能够满足高速的要求;当然由于电阻小了,就有更大的电流流过这些电阻,那么总功耗就大了。这种情况下LVDS的参数可能会受到电压变化的影响。电阻值可以由下列等式求得:

代入VCC = 3. 3 V、R1 = 374Ω、R2 = 249Ω、R3= 402 Ω, 得到VA = 1. 2 V、VB = 2. 0 V、RIN =49Ω, Ga in = 0. 62.LVDS的差分输出的VP - P =500 mV,信号在LVPECL输入端变成310 mVP - P.

电压变化比PECL的输入标准小,但满足LVPECL的输入要求。

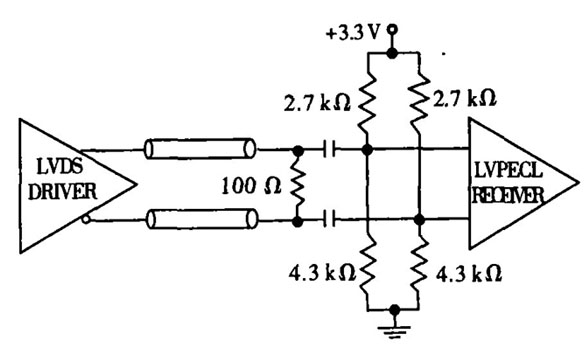

4. 3. 2 交流耦合。

LVDS到LVPECL的交流耦合很简单,图5给出了例子,LVPECL的芯片是MAX3867它的片内没有端接电阻。

图5 LVDS到LVPECL的交流耦合。

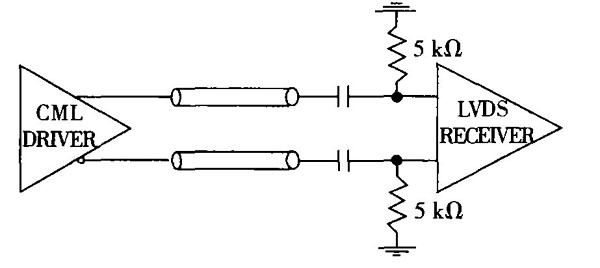

4. 4 CML和LVDS的接口

CML到LVDS的交流耦合如图6所示,要注意的一点就是CML 的输出信号漂移要在LVDS输入信号的要求范围内。

图6 CML到LVDS的交流耦合电路图。

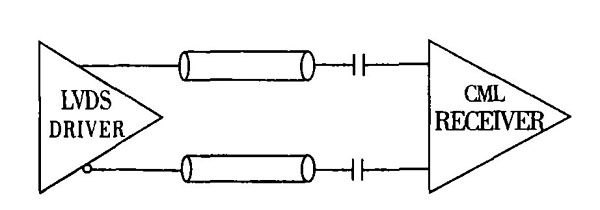

LVDS驱动器连接CML接收器的交流耦合方案如图7所示。

图7 LVDS到CML的交流耦合电路图。

5 结 论

随着信息化的发展, LVDS的高性能、低功耗、低噪声的优点,使得LVDS将成为很多设计适合的方案。LVDS不仅能够以数百兆的速率传输数据而且驱动距离可达10 m,远胜于其他标准。

这些优点可能使LVDS成为高速数据传输的标准。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。