MCU简介

MCU(Micro Control Unit)中文名称为微控制单元,又称单片微型计算机(Single Chip Microcomputer)或者单片机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时计数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。

其缩略图如下:

微控制器在经过这几年不断地研究,发展,历经4位,8位,到现在的16位及32位。产品的成熟度,以及投入厂商之多,应用范围之广,真可谓之空前。目前在国外大厂因开发较早,产品线广,所以技术,而本土厂商则以多功能为产品导向取胜。但不可讳言的,本土厂商的价格战是对外商造成威胁的关键因素。

32位MCU性能差距

由于制程的改进,8位MCU与4位MCU价差相去无几,8位已渐成为市场主流;目前4位MCU大部份应用在计算器、车用仪表、车用防盗装置、呼叫器、无线电话、CD播放器、LCD驱动控制器、LCD游戏机、儿童玩具、磅秤、充电器、胎压计、温湿度计、遥控器及傻瓜相机等;8位MCU大部份应用在电表、马达控制器、电动玩具机、变频式冷气机、呼叫器、传真机、来电辨识器(CallerID)、电话录音机、CRT显示器、键盘及USB等;16位MCU大部份应用在行动电话、数字相机及摄录放影机等;32位MCU大部份应用在Modem、GPS、PDA、HPC、STB、Hub、Bridge、Router、工作站、ISDN电话、激光打印机与彩色传真机等。

MCU领域如今仍由 8 位和 16 位器件控制,但随着更高性能的 32 位处理器开始在 MCU 市场创造巨大收益,在系统设计方面,芯片架构师面临着 PC 设计人员早在十年前便遇到的挑战。尽管新内核在速度和性能方面都在不断提高,一些关键支持技术却没有跟上发展的步伐,从而导致了严重的性能瓶颈。

很多 MCU 完全依赖于SRAM以及NOR这两种类型的内部存储器件。在新 32 位内核的尺寸和运行速度方面,嵌入式 SRAM 技术正在保持同步其在 100MHz 的运行范围更易于实现。对 MCU 所需的典型 RAM 容量来说,这个速度级别也更具成本效益。

但是标准的 NOR 闪存却落在了基本 32 位内核时钟速度之后,几乎相差一个数量级。当前的嵌入式 NOR 闪存技术的存取时间基本为 50ns (20 MHz)。这在闪存器件和内核间转移数据的能力方面造成了真正的瓶颈,因为很多时钟周期可能浪费在等待闪存找回特定指令上。

XIP为eXecute In Place的缩写,就是WINCE XIP KERNEL,是CE部分,XIP是MCU标准的执行模型,它更加剧了处理器内核速度和闪存存取时间之间的性能差距。

从闪存执行的两个主要原因是大容量存储中的应用容错及SRAM较高的成本。存储在闪存内的程序比较稳定,基本不会被系统内的随机错误破坏,如电源轨故障。利用闪存直接执行还无需为MCU器件提供足够的 SRAM,来将应用从一个 ROM 或闪存器件复制至目标 RAM 执行空间。

消除差距

理想的情况是,改进闪存技术,以匹配32位内核的性能。虽然当前的技术有一定的局限,仍有一些有效的方法,可帮助架构师解决性能瓶颈问题。

简单的指令预取缓冲器和指令高速缓存系统在32位MCU设计中的采用,将大大提高MCU的性能。下面将介绍系统架构师如何利用这些技术将16位的MCU架构升级至32位内核CPU。

在 MCU 设计中引入 32位内核

图1明确的显示了新32 位内核及其基本外设集合之间的基本联系,由于我们在讨论将新的32位处理器内核集成至新的MCU设计及,我们假设可采用新32位内核采用以下规范。

改良的哈佛架构

新的32位内核也采用改良的哈佛架构,程序存储和数据存储空间是在两个独立的总线构架上执行。一个纯哈佛设计可防止数据在程序存储空间被读取,该内核改良的哈佛架构设计仍可实现这样的操作,同时,该32位内核设计还可实现程序指令在数据存储空间的执行。在标准总线周期内,程序和数据存储器接口允许插入等待状态,有助于响应速度缓慢的存储或存储映射器件。

工作频率

新内核的工作时钟频率为120MHz,是被替代的16位内核速度的六倍。

指令存储器接口

指令存储系统接口有一个32位宽的数据总线,以及一个总共地址空间为1MB的20位宽的地址总线。尽管 32位内核具备更大的地址空间,而这足够满足这个MCU的目标应用空间。标准的控制信号同样具备为缓慢的存储器件插入等待状态的能力。该设计的闪存器件与16位设计采用的技术一样,运行速度达20 MHz。

数据存储器接口

系统SRAM和存储器映射外设都通过系统控制器与处理器数据总线相连。系统控制器可提供额外的地址解码及其他控制功能,帮助处理器内核正确访问数据存储器或存储器映射外设,而无需处理特定的等待状态、不同的数据宽度或每个映射到数据存储空间的器件的其他特殊需求。系统控制器和处理器内核之间的数据总线为 32 位宽,与系统控制器和SRAM 间的数据总线宽度相同。系统控制器和外设以及 GPIO 端口间的数据总线宽度可为 8 位、16 位或 32 位,视需求而定。目标设计采用的 SRAM 与 16 位设计采用的类型相同,在 120 MHz时可实现 0 等待状态操作。

起步解析

目前系统的性能由这几个因素控制:

处理器内核与闪存器件速度的差异可极大地影响性能,因为至少有五个等待状态必须添加到每个指令提取中。根据粗粒经验法则,至少每十个指令有一个读取或存储。每条指令加权平均周期(CPI)的典型顺序为:

CPI = (9 inst * 6 闪存周期 + 1 inst *1 SRAM周期) / 10 指令

CPI = 5.5

内核的吞吐量由闪存接口的速度决定,因此以前所有的32位内核都是数据通道宽度的两倍。

在这种情况下,SRAM接口无关紧要。虽然某些问题很有可能源于存储接口方面,如中断延迟和原子位处理,SRAM存储器的零等待状态操作可以忽略。关注的重点是通过采用目前可用的、具有成本效益的技术,来提高指令存储接口的性能。

提高CPU内核性能——闪存接口

来自高性能计算环境的一个通用概念是高速缓存,在主要存储器件和处理器内核之间采用更小及更快的内存存储,可以实现突发数据或程序指令的更快访问。

设计和实现高速缓存可能非常复杂——需要考虑高速缓存标记、N-Way级联和普通高速缓存控制等问题——仅关注程序指令存储器可让这项工作变得非常简单。这是因为对此特定的 32 位内核来说,对程序存储器的访问是一个严格的只读操作。在这种情况下,我们只需考虑一个方向的数据流可以减少缓冲器和高速缓存系统的复杂性。

预取缓冲器

增加闪存接口总体带宽的一个简单方法是扩展处理器和闪存器件间的通道宽度。假定闪存的速度一定,增加带宽的另外一个方法是扩展接口宽度,以实现提取更多指令,创造一个更为快速的闪存接口外观。这是预取缓冲器的一个基本前提。它利用了连接闪存的更宽接口的优势,可在同样的时钟周期数内读取更大的数据量,这通常只要花闪存读一个字的时间。因此,预取缓冲器还定义了新数据通道的尺寸,原因显而易见。

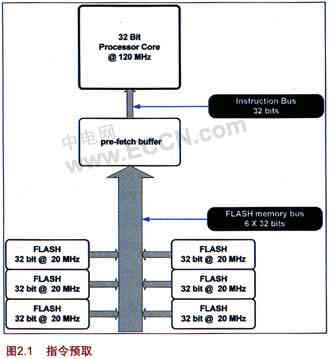

图2.1显示了我们的120 MHz内核连接到20 MHz闪存阵列的情况。

在这种情况下,预取/闪存数据通道将是:(120/20)X32位=192位宽。预取缓冲器控制逻辑可识别每次进入的有效地址,供以适当的解码按正确的顺序指令显示处理器数据总线,当一个执行分支需要完整的新的顺序指令时,将重新加载缓冲器。

由于提取新的指令时,分支比将造成一些额外的延迟。相比处理器内核,预取缓冲器的六合一方法在数据通道宽度方面具有的优势,为该分支问题的终平衡的结果付出的代价是值得的。

更多经验法则分析都显示,一个典型的嵌入式应用有20%发生分支的机会,每五个周期相当于一个分支。采用之前的方法,CPI值现在为:

CPI = (4指令*1周期+1指令*6周期)/5指令=2.0 此方法有效的提高了整个系统周期,使得效率打打增加。

图2.1显示的六个独立的闪存系统的32位总线加在一起为方法也是相当不错的。预取缓冲器控制逻辑将自动创建六个连续的程序地址,然后允许一个正常的读取周期同时访问所有六个组。在读取周期的末尾,预取缓冲器现在可保持六个新的指令,模拟的零等待状态系统。

指令高速缓存

形式指令高速缓存赋予预

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。