摘要:提出了利用双口RAM实现高时间分辨率光谱测量系统中DSP与ICCD并行接口的设计方案。以确保使双方的高速通信。介绍了双口RAM器件IDT7007的原理与使用规划,并针对方案,给出了接口电路和软件流程。针对二者交换数据的仲裁方式,提出了解决冲突争端的方法。整体系统通过调试,证明文中采取的中断,忙逻辑,软件协调三种模式,有效解决了两个系统之间的通信争端。信息处理系统与ICCD可良好协调工作,系统运行稳定,构成合理,保证了整体系统的实时性。

增强型电荷耦合器件(Intensified Charge Coupled Device,简称ICCD)作为一种数据采集部件,因其采集光谱数据量大,快门时间达ns级,采集速率高的特点,在高时间分辨率光谱系统中应用较广。这样组成的双口RAM系统可以全速运行,而且无须任何额外的附加逻辑。在高分辨率光谱测量分析系统中,为了与ICCD子系统实时通信,及时处理IC-CD子系统采集到的信息,作为实时信息处理器件的DSP子系统必须与ICCD子系统采取一种高速的并行接口方案。因此在实际的双机通信系统中,一般通过双口RAM实现并口通信。双口RAM具有以下优越的性能特点:

㈠、两套完全独立的数据线、地址线、读/写控制线,允许两个CPU对双端口存储器的同一单元进行同时存取;

㈡、有两套完全独立的中断逻辑来实现两个CPU之间的握手控制信号;

㈢、具有两套独立的“忙”逻辑,保证两个CPU同时对同一单元进行读/写操作的正确性;

㈣、兼容性强,读/写时序与普通单端口存储器完全一样,存取速度几乎可以满足各种CPU的要求。

因此。我们采用了双口RAM来实现DSP子系统与ICCD子系统之间的高速通信。

1.1 器件简介

IDT7007是美国IDT公司采用高性能的CMOS工艺生产的高速32 k×8 bit双端口静态RAM,典型功耗850 mW;存取时间:15 ns;工作环境:-45℃~+85℃;工作电压:5 V±10%。它可以作为8位双口RAM单独使用,也可以进行位扩展,将数据线扩展到16 Bit,甚至更宽。CY7C006A是Cypress公司生产的16 kb×8高速双口静态RAM,存取速度小于20 ns。该器件具有真正的双端口,可以同时进行数据存取,两个端口具有独立的控制信号线、地址线和数据线,另外通过主/从选择可以方便地扩存储容量和数据宽度。通过器件的信号量标志器,左、右两端口可以实现器件资源共享。

双口RAM是在1个SRAM存储器上具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对其进行随机性访问的存储器,即共享式多端口存储器。双口RAM的特点是存储数据共享。1个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。因为数据共享。则必须具有访问仲裁控制。内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配:信令交换逻辑(例如中断信号)等。双口RAM可用于提高RAM的吞吐率,适用于实时数据缓存。

双口RAM器件IDT7007固体成像、信号处理和大容量存储器是 CCD的三大主要用途。各种线阵、面阵像感器已成功地用于天文、遥感、传真、卡片阅读、光测试和电视摄像等领域,微光CCD和红外CCD在航遥空感、热成像等军事应用中显示出很大的作用。在N型或 P型硅衬底上生长一层二氧化硅薄层,再在二氧化硅层上淀积并光刻腐蚀出金属电极,这些规则排列的金属-氧化物-半导体电容器阵列和适当的输入、输出电路就构成基本的 CCD移位寄存器。对金属栅电极施加时钟脉冲,在对应栅电极下的半导体内就形成可储存少数载流子的势阱。

1.2 器件使用

单片使用、不进行位扩展时,IDT7007的真值表如表1:

X:无关;H:逻辑高;L:逻辑低。

2 接口电路设计

系统中,ICCD子系统负责数据采集,DSP子系统负责信息处理。ICCD采集光谱数据,将数据写入到双口RAM的指定存储单元。DSP再将双口RAM中的数据转移入内存储器,进行分析处理,以及其他运算。体沟道CCD的电荷转移机理和表面沟道CCD略有不同。体沟道CCD又称为埋沟CCD。所谓体沟道即用来存储和转移信号电荷的沟道是在离开半导体表面有一定距离的体内形成。体沟道 CCD的时钟频率可高达几百兆赫,而通常的表面沟道CCD只几兆赫。

双口RAM与DSP芯片之间,我们采取8位数据线的接口宽度,地址线12位,可寻址空间应为32 k×8 bit。

ICCD通过一条数据线与信息处理系统上的扩展接插板相连。二者间接口信号定义如表2:

二者之间的电路框图如图1。

如图1所示,双口RAM的左端与DSP相连,作为DSP系统的扩展存储器,共同构成了信息处理系统。双口RAM的右端,与ICCD子系统相连,也可以认为是ICCD子系统的一个外存储器。为了保护ICCD子系统的处理器,我们在双口RAM和ICCD之间加了总线收发器SN74LVCC3245,对信号进行隔离与调理电平。

3 信息处理系统与ICCD交换数据的仲裁方式

对于整个系统来说,两个子系统之间合适的仲裁方式是极为重要的。处理不好数据交换的仲裁。就会使两个系统之间发生冲突。比如当DSP系统对双口RAM的一个存储单元进行写操作时,ICCD系统也对这个单元写入数据,就必然导致写操作的错误。抑或是当ICCD系统对双口RAM的某一存储单元进行读取时,DSP也对这个单元读操作,就会造成读数据的错误。我们采取了三种有效的仲裁方式,用于解决两个系统之间的通信争端:

㈠、中断方式:双口RAM提供了一种特殊的中断方式,有别于其他芯片的中断。

IDT7007左右两端各提供一个中断信号。存储阵列中的FFEH和FFFH单元被用做通信的信令字和中断源,左端口向FFFH写入访问的同时,右端口的中断标志被设置,直到右端口进行读取FFFH时清除,右端给左端的中断方式与此类似。这样就可以有效地协调通信双方的读写操作。图2为双方接口的中断逻辑。

㈡、忙逻辑:当双口RAM的两个端口同时对某一个存储单元进行操作时,IDT7007的忙逻辑(BUSY)将会有一个硬件的指示,允许对其中的一个端口进行操作,将另一个端口置于等待状态。如果在接到BUSY信号时,已经进行写操作,那么IDT7007的内部机制可以阻止写操作的继续进行。

系统中,为了提高系统的稳定性,保证通信数据的正确,我们对IDT7007原有的忙逻辑进行了修改。硬件方面将双口RAM原有的两个BUSY信号求逻辑或,这个结果再与中断信号INT求逻辑或。这样,只要通信双方同时读写同一个存储单元,系统就认为读写非法,同时中断双方的读写操作。这样可以提高双方交换数据的正确性。

在探索磁泡器件的电模拟过程中,产生了电荷耦合器件的原理设想,并在实验中得到验证初期的CCD存储和转移信号电荷的势阱都位于硅-二氧化硅界面处,即所谓表面沟道CCD。1972年D.康首先设想了多数载流子CCD形式,在此基础上人们研制出体沟道CCD和“蠕动”型CCD的新结构,有效地改善了CCD的性能。1973年美国仙童公司制成CCD摄像传感器,CCD遂从实验室进入工业生产的实用阶段。双口RAM器件IDT7007可用光注入或电注入的方法将信号电荷输入势阱。然后周期性地改变时钟脉冲的相位和幅度,势阱深度则随时间相应地变化,从而使注入的信号电荷在半导体内作定向传输。

图3即为通信双方接口的BUSY逻辑时序:

㈢、软件协调:对于任何一个双机系统来讲,双方的软件设计都是避免争端冲突的重要环节。软件方案将在下一节详细介绍。

4 软件设计方案

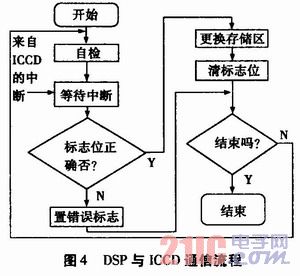

系统中,ICCD(右方)主要负责发送数据,信息处理系统(左方)主要负责接受数据。信息处理系统的软件基于TI的TMS320C6713,用C语言与线性汇编语言进行编程。通信部分的软件主要包括了两方面的内容:(1)系统自检,即右方向信令字单元0xFFFH写入“5AH”,左方接到中断后,到0xFFFH中读取数据,如果是“5AH”,说明通信正常,反之亦然。(2)传输数据,右方向信令字单元FFFH写入‘A5H’,在左方产生中断后,左方读信令字单元FFFH,如果是‘A5H’,说明在传输数据,读完数据后,向信令字单元FFEH写入‘AAH’,表示读完。右方接到中断后,读信令字单元FFEH,如果是‘AAH’,表示传数据成功。

图4为基于DSP的通信程序流程:

5 结论

基于双口RAM芯片IDT7007实现DSP系统与ICCD并行接口的设计方案,实现了ICCD和信息处理系统的高速通信,保证了整体系统的实时性。文中所涉及的中断,忙逻辑,软件协调三种模式,可有效解决两个系统之间的通信争端。整体系统已经通过调试,信息处理系统与ICCD可良好协调工作,系统运行稳定,构成合理,对相关系统设计有一定的参考价值。

本设计采用自顶而下的设计思想。选用Xilinx公司的Spartan-6 FPGA器件,基于低功耗45 nm、9-金属铜层、双栅极氧化层工艺技术,提供功耗管理技术,150 000个逻辑单元,集成式PCI Express模块,存储器支持。250 MHz DSPslice和3.125 Gb/s低功耗收发器。通过Verilog HDL语言对双口RAM功能的描述就能在一片FPGA器件内实现8位16字节的双口RAM,并进行读写操作控制。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。