引 言

System on Chip的缩写,称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。 它是信息系统的芯片集成,是将系统关键部件集成在一块芯片上;从广义角度讲, SoC是一个微小型系统,如果说中央处理器(CPU)是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。国内外学术界一般倾向将SoC定义为将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常是客户定制的,或是面向特定用途的标准产品。 集成电路的发展已有40年的历史,它一直遵循摩尔所指示的规律推进,现已进入深亚微米阶段。由于信息市场的需求和微电子自身的发展,引发了以微细加工(集成电路特征尺寸不断缩小)为主要特征的多种工艺集成技术和面向应用的系统级芯片的发展。随着半导体产业进入超深亚微米乃至纳米加工时代,在单一集成电路芯片上就可以实现一个复杂的电子系统,诸如手机芯片、数字电视芯片、DVD 芯片等。在未来几年内,上亿个晶体管、几千万个逻辑门都可望在单一芯片上实现。 SoC设计技术始于20世纪90年代中期,随着半导体工艺技术的发展,IC设计者能够将愈来愈复杂的功能集成到单硅片上, SoC正是在集成电路( IC)向集成系统( IS)转变的大方向下产生的。1994年Motorola发布的FlexCore系统(用来制作基于68000和PowerPC的定制微处理器)和1995年LSILogic公司为Sony公司设计的SoC,可能是基于IP核完成SoC设计的早报导。由于SoC可以充分利用已有的设计积累,显着地提高了ASIC的设计能力,因此发展非常迅速,引起了工业界和学术界的关注。

l 系统总体设计

图1为基于FPGA的射电宇宙信号处理框图。

该设计是基于SoPC技术设计的Chirp函数信号发生器,该系统把微处理器模块和DDS模块集成到单片FPGA芯片内部,通过在嵌入式操作系统μC/OS-Ⅱ编写的程序,实时控制微处理器对DDS的控制字输出,DDS模块根据频率控制字的不同,输出不同的数字化正弦波。使之符合Chirp函数的时变频率特征。Chirp函数根据输出频率的递变规律一般分为两种:线性Chirp函数和非线性Chirp函数,以下是两种Chirp函数在频域上的表现图如图2,图3所示。

从图2,图3可以看出Chirp函数的频率输出与时间的f-t关系可以总结为:

(1)对于线性Chirp函数

在连续域时间域内有关系式:

![]()

式中:k为常数;f0为初始输出频率;t为连续时间。

在离散时间域有关系式:

![]()

式中:k为常数;f0为初始输出频率;n为采样点。

(2)对于非线性Chirp函数

在连续域时间域内有关系式:

![]()

式中:f为非线性函数;f0为初始输出频率;t为连续时间。

在离散时间域有关系式:

![]()

式中:f为非线性函数;f0为初始输出频率;n为采样点。

因此该Chirp信号源的功能是:在NiosⅡ中建立的微控制器;使用嵌入式操作系统μC/OS-Ⅱ建立对DDS频率控制字输出实时改变的任务;根据线性和非线性Chirp函数的特点控制字的输出根据需要线性或者非线性输出,并且在此设计中将该任务的优先级设置为。利用VHDL语言编写DDS模块,首先根据Matlab计算出需要的正弦数据,然后将这些数据存储于ROM中供DDS模块调用,具体结构如图4所示。

2 DDS模块的设计

一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。在各行各业的测试应用中,信号源扮演着极为重要的作用。但信号源具有许多不同的类型,不同类型的信号源在功能和特性上各不相同,分别适用于许多不同的应用。目前,常见的信号源类型包括任意波形发生器,函数发生器,RF信号源,以及基本的模拟输出模块。信号源中采用DDS技术在当前的测试测量行业已经逐渐称为一种主流的做法。

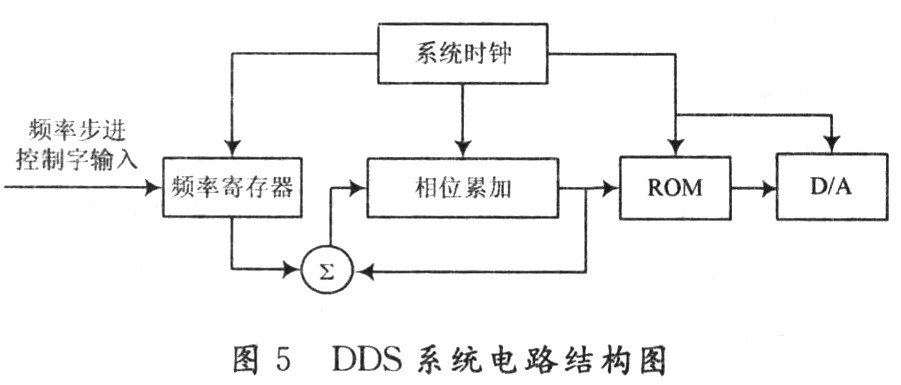

数字式频率合成器(DDS)模块的工作原理是:将O~2π的正弦函数值分为N份,将各点的幅度值存入ROM中,再用一个相位累加器每次累加相位值ωT,得到当前的相位值,通过查找ROM得到当前的幅度值。其系统框如图5所示。

DDS的几个主要参数是:系统时钟频率,频率控制字长,频率分辨率,ROM单元数,ROM字长。该设计的DDS是32位的,时钟频率为50 MHz,频率控制字长为32位,ROM单元数为2的11次方,ROM字长为16位。而且有如下关系:

频率分辨率=系统时钟频率/232;

频率控制字(FTW)=f×232/T;

其中:f为要合成的频率;T为系统时钟。

DDS的工作过程为:每次时钟的上升沿到来时,相位累加器(32位)中的值累加上频率寄存器(32位)中的值,再利用累加器的高11位作为地址进行ROM查表,输出相应的幅值数字信号。

如果是扫频工作,只需要根据一定的规律实时修改频率控制字,就可以达到扫频输出的目的。但是该系统的性能受到以下两个方面的制约:ROM单元数和ROM数值的有限字长。由于ROM大小的限制,ROM的单元地址位数一般都远小于相位累加器的位数,这样只能取相位累加器的高位作为ROM的地址进行查询,这就相当于引入了一个相位误差。为了解决ROM的受限问题,该设计采用ROM压缩技术。因为正弦函数存在对称和反转特性,即:

对于O~2兀的幅度值,可以只存储O~π/2的部分。这样原本需要的2的11次方个单元的ROM现在只需要2的9次方个单元的ROM就可以实现。在MatIab中产生16位512点的O~π/2正弦波数据的命令如下:

![]()

将Y数据依次存入Altera公司提供的Megawiz-ard宏单元实现的ROM中即可。

3 嵌入式微处理器的实现

嵌入式微控制器的典型代表是单片机(Microcontroller Unit),这种8位(8根数据线,8位指令)的电子器件目前在嵌入式设备中仍然有着极其广泛的应用。微控制器的特点是单片化,体积大大减小,从而使功耗和成本下降、可靠性提高。嵌入式微处理器的设计包括3个部分:利用SoPCBuilder定制的软核CPU,在QuartusⅡ环境下设计的电路和NiosⅡ编程。

本设计的软核CPU采用NiosⅡ/S标准型内核,带有16 KB的Cache;集成了外部的FLASH和SDRAM控制器用于保存程序数据;Jtag_Hart电脑开发板传输接口用于建立良好的用户交互接口使用户能在console界面上观察程序运行情况;两个位宽分别为8位和3位的输出口作为输出DDS模块的控制字。

NiosⅡ的编程主要是基于嵌入式操作系统μC/OS-Ⅱ,μC/OS-Ⅱ是一个完整的、可移植、固化和剪裁的占先式实时多任务核(Kernel)。从1992年发布至今,μC/OS-Ⅱ已经有了上百个的商业应用,在40多种处理器上成功移植。

μC/OS-Ⅱ提供以下系统服务:任务管理(TaskManagement);事件标志(Event Flag);消息传递(Message Passing);内存管理(Memory Management);信号量(Semaphores);时间管理(Time Management)。

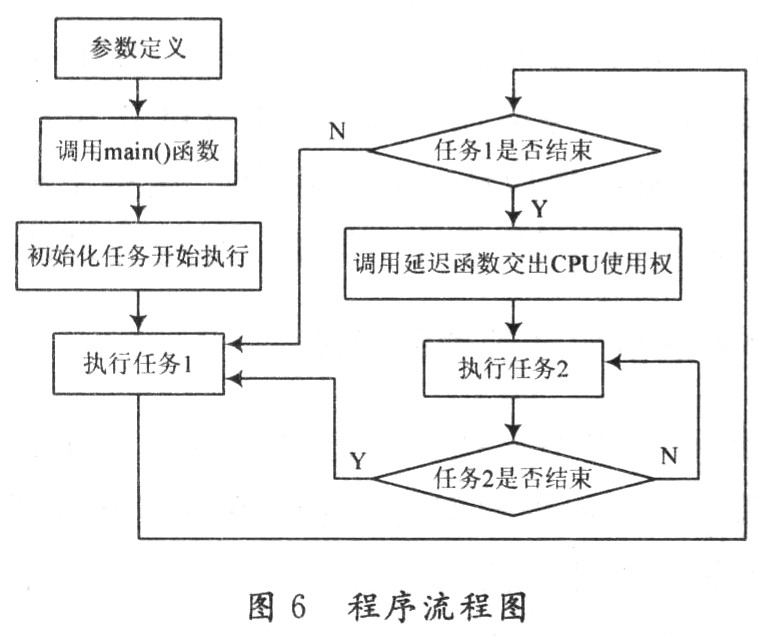

在该设计中建立一个主函数和两个任务函数,主函数的功能:调用系统任务初始化函数OSTaskCreateExt()初始化两个任务函数:调用系统开始函数OSStart()启动系统开始工作。

任务1:实时的改变DDS控制字的输出,并且保持一段时间,在遍历完所有的需要频率以后,延迟调用系统延迟函数OSTimeDlyHMSM(),延迟63 s将该使用权交付给任务2。

任务2:为了保证该系统以后能有功能扩展,建立一个任务,其仅仅是通过函Jtag_uart接口使用函数printf(),向电脑发送一个任务2已经开始工作的提示信息,如果以后需要扩展功能则只需修改任务2即可。程序的具体流程图如图6所示。

在任务1中实时改变变量i的值步进为1,通过定义的Chirp函数关于时间和输出频率控制字之间的关系函数function(),计算得到此时的频率控制字f,并且将f的值通过API函数IOWR_ALTERA_AVALON_PIO_DATA()从I/O端口输出以控制DDS,然后延迟2 s使DDS保持该输出频率一段时间,并且通过Jtag_uart端口在Console调试界面向用户提示当前的信号源的输出频率,程序如下:

图7为QuartusⅡ中生成的嵌入式软核示意图。

4 结 语

该设计在21controll公司提供的V4.O FPGA/SoPC开发学习套件上面通过仿真验证,该套件的芯片为CycloneⅡ系列:EP2C20F484C8,其具有18 752个逻辑单元(LE)和52个M4K RAM块,能够很好地设计存储需要的数据,完全符合设计要求。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。