1.引言

传统上 FPGA只能实现相对较小的逻辑电路,随着工艺技术的提高,FPGA的容量和性能也不断提高,FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

然而,多数学术性的 FPGA CAD工具只针对于同质的 FPGA,即只包含逻辑模块和布线资源的 FPGA。本文中我们提出了一种灵活的包含嵌入式存储器的 FPGA的结构以及一种建立RRG(布线资源图)的方法。FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器件。与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及个模块之间或模块与I/O间的连接方式,并终决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并终决定了FPGA所能实现的功能, FPGA允许无限次的编程。

2.结构

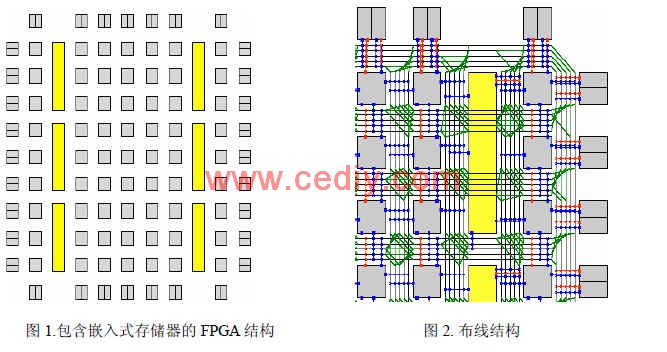

包含嵌入式存储器的FPGA结构如图1所示。整个 FPGA由四种基本资源构成,逻辑模块,I/O模块,布局布线模块和存储器模块。每个存储器模块的存储容量是固定的,但是用户可以对存储器模块进行配置,以实现不同长宽比的存储器。我们假设存储器模块在整个 FPGA芯片中按列排放。存储器模块的列数,每列存储器所处的位置、每列存储器模块包含的存储器模块数目以及每列存储器模块中个存储器模块的起始物理位置都会在结构描述文件中定义。

图 2所示为我们的 FPGA布线结构,这是一种岛式结构。逻辑模块周围围绕了布线通道。每个逻辑模块的输入或输出引脚可以通过一个由可配置开关组成的连接模块与靠近它的通道中的 8条连线相连。在每一个垂直通道和水平通道交叉处有一个开关模块。开关模块给每条输入信号线提供了三个可能的连接选择。同逻辑模块相同,存储器模块也通过连接模块与逻辑布线相连。在图 2中的结构中, Fm=3。Fm的值是 1,值为 V,这里的 V值即每个布线通道中的连线数目。

3.具体实现方式

存储器模块相对于逻辑模块,有一些不同之处,例如模块引脚的分布方式、模块高度等,这使得 RRG的设计非常复杂。在这一部分中,我们将讨论一种简单而且灵活的 RRG设计方法。

3.1结构描述

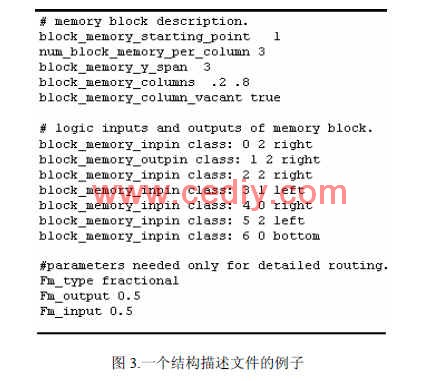

VPR用布线结构描述语言定义 FPGA的布线结构【 5】。VPR通过一个内部的“结构产生器”来产生 RRG。我们扩展了布线结构描述语言来定义包含嵌入式存储器的FPGA的布线结构,然后我们改进了 VPR的结构产生器以适应这些扩展。

由于嵌入式存储器模块的存在,我们对布线结构描述语言的扩展主要包括:(1)存储器模块的列数,(2)每列存储器模块的相对位置,(3)存储器模块输入和输出引脚的 Fm值,(4)每列存储器模块中的存储器模块数目,(5)每列存储器模块中个存储器模块的起始位置,(6)存储器模块的高度,(7)存储器模块输入输出引脚的数目,(8)存储器模块每个输入或输出引脚对应的边( side)和群( cluster),例如如图 2所示的 FPGA结构中,存储器模块的左边和右边共有 3个群,因为存储器模块的高度是 3个逻辑模块的高度,而上下两边只有一个群。(9)每个存储器模块中的组合逻辑电路延迟和时序电路延时。

图 3所示为一个描述包含嵌入式存储器的 FPGA布线结构的文件的一部分,其中逻辑模块由一个 4输入的查找表和一个寄存器构成。图 1和图 2示出了这种 FPGA的结构。VA产生的文件要满足图 3定义的结构,其中需要的布线通道宽度为 5,即 5条连线。这些描述 FPGA结构的图形都是由我们的 VA产生。图 1示出了整个 FPGA的结构,这种情况下,整个 FPGA包含 9x9个逻辑模块,周围围绕 I/O模块。黄色所示的为两列存储器模块,每个存储器模块跨越 3个逻辑模块的高度。图 2所示仅为FPGA近距离结构的一部分。

3.2布线资源图

虽然上述所列的结构参数使得 FPGA的结构很容易就可以定义,但是对于布线器来说它并不是一个合适的表达方法。在 RRG中,连线、逻辑模块的引脚以及存储器模块的引脚都被表示为节点,开关被表示为连接两个节点的边。

如前所述,我们对 VPR的结构产生器作了改进以建立包含嵌入式存储器的 FPGA的 RRG。由于存储器模块在 Y方向跨越多个逻辑模块,这就使得在 RRG中插入存储器模块的引脚变得复杂,同时连接从存储器模块输出引脚到连线以及从连线到存储器输入引脚的边也更加复杂。但幸运的是如图 2所示,存储器模块的存在并不破坏布线通道的分布。为了方便建立 RRG,我们增加了虚构存储器模块的定义,在建立 RRG的过程中,存储器模块的位置由它的起始位置来表示。当在建立 RRG对所有模块进行扫描的时候,我们对存储器模块以及虚构存储器模块的处理方法和对逻辑块的处理方法是一样的。通过这样的方法,我们简化了创建异质 FPGA布线资源图的过程。

4.结论

本文中,我们提出了一种包含嵌入式存储器的 FPGA的灵活结构以及一种建立 RRG的简化方法。我们对 VPR进行了改进,扩展了其功能,使得它可以处理包含嵌入式存储器的 FPGA结构,同时保持了原有的灵活性。

纵观整个工作,我们着重处理包含嵌入式存储器模块的 FPGA结构,我们假设存储器模块按列排放。我们的这种结构不仅适用于存储器模块,同时也适用于其他的按列排放的功能模块,例如 Spartan-3系列 FPGA中的乘法器模块以及 Stratix系列 FPGA中的 DSP模块。

本文作者创新观点:本文中,我们提出了一种灵活的包含嵌入式存储器的 FPGA结构以及一种建立 RRG的简化方法。我们对 VPR进行了改进,扩展了其功能,使得它可以处理包含嵌入式存储器的 FPGA结构,同时保持了原有的灵活性。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。