近年来,随着微控制器的发展,各类工业控制产品对现代数字控制器的需求也越来越大。微控制器是将微型计算机的主要部分集成在一个芯片上的单芯片微型计算机。微控制器诞生于20世纪70年代中期,经过20多年的发展,其成本越来越低,而性能越来越强大,这使其应用已经无处不在,遍及各个领域。例如电机控制、条码阅读器/扫描器、消费类电子、游戏设备、电话、HVAC、楼宇安全与门禁控制、工业控制与自动化和白色家电(洗衣机、微波炉)等。微控制器(Microcontroller Unit,即MCU)可从不同方面进行分类:根据数据总线宽度可分为8位、16位和32位机;根据存储器结构可分为Harvard结构和Von Neumann结构;根据内嵌程序存储器的类别可分为OTP、掩膜、EPROM/EEPROM和闪存Flash;根据指令结构又可分为CISC(Complex Instruction Set Computer)和RISC(Reduced Instruction Set Computer)微控制器。

1 浮点DSP TMS320C6713简介

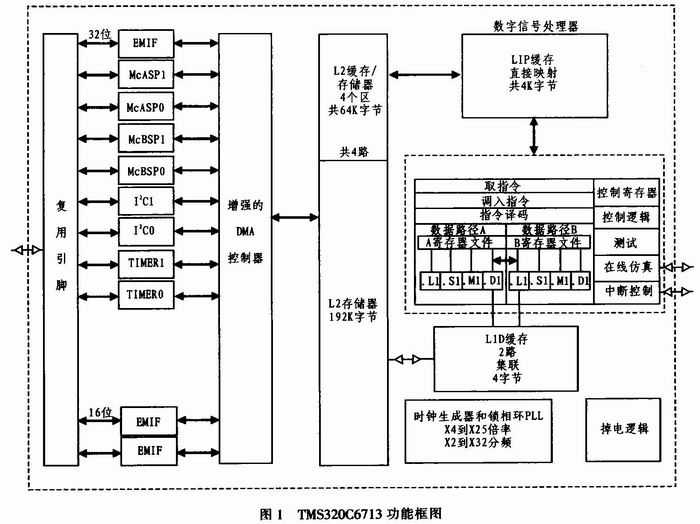

TMS320C6713 DSP是美国TI于1997年推出的C6000系列DSP芯片的一款,它是32位高速浮点型DSP,时钟频率为300MHz。TMS320C6713主要特点有:(1)体系结构采用超长指令字(VLIW)结构,单指令字长为32位,指令包里有8个指令,总字长达到256位。执行指令的功能单元已经在编译时分配好,程序运行时通过专门的指令分配模块,可以将每个256位的指令包同时分配到8个处理单元,并由8个单元同时运行。其处理能力可以达到2400MIPS。(2)采用二级缓冲处理,4KByte直接匹配的程序缓冲L1P,4KByte可匹配的数据缓冲L1D,256KByteL2额外匹配内存。32位外部存储器接口,可无缝连接SRAM、EPROM、Flash、SBSRAM和SDRAM。(3)丰富的外设,包括DMA,EDMA,支持无需CPU参与可以在允许的地址空间里传送数据,扩展总线,具有主机口和I/O端口操作等功能,多通道缓冲串口,其通过配置能和多种串行通信接口通信,两个32位通用定时器等。

CPU中包含8个功能单元,可以并行操作;有两组寄存器,每组寄存器由16个32位寄存器组成。片内程序存储器的总线宽度为256 bit,每个周期可取8条32位指令。TMS320C6713功能框图如图1所示。

从总体上归纳一下,TMS320C6713具有以下特点:

1)高性能浮点DSP,主频高达200 MHz,运算速度可达1600 MIPS;

2)超长指令字(VLIW)DSP核:8个独立功能单元(6个累加器和2个乘法器),32个32 bit的通用寄存器的存储装载结构,可以大大缩减代码的指令包;

3)L1/L2存储器结构:4 KB L1P程序缓存,4 KB L1D数据缓存:256 KB L2内存:其中64 K字节可配置成缓存或存储器,192 K字节统一映像内存,可以灵活地定位为程序/数据空间;

4)32位外部存储器接口(EMIF):可配置异步存储器接口,扩展SRAM和E2PROM;可配置同步存储器接口,可扩展SDRAM和SBSRAM;可寻址512 MB外存空间;

5)16位的HPI接口,可访问CPU的任意可寻址空间;

6)2个多通道缓存串口(McBSP);

7)2个I2C总线主/从模式接口;

8)内置灵活的PLL锁相时钟电路;

9)支持1EEE-1149.1(JTAG)边界扫描接口;10)16路GPIO接口。

2 EMIF简介

外部存储器接口(EMIF),External Memory Interface,是TMS DSP器件上的一种接口。一般来说,EMIF可实现DSP与不同类型存储器(SRAM、Flash RAM、DDR-RAM等)的连接。一般EMIF与FPGA相连,从而使FPGA平台充当一个协同处理器、高速数据处理器或高速数据传输接口。设计接口提供了一个FPGA块至RAM的无缝连接。在读/写、FIFO或存储器模式中,双端口块RAM的一侧被用来实现与DSP的通信。另一侧用于实现与内部FPGA逻辑电路或平台-FPGA嵌入式处理器的通信。在使用DSP的过程中,需要设计外部存储器接口时可以参考TI的TMS320XX DSP External Memory Interface (EMIF) Reference Guide。其中XX代表某一种具体的dsp处理器。

TMS320C6000的EMIF接口,即外部存储器接口(The External Memory Interface),支持各种外部器件的无缝接口。

简单来说,EMIF接口就相当于一个可配置的总线接口,其接口上面的信号线基本囊括了各种存储器(SRAM、Flash RAM、DDR-RAM等)的读写接口信号。通过软件配置相应的寄存器,可以使EMIF接口工作于和设计中使用的外部存储器相匹配的固定的接口形式。

下面就本次设计使用的TMS320C6713为例详细介绍一下EMIF。TMS320C6713的EMIF可以通过下面两种请求器处理外部总线请求:片内加强型直接存储器存取EDMA控制器;外部共享存储器的设备控制器。

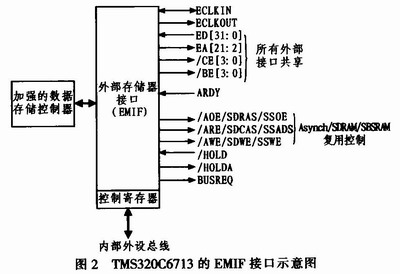

图2是TMS320C6713的EMIF接口信号示意图。

图2中,ECLKIN信号是系统提供的一个外部时钟源。ECLKOUT信号是由内部产生(基于ECLKIN),所有与本控制器EMIF接口对接的存储器必须工作在ECLKOUT下。SBSRAM接口、SDRAM接口和异步接口的信号合并复用。这里的CE1片选空间支持所有的3种存储器接口。

表1列出TMS320C6713的EMIF存储器映射寄存器。通过设置这些寄存器,既可以将EMIF配置成为不同类型、不同位宽的总线接口,又可以配置总线读写时序的速度。由于EMIF接口的这一优势,设计者使用集成EMIF接口的控制芯片时,无论是扩展外部存储设备,还是利用EMIF接口进行外部设备的读取,其难度都大大降低。

3 硬件电路设计与实现

3.1 需求分析

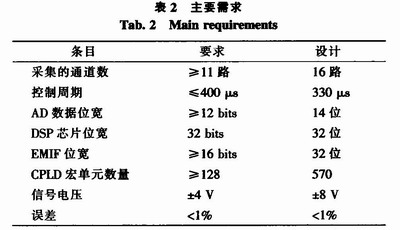

本设计硬件任务主要是完成对主电路的电压、电流的采集,具体的要求如表2所示。

3.2 硬件设计

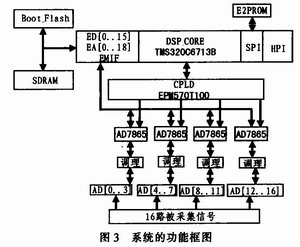

图3所示是TMS320C6713外围的主要的功能框图。

如图3所示,本设计的外围器件主要包括:双口RAM,用于与定点核DSP芯片(如TMS320F2812)交换数据;Boot Flash,当程序的大小大于192 KB,用于存储启动程序;SDRAM,用作运行部分程序的存储介质;CPLD,用于逻辑扩展;AD7865,用于采集电压电流的实时数据。

AD7865是一种高速、低功耗、四通道同步采样的14位A/D转换芯片,该芯片内部有1个2.4μs的逐次逼近型A/D转换器,4个跟踪/保持放大器,内部2.5V参考电压,同时片上还集成有时钟振荡器和1个高速并行接口。AD7865可大大简化硬件电路设计。AD574转换时间为25μs,而AD7865完成四通道信号的同时转换,则只需要100 μs。 AD7865内部4个采样通道的输入信号是同步采样的,只需发送1个脉冲的采样启动信号,芯片将自动完成采样、逼近和存储数据到片内特定寄存器等工作,单路采样速率350 KSPS,四路同时采集时100 kHz。

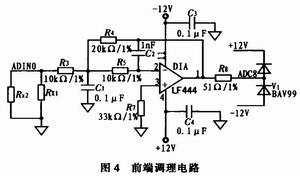

根据设计需求可设定调理电路放大倍数为2倍(反相放大),则实际值与A/D的采样值之间的关系可由式(1)表示。

实际值=采样值/213x10/(-2)×传感器系数 (1)

若采样值为正数时可用式(1),否则需先进行求补处理。

AD7865的前端调理电路如图4所示。

AD7865的外围连接电路如图5所示。

TMS320C6713的EMIF接口各信号线可以根据EMIF接口的示意图(图2)连接。在这里需要注意的是各信号线的上拉、下拉和信号线上的限流等措施。可按照如下原则设计:1)地址线和数据线以及控制线出口处可以串联33 Ω的电阻,以达到限流的效果;2)对于某些敏感信号在默认状态下的电平,应该通过上拉和下拉进行确定。一般情况下,上拉电阻用10 kΩ的电阻,下拉电阻用1 kΩ的电阻。

CPLD的主要功能主要是实现逻辑扩展,在本设计中,CPLD的主要工作是在DSP6713和多片AD7865芯片之间进行信号的解析和传递。选用的CPLD芯片是ALTERA公司的EPM570,该芯片相较于其他同类型的CPLD而言,配置简单、存储容量大而价格较低廉。其外围电路比较简单,可以参考ALTERA公司关于该芯片的引脚功能表,在此不做赘述。

4 软件实现与部分流程图

4.1 EMIF接口的配置实现

TMS320C6713要实现EMIF接口数据读取的首要条件是正确配置EMIF接口的寄存器,以达到设计的要求。

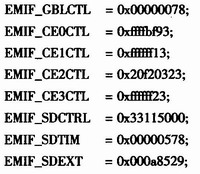

本设计将CE3作为外部AD的寻址空间,因此在这里主要需要配置的EMIF寄存器主要是全局控制寄存器GBLCTL和CE3空间控制寄存器。当然,要正确地配置EMIF接口,必须要正确配置TMS320C6713的锁相环(PLL)寄存器,在此处不具体说明。本设计中具体主要寄存器配置的几个参数如下:

本设计中采用的EMIF接口方式为32位异步接口(MTYPE=0010b)。虽然AD7865是14位MD转换器,配置为16位宽的接口方式也可以了,但是实际上,由于内部数据处理时为了计算方便而采用了32位的数据,数据位宽通常为32位,在进行外部读取时,如果采用16位宽度,那么读取总线为了匹配数据长度,将要发送连续读取两次的读信号,这在一定程度上虽然加快了A/D读取的速度。

4.2 实现A/D转换和读取数据

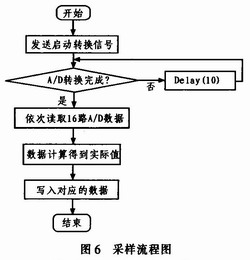

实际使用中,AD7865启动转换只需要给出片选和ADCONV信号。而它的读取方式有两种:

1)转换过程中读取数据,即转换一路读取一路;

2)所有通道的信号均转换完成后再顺序读取各通道数据。

两种读取方式的主要区别是:第1种读取速度较快,但是时序要求较高,硬件连接复杂,增加软硬件设计的难度;而第2种读取速度相对较慢,但是时序要求不高,软硬件设计也相对简单。考虑到系统的可靠性,同时CPLD完成时序的能力较差,CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

实际采用的A/D转换和读取的主要流程如图6所示。

5 测量结果

本文完成辅助控制器的设计后,对软硬件进行测试。

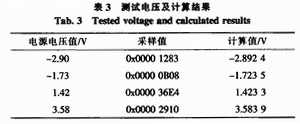

主要采用直流电源进行测试,测试分为正向电压、反向电压(即认为传感器系数为1)。测试结果见表3。由表可知测试结果的误差小于1%,完全符合设计要求。

6 结束语

由测量数据和控制器的计算结果可知,本设计完成了基于EMIF接口的数据采集系统的设计任务。由系统采集得到的数据误差较小,可以满足各类工程的需求。通过在线调试。可看到在实际采样过程中,采样数据是在一个值附近波动,在某些对于数据的实时度需求不是很高,而对数据的度需求较高的场合,可通过求取某一段较短时间内的采样平均值的方法来提高数据的。而且,由于控制器选用性能较高的TMS320C6000系列DSP,其性能和资源还有很大的可利用率。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。