0 引言

随着科技的不断的发展,对集成电路的要求越来越高。FPGA/CPLD也被大量的应用。它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器件。与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

QuartusⅡ是Altera公司在21世纪初推出的FPGA/CPLD集成开发环境,是Altera公司前一代FPGA/CPLD集成开发环境Max+PlusⅡ的更新换代产品,其界面友好,使用便捷,功能强大,为设计者提供了一种与结构无关的设计环境,使设计者能方便的进行设计输入、快速处理和器件编程。

本文在QuartusⅡ开发环境下,用VHDL语言设计了一种可用于控制16路彩灯,具有4种彩灯变换模式,且变换速度可调的彩灯控制器。

1 16路可调速彩灯控制嚣设计思路

16路可调逮彩灯控制器根据功能可分为3个部分,如图1所示。其中,8 Hz分频部分用于对频率为10 MHz的时钟信号进行分频,获得频率为8 Hz的时钟信号CLK8。CLK8作为速度控制部分的基准时钟,通过计数分频方式又可获得频率分别为4 Hz,2 Hz和1 Hz的时钟信号,然后由调速信号选择其中之一作为彩灯时钟信号CLKQ,CLKQ即为彩灯控制部分的基准时钟,用于决定彩灯变换的速度,由此实现调速信号SPD对彩灯变换速度的控制,使彩灯可调速。

彩灯控制部分通过输出1个16位二进制数来控制16个彩灯,每一位二进制数对应1个彩灯的开关,当该位数字为“1”时灯亮,该位数字为“O”时灯灭。彩灯的变换共设置4种模式:

sO模式:只亮1个灯,从左端逐个移动到右端,即输出信号Q从第15位开始将1个“1”依次移动到第0位;

s1模式:只亮1个灯,从右端逐个移动到左端,即输出信号Q从第0位开始将1个“1”依次移动到第15位;

s2模式:亮2个灯,同时从左右两端向中间移动,即输出信号Q从第15位开始将1个“1”依次移动到第8位,同时从第O位开始将1个“1”依次移动到第7位;

s3模式:亮2个灯,同时从中间向左右两端移动,即输出信号Q从第8位开始将1个“1”依次移动到第15位,同时从第7位开始将1个“1”依次移动到第0位。

四种模式依次循环,若复位信号RST输入为高电平,则循环中断,输出信号Q置零,彩灯全灭,RST恢复为低电平后,再次从sO模式开始循环。

2 16路可调速彩灯控制器的实现

本文所设计的16路可调速彩灯控制器,其电路符号如图2所示,其中clk为10 MHz时钟信号输入端,rst为复位控制端,spd为调速信号输入端,q为彩灯控制信号输出端。

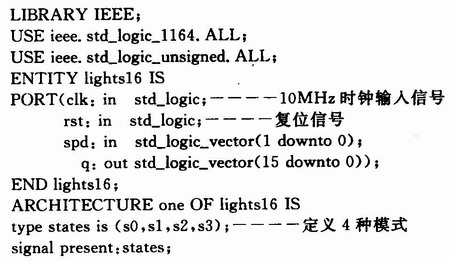

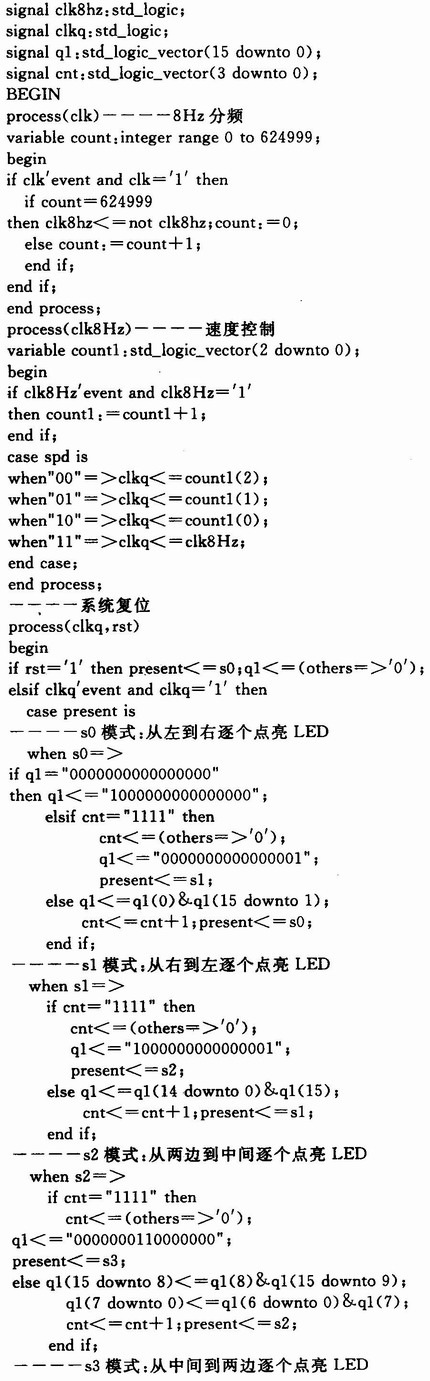

本文所设计的16路可调速彩灯控制器的VHDL代码如下所示:

值得注意的是,本文设计的16路可调速彩灯控制器使用了数据循环算法,较以往的case when语句,更加简洁,实现的功能更加强大,其具有如下特点:

(1)在硬件验证时,将速度控制端spd的pin脚接到拨码开关上,从而实现彩灯变换速度快慢的手动控制,在更进一步的设计中,也可以通过对spd信号的内部控制,实现各种变换速度的自动调整。

(2)该设计采用数据移位的方式实现彩灯的变换,更有利于彩灯变换模式的扩展。该设计虽然只设计了4种变换模式,但可以根据需要轻松的扩展至6~8种模式,甚至更多。

(3)8 Hz分频部分的分频比很大,不适于计算机仿真验证,在仿真时需要调小分频比,在硬件验证时再恢复较大的分频比。

3 仿真结果分析

本文设计的16路可调速彩灯控制器在QuartusⅡ开发环境下进行了仿真验证,仿真波形如图3所示。仿真结果分析如下:

(1)clk为时钟信号,由时钟信号的上升沿触发分频器计数;

(2)rst为复位信号输入端,当其为高电平时,彩灯控制输出信号q清零,rst恢复为低电平后彩灯控制输出信号q从sO模式重新开始循环;

(3)spd为调速信号输入端,对应于spd的“00”,“01”,“10”,“11”这4个数值,彩灯变换的速度分别为1 Hz,2 Hz,4 Hz,8 Hz;

(4)q为彩灯控制信号输出端,由图3可知,该设计成功地实现了4种变换模式的循环和各种变换速度的调节。

4 结语

设计的16路可调速彩灯控制器在QuartusⅡ开发环境下进行了仿真验证后,到湖北众友科技实业股份有限公司的ZYllEDAl3BE实验箱中进行了硬件验证,该实验箱使用ACEXlK系列EPlK30QC208芯片作为芯片,实验证明设计正确,功能完整,运行稳定。另外,本文所设计的16路可调速彩灯控制器可根据需要增加更多的变换模式,使彩灯更加绚丽多姿。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。